**PRELIMINARY**

## NS32381-15/NS32381-20/NS32381-25/NS32381-30 Floating-Point Unit

#### **General Description**

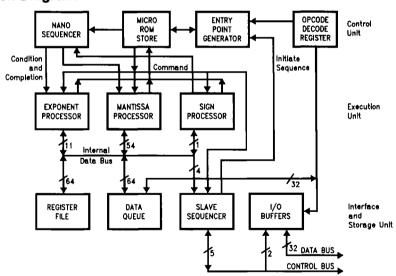

The NS32381 is a second generation, CMOS, floating-point slave processor that is fully software compatible with its forerunner, the NS32081 FPU. The NS32381 FPU functions with National's Embedded System Processors™, the NS32GX32 and the NS32CG16, and with any Series 32000 CPU, from the NS32008 to the NS32532, in a tightly coupled slave configuration. The performance of the NS32381 has been increased over the NS32081 by architecture improvements, hardware enhancements, and higher clock frequencies. Key improvements include the addition of a 32-bit slave protocol, an early done algorithm to increase CPU/FPU parallelism, an expanded register set, an automatic power down feature, expanded math hardware, and additional instructions.

The NS32381 FPU contains eight 64-bit data registers and a Floating-Point Status Register (FSR). The FPU executes 20 instructions, and operates on both single and double-precision operands. Three separate processors in the NS32381 manipulate the mantissa, sign, and exponent.

The CPU and NS32381 FPU form a tightly coupled computer cluster, which appears to the user as a single processing unit. The CPU and FPU communication is handled automatically, and is user transparent.

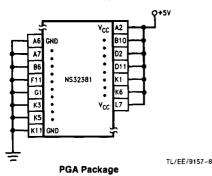

The FPU is fabricated with National's advanced double-metal CMOS process. It is available in a 68-pin Pin Grid Array (PGA) package or 68-pin Plastic package.

#### **Features**

- Compatible with NS32008, NS32016, NS32C016, NS32032, NS32C032, NS32332, NS32532, NS32CG16 and NS32GX32 microprocessors

- Selectable 16-bit or 32-bit Slave Protocol

- Format compatible with IEEE Standard 754-1985 for binary floating point arithmetic

- Early done algorithm

- Single (32-bit) and double (64-bit) precision operations

- Eight on-chip (64-bit) data registers

- Automatic power down mode

- Full upward compatibility with existing 32000 software

- High speed double-metal CMOS design

- 68-pin PGA package

- 68-pin plastic package

#### **FPU Block Diagram**

FIGURE 1-1

#### **Table of Contents**

#### 1.0 PRODUCT INTRODUCTION

- 1.1 IEEE Features Supported-Standard 754-1985

- 1.2 Operand Formats

- 1.2.1 Normalized Numbers

- 1.2.2.7ero

- 1.2.3 Reserved Operands

- 1.2.4 Integers

- 1.2.5 Memory Representations

#### 2.0 ARCHITECTURAL DESCRIPTION

- 2.1 Programming Model

- 2.1.1 Floating-Point Registers

- 2.1.2 Floating-Point Status Register (FSR)

- 2.1.2.1 FSR Mode Control Fields

- 2.1.2.2 FSR Status Fields

- 2.1.2.3 FSR Software Fields (SWF)

- 2.2 Instruction Set

- 2.3 Exceptions

#### 3.0 FUNCTIONAL DESCRIPTION

- 3.1 Power and Grounding

- 3.2 Automatic Power Down Mode

- 3.3 Clocking

- 3.4 Resetting

- 3.5 Bus Operation

- 3.5.1 Bus Cycles

- 3.5.2 Operand Transfer Sequences

- 3.6 Instruction Protocols

- 3.6.1 General Protocol Sequence

- 3.6.2 Early Done Algorithm

- 3.6.3 Floating-Point Protocols

#### 4.0 DEVICE SPECIFICATIONS

- 4.1 Pin Descriptions

- 4.1.1 Supplies

- 4.1.2 Input Signals

- 4.1.3 Output Signals

- 4.1.4 Input/Output Signals

- 4.2 Absolute Maximum Ratings

4.3 Electrical Characteristics

- 4.4 Switching Characteristics

- 4.4.1 Definitions

- 4.4.2 Timing Tables

- 4.4.2.1 Output Signal Propagation Delays for all CPUs

- 4.4.2.2 Output Signal Propagation Delays for the NS32008, NS32016, NS32032 CPUs

- 4.4.2.3 Output Signal Propagation Delays for the 32-Bit Slave Protocol NS32332 CPU

- 4.4.2.4 Output Signal Propagation Delays for the 32-Bit Slave Protocol NS32532 CPU

- 4.4.2.5 Input Signal Requirements for all CPUs

- 4.4.2.6 Input Signal Requirements for the NS32008, NS32016, NS32032 CPUs

- 4.4.2.7 Input Signal Requirements for the 32-Bit Stave Protocol NS32332 CPU

- 4.4.2.8 Input Signal Requirements for the 32-Bit Slave Protocol NS32532 CPU

- 4.4.2.9 Clocking Requirements for all CPUs

#### **APPENDIX A: NS32381 PERFORMANCE ANALYSIS**

#### List of Illustrations

| FPU Block Diagram                                                        |

|--------------------------------------------------------------------------|

| Floating-Point Operand Formats                                           |

| Integer Format                                                           |

| Register Set                                                             |

| The Floating-Point Status Register                                       |

| Floating-Point Instruction Formats                                       |

| Recommended Supply Connections                                           |

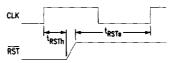

| Power-On Reset Requirements                                              |

| General Reset Timing                                                     |

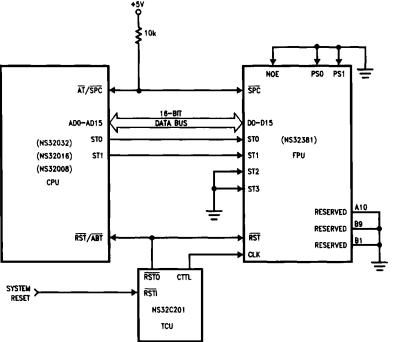

| System Connection Diagram with the NS32532 CPU                           |

| System Connection Diagram with the NS32332 CPU                           |

| System Connection Diagram with the NS32008, NS32016 or NS32032 CPU       |

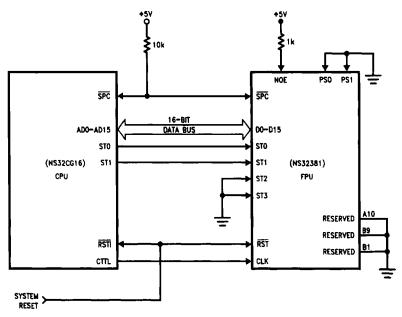

| System Connection Diagram with the NS32CG16 CPU                          |

| Slave Processor Read Cycle (NS32008, NS32016, NS32032 and NS32332 CPUs)  |

| Slave Processor Read Cycle (NS32532 CPU)                                 |

| Slave Processor Write Cycle (NS32008, NS32016, NS32032 and NS32332 CPUs) |

| Slave Processor Write Cycle (NS32532 CPU)                                |

| ID and Opcode Format 16-Bit Slave Protocol                               |

| ID and Opcode Format 32-Bit Slave Protocol                               |

| FPU Status Word Format                                                   |

| 16-Bit General Slave Instruction Protocol: FPU Actions                   |

| 32-Bit General Slave Instruction Protocol: FPU Actions                   |

| 68-Pin PGA Package4-1                                                    |

| Timing Specification Standard (Signal Valid After Clock Edge)            |

| Timing Specification Standard (Signal Valid Before Clock Edge)           |

| Clock Timing         4-4                                                 |

| Power-On Reset                                                           |

| Non-Power-On Reset                                                       |

| RST Release Timing4-7                                                    |

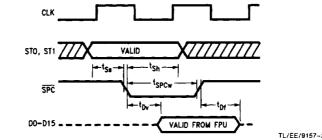

| Read Cycle from FPU (NS32008, NS32016, NS32032 CPUs)                     |

| Write Cycle to FPU (NS32008, NS32016, NS32032 CPUs)4-9                   |

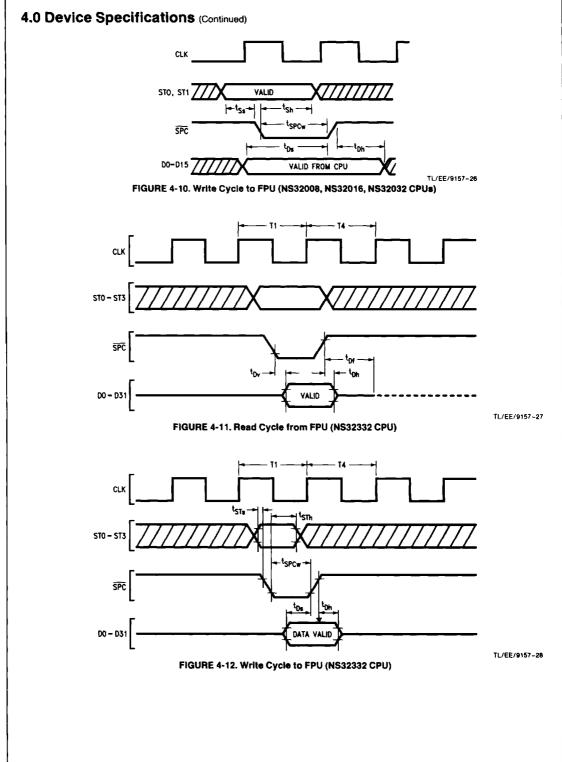

| Read Cycle from FPU (NS32332 CPU)                                        |

| Write Cycle to FPU (NS32332 CPU)4-11                                     |

| <u>\$DN332</u> Timing (NS32332 CPU)4-12                                  |

| \$DN332 (TRAP) Timing (NS32332 CPU)                                      |

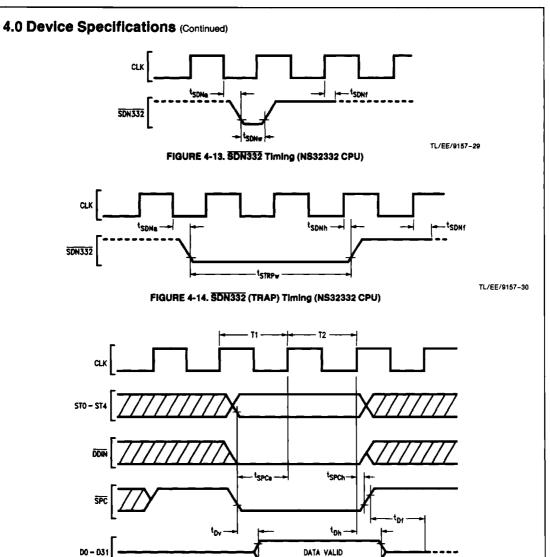

| Read Cycle from FPU (NS32532 CPU)                                        |

| Write Cycle from FPU (NS32532 CPU)                                       |

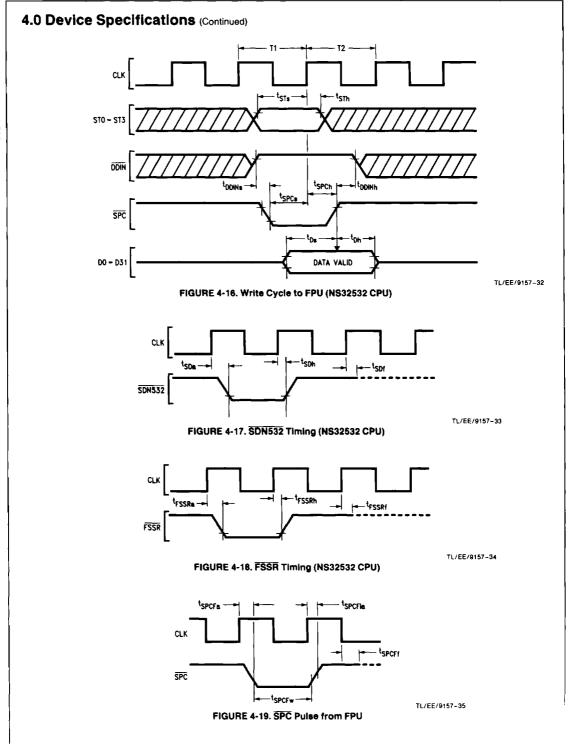

| <u>\$DN532</u> Timing (NS32532 CPU)4-16                                  |

| FSSR Timing (NS32532 CPU)                                                |

| SPC Pulse from FPU                                                       |

## List of Tables Sample F Fields 1-1 Sample E Fields 1-2 Normalized Number Ranges 1-3 16-Bit General Slave Instruction Protocol 3-1 32-Bit General Slave Instruction Protocol 3-2 Floating-Point Instruction Protocols 3-3

#### 1.0 Product Introduction

The NS32381 Floating-Point Unit (FPU) provides high speed floating-point operations for the Series 32000 family, and is fabricated using National high-speed CMOS technology. It operates as a slave processor for transparent expansion of the Series 32000 CPU's basic instruction set. The FPU can also be used with other microprocessors as a peripheral device by using additional TTL and CMOS interface logic. The NS32381 is compatible with the IEEE Floating-Point Formats.

#### 1.1 IEEE FEATURES SUPPORTED-STANDARD 754-1985

- a) Basic floating-point number formats

- b) Add, subtract, multiply, divide and compare operations

- c) Conversions between different floating-point formats

- d) Conversions between floating-point and integer formats

- e) Round floating-point number to integer (round to nearest, round toward negative infinity and round toward zero, in double or single-precision)

- f) Exception signaling and handling (invalid operation, divide by zero, overflow, underflow and inexact)

#### 1.2 OPERAND FORMATS

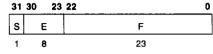

The N32381 FPU operates on two floating-point data types—single precision (32 bits) and double precision (64 bits). Floating-point instruction mnemonics use the suffix F (Floating) to select the single precision data type, and the suffix L (Long Floating) to select the double precision data type.

A floating-point number is divided into three fields, as shown in *Figure 1-2*.

The F field is the fractional portion of the represented number. In Normalized numbers (Section 1.2.1), the binary point is assumed to be immediately to the left of the most significant bit of the F field, with an implied 1 bit to the left of the binary point. Thus, the F field represents values in the range  $1.0 \le x < 2.0$ .

TABLE 1-1. Sample F Fields

|         | •            |               |

|---------|--------------|---------------|

| F Field | Binary Value | Decimal Value |

| 000 0   | 1.000 0      | 1.000 0       |

| 010 0   | 1.010 0      | 1.250 0       |

| 100 0   | 1.100 0      | 1.500 0       |

| 110 0   | 1.110 0      | 1.750 0       |

|         | 1            |               |

Implied Bit

The E field contains an unsigned number that gives the binary exponent of the represented number. The value in the E field is biased; that is, a constant bias value must be subtracted from the E field value in order to obtain the true

exponent. The bias value is 011...11<sub>2</sub>, which is either 127 (single precision) or 1023 (double precision). Thus, the true exponent can be either positive or negative, as shown in Table 1.2

TABLE 1-2. Sample E Fields

| E Field | F Field | Represented Value          |  |  |

|---------|---------|----------------------------|--|--|

| 011 110 | 100 0   | $1.5 \times 2^{-1} = 0.75$ |  |  |

| 011 111 | 100 0   | $1.5 \times 2^0 = 1.50$    |  |  |

| 100 000 | 100 0   | $1.5 \times 21 = 3.00$     |  |  |

Two values of the E field are not exponents. 11...11 signals a reserved operand (Section 1.2.3). 00...00 represents the number zero if the F field is also all zeroes, otherwise it signals a reserved operand.

The S bit indicates the sign of the operand. It is 0 for positive and 1 for negative. Floating-point numbers are in sign-magnitude form, that is, only the S bit is complemented in order to change the sign of the represented number.

#### 1.2.1 Normalized Numbers

Normalized numbers are numbers which can be expressed as floating-point operands, as described above, where the E field is neither all zeroes nor all ones.

The value of a Normalized number can be derived by the formula:

$$(-1)^S \times 2^{(E-Bias)} \times (1 + F)$$

The range of Normalized numbers is given in Table 1-3.

#### 1.2.2 Zero

There are two representations for zero—positive and negative. Positive zero has all-zero F and E fields, and the S bit is zero. Negative zero also has all-zero F and E fields, but its S bit is one.

#### 1.2.3 Reserved Operands

The IEEE Standard for Binary Floating-Point Arithmetic provides for certain exceptional forms of floating-point operands. The NS32381 FPU treats these forms as reserved operands. The reserved operands are:

- · Positive and negative infinity

- Not-a-Number (NaN) values

- Denormalized numbers

Both Infinity and NaN values have all ones in their E fields. Denormalized numbers have all zeroes in their E fields and non-zero values in their F fields.

The NS32381 FPU causes an Invalid Operation trap (Section 2.1.2.2) if it receives a reserved operand, unless the operation is simply a move (without conversion). The FPU does not generate reserved operands as results.

#### Single Precision

#### **Double Precision**

FIGURE 1-2. Floating-Point Operand Formats

#### 1.0 Product Introduction (Continued)

**TABLE 1-3. Normalized Number Ranges**

| Most Positive  | Single Precision<br>$2^{127} \times (2 - 2^{-23})$<br>= $3.40282346 \times 10^{38}$ | Double Precision $2^{1023} \times (2 - 2^{-52})$ = 1.7976931348623157 $\times$ 10 <sup>308</sup> |

|----------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Least Positive | $2^{-126}$ = 1.17549436 × 10 <sup>-38</sup>                                         | $2^{-1022}$ = 2.2250738585072014 × 10 <sup>-308</sup>                                            |

| Least Negative | $-(2^{-126})$<br>= $-1.17549436 \times 10^{-38}$                                    | $-(2^{-1022})$ = -2.2250738585072014 × 10 <sup>-308</sup>                                        |

| Most Negative  | $-2^{127} \times (2 - 2^{-23})$<br>= $-3.40282346 \times 10^{38}$                   | $-2^{1023} \times (2 - 2^{-52})$<br>= -1.7976931348623157 × 10 <sup>308</sup>                    |

Note: The values given are extended one full digit beyond their represented accuracy to help in generating rounding and conversion algorithms.

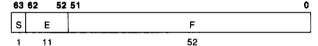

#### 1.2.4 Integers

In addition to performing floating-point arithmetic, the NS3281 FPU performs conversions between integer and floating-point data types. Integers are accepted or generated by the FPU as two's complement values of byte (8 bits), word (16 bits) or double word (32 bits) length.

See Figure 1-3 for the Integer Format and Table 1-4 for the Integer Fields.

TABLE 1-4. Integer Fields

| S | Value | Name             |

|---|-------|------------------|

| 0 | 1     | Positive Integer |

| 1 | 1 2n  | Negative Integer |

Note: n represents the number of bits in the word, 8 for byte, 16 for word and 32 for double-word.

#### 1.2.5 Memory Representations

The NS32381 FPU does not directly access memory. However, it is cooperatively involved in the execution of a set of two-address instructions with its Series 32000 Family CPU. The CPU determines the representation of operands in memory.

In the Series 32000 family of CPUs, operands are stored in memory with the least significant byte at the lowest byte

address. The only exception to this rule is the Immediate addressing mode, where the operand is held (within the instruction format) with the most significant byte at the lowest address.

#### 2.0 Architectural Description

#### 2.1 PROGRAMMING MODEL

The Series 32000 architecture includes nine registers that are implemented on the NS32381 Floating-Point Unit (FPU).

#### 2.1.1 Floating-Point Registers

There are eight registers (L0-L7) on the NS32381 FPU for providing high-speed access to floating-point operands. Each is 64 bits long. A floating-point register is referenced whenever a floating-point instruction uses the Register addressing mode (Section 2.2.2) for a floating-point operand. All other Register mode usages (i.e., integer operands) refer to the General Purpose Registers (R0-R7) of the CPU, and the FPU transfers the operand as if it were in memory.

Note: These registers are all upward compatible with the 32-bit NS32081 registers, (F0-F7), such that when the Register addressing mode is specified for a double precision (64-bit) operand, a pair of 32-bit registers holds the operand. The programmer specifies the even register of the pair which contains the least significant half of the operand and the next consecutive register contains the most significant half.

#### 2.1.2 Floating-Point Status Register (FSR)

The Floating-Point Status Register (FSR) selects operating modes and records any exceptional conditions encountered during execution of a floating-point operation. *Figure 2-2* shows the format of the FSR.

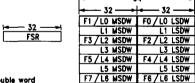

L7 LSDW

L7 MSDW

LSDW → least significant double word MSDW → most significant double word

TL/EE/9157-36

FIGURE 2-1. Register Set

| 31      | 17 | 16  | 15 |   |    |       |   | 9 | 8 | 7 | 6  | 5   | 4  | 3   | 2 | 1 | 0_ |

|---------|----|-----|----|---|----|-------|---|---|---|---|----|-----|----|-----|---|---|----|

| Reserve | eď | RMB |    | 1 | SW | <br>F | 1 |   | R | M | IF | IEN | UF | UEN |   | Π |    |

FIGURE 2-2. The Floating-Point Status Register

#### 3

#### 2.0 Architectural Description (Continued)

#### 2.1.2.1 FSR Mode Control Fields

The FSR mode control fields select FPU operation modes. The meanings of the FSR mode control bits are given below.

Rounding Mode (RM): Bits 7 and 8. This field selects the rounding method. Floating-point results are rounded whenever they cannot be exactly represented. The rounding modes are:

- On Round to nearest value. The value which is nearest to the exact result is returned. If the result is exactly halfway between the two nearest values the even value (LSB=0) is returned.

- 01 Round toward zero. The nearest value which is closer to zero or equal to the exact result is returned.

- 10 Round toward positive infinity. The nearest value which is greater than or equal to the exact result is returned.

- 11 Round toward negative infinity. The nearest value which is less than or equal to the exact result is returned.

Underflow Trap Enable (UEN): Bit 3. If this bit is set, the FPU requests a trap whenever a result is too small in absolute value to be represented as a normalized number. If it is not set, any underflow condition returns a result of exactly zero.

Inexact Result Trap Enable (IEN): Bit 5. If this bit is set, the FPU requests a trap whenever the result of an operation cannot be represented exactly in the operand format of the destination. If it is not set, the result is rounded according to the selected rounding mode.

#### 2.1.2.2 FSR Status Fields

The FSR Status Fields record exceptional conditions encountered during floating-point data processing. The meanings of the FSR status bits are given below:

Trap Type (TT): bits 0-2. This 3-bit field records any exceptional condition detected by a floating-point instruction. The TT field is loaded with zero whenever any floating-point instruction except LFSR or SFSR completes without encountering an exceptional condition. It is also set to zero by a hardware reset or by writing zero into it with the Load FSR (LFSR) instruction. Underflow and Inexact Result are always reported in the TT field, regardless of the settings of the UEN and IEN bits.

- 000 No exceptional condition occurred.

- 001 Underflow. A non-zero floating-point result is too small in magnitude to be represented as a normalized floating-point number in the format of the destination operand. This condition is always reported in the TT field and UF bit, but causes a trap only if the UEN bit is set. If the UEN bit is not set, a result of Positive Zero is produced, and no trap occurs.

- 010 Overflow. A result (either floating-point or integer) of a floating-point instruction is too great in magnitude to be held in the format of the destination operand. Note that rounding, as well as calculations, can cause this condition.

- 011 Divide by zero. An attempt has been made to divide a non-zero floating-point number by zero. Dividing zero by zero is considered an Invalid Operation instead (below).

- 100 Illegal Instruction. Any instruction forms not included in the NS32381 Instruction Set are detected by the FPU as being illegal.

- 101 Invalid Operation. One of the floating-point operands of a floating-point instruction is a Reserved operand, or an attempt has been made to divide zero by zero using the DIVf instruction.

- 110 Inexact Result. The result (either floating-point or integer) of a floating-point instruction cannot be represented exactly in the format of the destination operand, and a rounding step must alter it to fit. This condition is always reported in the TT field and IF bit unless any other exceptional condition has occurred in the same instruction. In this case, the TT field always contains the code for the other exception and the IF bit is not altered. A trap is caused by this condition only if the IEN bit is set; otherwise the result is rounded and delivered, and no trap occurs.

#### 111 (Reserved for future use.)

Underflow Flag (UF): Bit 4. This bit is set by the FPU whenever a result is too small in absolute value to be represented as a normalized number. Its function is not affected by the state of the UEN bit. The UF bit is cleared only by writing a zero into it with the Load FSR instruction or by a hardware reset.

Inexact Result Flag (IF): Bit 6. This bit is set by the FPU whenever the result of an operation must be rounded to fit within the destination format. The IF bit is set only if no other error has occurred. It is cleared only by writing a zero into it with the Load FSR instruction or by a hardware reset.

Register Modify Bit (RMB): Bit 16. This bit is set by the FPU whenever writing to a floating point data register. The RMB bit is cleared only by writing a zero with the LFSR instruction or by a hardware reset. This bit can be used in context switching to determine whether the FPU registers should be saved.

#### 2.1.2.3 FSR Software Field (SWF)

Bits 9-15 of the FSR hold and display any information written to them (using the LFSR and SFSR instructions), but are not otherwise used by FPU hardware. They are reserved for use with NSC floating-point extension software.

#### 2.0 Architectural Description (Continued)

#### 2.2 INSTRUCTION SET

#### 2.2.1 Floating-Point Instruction Set

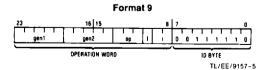

This section describes the floating-point instructions executed by the FPU in conjunction with the CPU. These instructions form a subset of the Series 32000® instruction set and take 9, 11, and 12 encoding formats. A list of all the Series 32000 instructions as well as details on their formats and addressing modes can be found in the appropriate CPU data sheets

Certain notations in the following instruction description tables serve to relate the assembly language form of each instruction to its binary format in *Figure 2-3*.

## Format 12 23 16 15 8 7 0 29 9 1 9 9 0 1 1 1 1 1 1 1 1 1 0

## FIGURE 2-3. Floating-Point Instruction Formats

TL/EE/9157-7

The Format column indicates which of the three formats in *Figure 2-9* represents each instruction.

The Op column indicates the binary pattern for the field called "op" in the applicable format.

The Instruction column gives the form of each instruction as it appears in assembly language. The form consists of an instruction mnemonic in upper case, with one or more suffixes (i or f) indicating data types, followed by a list of operands (gen1, gen2).

An i suffix on an instruction mnemonic indicates a choice of integer data types. This choice affects the binary pattern in the i field of the corresponding instruction format as follows:

| Suffix i | Data Type   | i Fleld |

|----------|-------------|---------|

| В        | Byte        | 00      |

| W        | Word        | 01      |

| D        | Double Word | 11      |

An f suffix on an instruction mnemonic indicates a choice of floating-point data types. This choice affects the setting of the f bit of the corresponding instruction format as follows:

| Suffix f | Data Type               | f Bit |

|----------|-------------------------|-------|

| F        | Single Precision        | 1     |

| L        | Double Precision (Long) | 0     |

An operand designation (gen1, gen2) indicates a choice of addressing mode expressions. This choice affects the binary pattern in the corresponding gen1 or gen2 field of the instruction format. Refer to Table 2-1 for the options available and their patterns.

Further details of the exact operations performed by each instruction are found in the Series 32000 Instruction Set Reference Manual.

#### Movement and Conversion

The following instructions move the gen1 operand to the gen2 operand, leaving the gen1 operand intact.

| Format    | Op    | Inst            | truction             | Description                                                                                                     |

|-----------|-------|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------|

| 11        | 0001  | MOVf            | gen1, gen2           | Move without conversion                                                                                         |

| 9         | 010   | MOVLF           | gen1, gen2           | Move, converting from double precision to single precision.                                                     |

| 9         | 011   | MOVFL           | gen1, gen2           | Move, converting<br>from single<br>precision to<br>double<br>precision.                                         |

| 9         | 000   | MOVif           | gen1, gen2           | Move, converting<br>from any integer<br>type to any<br>floating-point<br>type.                                  |

| 9         | 100   | ROUNDfi         | gen1, gen2           | Move, converting from floating-point to the nearest integer.                                                    |

| 9         | 101   | TRUNCfi         | gen1, gen2           | Move, converting<br>from floating-<br>point to the<br>nearest integer<br>closer to zero.                        |

| 9         | 111   | FLOORfi         | gen1, gen2           | Move, converting<br>from floating-<br>point to the<br>largest integer<br>less than or<br>equal to its<br>value. |

| Note: The | MOVLE | instruction f b | it must be 1 and the |                                                                                                                 |

Note: The MOVLF instruction f bit must be 1 and the i field must be 10.

The MOVFL instruction f bit must be 0 and the i field must be 11.

#### **Arithmetic Operations**

The following instructions perform floating-point arithmetic operations on the gen1 and gen2 operands, leaving the result in the gen2 operand.

Note: POLY and DOT use the additional third implied operand.

POLY and DOT put their result to LO/FO register and not to GEN2.

| Format | Op   | Ins  | struction  | Description              |

|--------|------|------|------------|--------------------------|

| 11     | 0000 | ADDf | gen1, gen2 | Add gen1 to gen2.        |

| 11     | 0100 | SUBf | gen1, gen2 | Subtract gen1 from gen2. |

| 11     | 1100 | MULf | gen1, gen2 | Multiply gen2 by gen1.   |

#### 2.0 Architectural Description (Continued)

|     |        |      |        |            | . <b>P</b> (                                                                              |

|-----|--------|------|--------|------------|-------------------------------------------------------------------------------------------|

|     | Format | Ор   | Inst   | ruction    | Description                                                                               |

|     | 11     | 1000 | DIVf   | gen1, gen2 | Divide gen2 by gen1.                                                                      |

|     | 11     | 0101 | NEGf   | gen1, gen2 | Move negative of gen1 to gen2.                                                            |

|     | 11     | 1101 | ABSf   | gen1, gen2 | Move absolute value of gen1 to gen2.                                                      |

| (N) | 12     | 0100 | SCALBf | gen1, gen2 | Move gen2*29en1 to<br>gen2, for integral<br>values of gen1<br>without computing<br>29en1. |

| (N) | 12     | 0101 | LOGBf  | gen1, gen2 | Move the unbiased exponent of gen1 to gen2.                                               |

| (N) | 12     | 0011 | DOTf   | gen1, gen2 | Move (gen1*gen2)<br>+ L0 to L0.(*)                                                        |

| (N) | 12     | 0010 | POLYf  | gen1, gen2 | Move (L0*gen1) +<br>gen2 to L0.(*)                                                        |

#### Notes

(N): Indicates NEW instruction.

(\*)The third impled operand used by these instructions can be either F0 or L0 depending on whether 'floating' or 'long' data type is specified in the opcode.

#### Comparison

The Compare instruction compares two floating-point values, sending the result to the CPU PSR Z and N bits for use as condition codes. See *Figure 3-11*. The Z bit is set if the gen1 and gen2 operands are equal; it is cleared otherwise. The N bit is set if the gen1 operand is greater than the gen2 operand; it is cleared otherwise. The CPU PSR L bit is unconditionally cleared. Positive and negative zero are considered equal.

| Format | Op   | Ins  | struction  | Description  |  |  |

|--------|------|------|------------|--------------|--|--|

| 11     | 0010 | CMPf | gen1, gen2 | Compare gen1 |  |  |

|        |      |      |            | to den2      |  |  |

#### Floating-Point Status Register Access

The following instructions load and store the FSR as a 32-bit integer.

| Format | Op  | instru | ction | Description |

|--------|-----|--------|-------|-------------|

| 9      | 001 | LFSR   | gen1  | Load FSR    |

| 9      | 110 | SESR   | gen2  | Store FSR   |

Note: All instructions support all of the NS32000 family data formats (for external operands) and all addressing modes are supported.

#### Rounding

The FPU supports all IEEE rounding options: Round toward nearest value or even significant if a tie. Round toward zero, Round toward positive infinity and Round toward negative infinity.

#### 2.3 EXCEPTIONS

The FPU supports five types of exceptions: Invalid operation, Division by zero, Overflow, Underflow and Inexact Result. When an exception occurs, the FPU may or may not generate a trap depending upon the bit setting in the FSR Register. The user can disable the Inexact Result and the Underflow traps. If an undefined Floating-Point instruction is passed to the FPU an Illegal Instruction trap will occur. The user can't disable trap on Illegal Instruction.

Upon detecting an exceptional condition in executing a floating-point instruction, the FPU requests a TRAP by pulsing the SPC line for one clock cycle, pulsing the SDN332 line for two and a half clock cycles and pulsing the FSSR line for one clock cycle. (The user will connect the correct lines according to the CPU being used).

In addition, the FPU sets the Q bit in the status word register. The CPU responds by reading the status word register (refer to Section 3.6.1 for its format) while applying status h'E (transferring status word) on the status lines. A trapped instruction returns no result (even if the destination is FPU register) and does not affect the CPU PSR. The FPU records exceptional cause in the trap type (TT) field of the FSR. If an illegal opcode is detected, the FPU sets the TS bit in the slave processor status word register, indicating a trap (UND).

#### 3.0 Functional Description

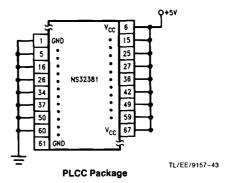

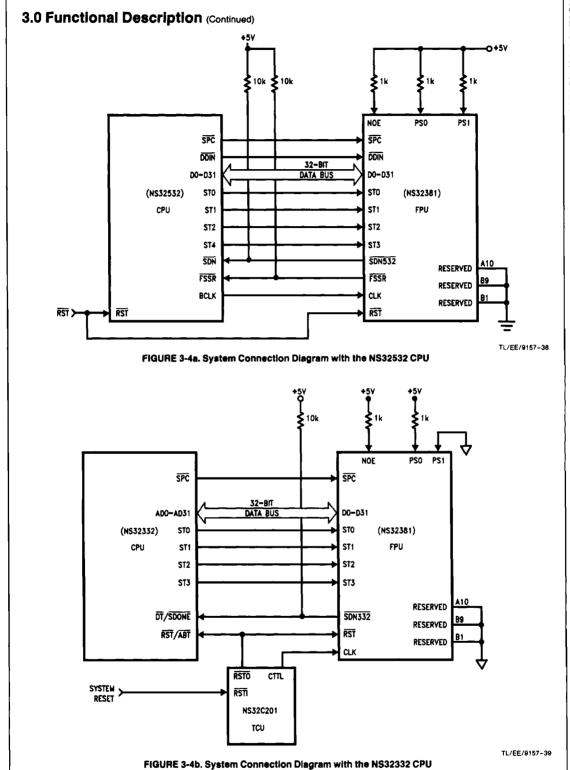

#### 3.1 POWER AND GROUNDING

The NS32381 requires a single 5V power supply, applied on the  $V_{CC}$  pins. These pins should be connected together by a power ( $V_{CC}$ ) plane on the printed circuit board. See *Figure 3-1*.

The grounding connections are made on the GND pins. These pins should be connected together by a ground (GND) plane on the printed circuit board. See *Figure 3-1*.

FIGURE 3-1. Recommended Supply Connections

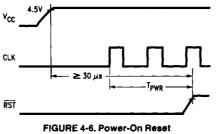

FIGURE 3-2. Power-On Reset Requirements

TL/FF/9157-9

#### 3.2 AUTOMATIC POWER DOWN MODE

The NS32381 supports a power down mode in which the device consumes only 10% of its original power at 30 MHz. The NS32381 enters the power down mode (internal clocks are stopped with phase two high) if it does not receive an SPC pulse from the CPU within 256 clocks.

The FPU exits the power down mode and returns to normal operation after it receives an SPC from the CPU. There is no extra delay caused by the FPU being in the power down mode.

#### 3.3 CLOCKING

The NS32381 FPU requires a single-phase TTL clock input on its CLK pin (pin A8). Different Clock sources can be used to provide the CLK signal depending on the application. For example, it can come from the BCLK of the NS32532 CPU. It can also come from the CTTL pin of the NS32C201 Timing Control Unit, if it is required.

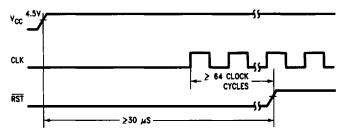

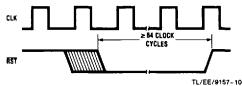

#### 3.4 RESETTING

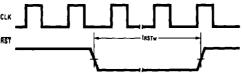

The RST pin serves as a reset for on-chip logic. The FPU may be reset at any time by pulling the RST pin low for at least 64 clock cycles. Upon detecting a reset, the FPU terminates instruction processing, resets its internal logic, and clears the FSR to all zeroes.

On application of power, RST must be held low for at least 30  $\mu$ s after V<sub>CC</sub> is stable. This ensures that all on-chip voltages are completely stable before operation. See *Figures 3-2* and *3-3*.

FIGURE 3-3, General Reset Timing

#### 3.5 BUS OPERATION

Instructions and operands are passed to the NS32381 FPU with slave processor bus cycles. Each bus cycle transfers

either one byte (8 bits), one word (16 bits) or one double word (32 bits) to or from the FPU. During all bus cycles, the SPC line is driven by the CPU as an active low data strobe, and the FPU monitors pins ST0-ST3 to keep track of the sequence (protocol) established for the instruction being executed. This is necessary in a virtual memory environment, allowing the FPU to retry an aborted instruction.

#### 3.5.1 Bus Cycles

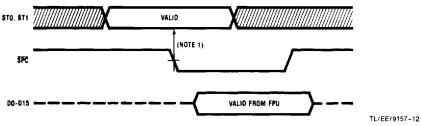

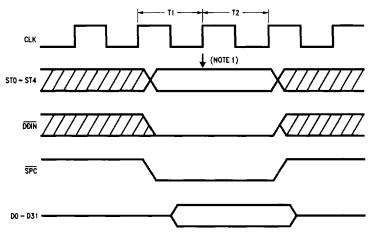

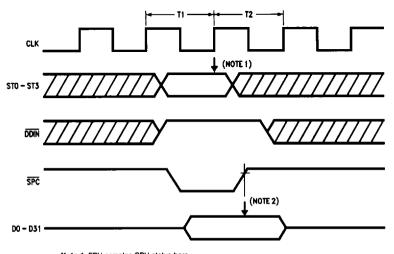

A bus cycle is initiated by the CPU, which asserts the proper status on (ST0-ST3) and pulses SPC low. The status lines are sampled by the FPU on the leading (falling) edge of the SPC pulse except for the 32532 CPU. When used with the 32532 CPU, the status lines are sampled on the rising edge of CLK in the T2 state. If the transfer is from the FPU (a slave processor read cycle), the FPU asserts data on the data bus for the duration of the SPC pulse. If the transfer is to the FPU (a slave processor write cycle), the FPU latches data from the data bus on the trailing (rising) edge of the SPC pulse. Figures 3-5, 3-6, 3-7 and 3-8 illustrate these sequences.

The direction of the transfer and the role of the bidirectional SPC line are determined by the instruction protocol being performed. SPC is always driven by the CPU during slave processor bus cycles. Protocol sequences for each instruction are given in Section 3.6.

#### 3.5.2 Operand Transfer Sequences

An operand is transferred in one or more bus cycles. For the 16-Bit Slave Protocol a 1-byte operand is transferred on the least significant byte of the data bus (D0-D7). A 2-byte operand is transferred on the entire bus. A 4-byte or 8-byte operand is transferred in consecutive bus cycles, least significant word first.

For the 32-Bit Slave Protocol a 4-byte operand is transferred on the entire data bus in a single bus cycle and an 8-byte operand is transferred in two consecutive bus cycles with the most significant byte transferred on data bits (D0–D7). The complete operand transfer of bytes B0–B7 where B0 is the least significant byte would appear on the data bus as B4, B5, B6, B7 followed by B0, B1, B2, B3 in the second bus cycle.

FIGURE 3-4c. System Connection Diagram with the NS32008, NS32016 or NS32032 CPU

TL/EE/9157~40

FIGURE 3-4d. System Connection Diagram with the NS32CG16 CPU

TL/EE/9157-13

#### 3.0 Functional Description (Continued)

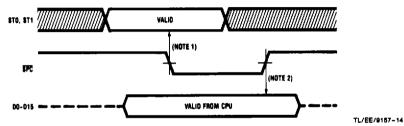

Note 1: FPU samples CPU status here.

FIGURE 3-5. Slave Processor Read Cycle (NS32008, NS32016, NS32032 and NS32332 CPUs)

Note 1: FPU samples CPU status here.

FIGURE 3-6. Slave Processor Read Cycle (NS32532 CPU)

Note 1: FPU samples CPU status here. Note 2: FPU samples data bus here.

FIGURE 3-7. Slave Processor Write Cycle (NS32008, NS32016, NS32032 and NS32332 CPU)

Note 1: FPU samples CPU status here. Note 2: FPU samples data bus here.

FIGURE 3-8. Slave Processor Write Cycle (NS32532 CPU)

#### 3.6 INSTRUCTION PROTOCOLS

#### 3.6.1 General Protocol Sequences

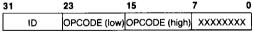

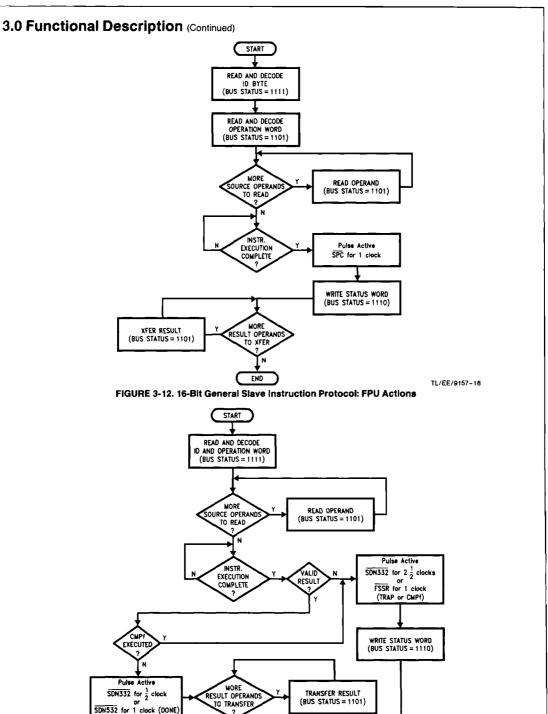

The NS32381 supports both the 16-bit and 32-bit General Slave protocol sequences. See Tables 3-1, 3-2 and *Figures 3-12, 3-13* respectively.

Slave Processor instructions have a three-byte Basic Instruction field, consisting of an ID byte followed by an Operation Word. See *Figure 3-9* for the ID and Opcode format 16-bit Slave Protocol and *Figure 3-10* for the ID and Opcode Format 32-bit Slave Protocol. The ID Byte has three functions:

1) It identifies the instruction to the CPU as being a Slave Processor instruction.

- 2) It specifies which Slave Processor will execute it.

- 3) It determines the format of the following Operation Word of the instruction.

Upon receiving a slave processor instruction, the CPU initiates a sequence outlined in either Table 3-1 or 3-2, depending on the PS0 and PS1, to allow for the 16-bit or 32-bit slave protocol. The NS32008, NS32016, NS32016, NS32032, NS32C032 and NS32CG16 all communicate with the NS32381 using the 16-bit Slave Protocol. The NS32332, NS32532 and NS32GX32 CPUs communicate with the NS32381 using a 32-bit Slave Protocol; a different version is provided for each CPU.

**TABLE 3-1. 16-Bit General Slave Instruction Protocol**

| Step | Status      | Action                                   |

|------|-------------|------------------------------------------|

| 1    | ID (1111)   | CPU sends ID Byte                        |

| 2    | OP (1101)   | CPU sends Operation Word                 |

| 3    | OP (1101)   | CPU sends required operands (if any)     |

| 4    | ′           | Slaves starts execution (CPU prefetches) |

| 5    |             | Slave pulses SPC low                     |

| 6    | ST (1110)   | CPU Reads Status Word                    |

| 7    | OP (1101)   | CPU Reads Result (if destination is      |

|      | , , , , , , | memory and if no TRAP occurred)          |

TABLE 3-2, 32-Bit General Slave Instruction Protocol

| Step | Status    | Action                                         |

|------|-----------|------------------------------------------------|

| 1    | ID (1111) | CPU sends ID and Operation Word                |

| 2    | OP (1101) | CPU sends required operands (if any)           |

| 3    |           | Slaves starts execution (CPU prefetches)       |

| 4    |           | Slave signals DONE or TRAP or CMPf             |

| 5    | ST (1110) | CPU Reads Status Word (If TRAP was signaled    |

|      | , ,       | or a CMPf instruction was executed)            |

| 6    | OP (1101) | CPU Reads Result (if destination is memory and |

| L    | , ,       | if no TRAP occurred)                           |

**TABLE 3-3. Floating-Point Instruction Protocols**

| Mnemonic | Operand 1<br>Class | Operand 2<br>Class | Operand 1<br>Issued | Operand 2<br>Issued | Returned Value Type and Destination | PSR Bits<br>Affected |

|----------|--------------------|--------------------|---------------------|---------------------|-------------------------------------|----------------------|

| ADDf     | read.f             | rmw.f              | f                   | f                   | f to Op. 2                          | none                 |

| SUBf     | read.f             | rmw.f              | f                   | l f                 | f to Op. 2                          | none                 |

| MULf     | read.f             | rmw.f              | f                   | f                   | f to Op. 2                          | none                 |

| DIVf     | read.f             | rmw.f              | ) f                 | f                   | f to Op. 2                          | none                 |

| MOVf     | read.f             | write.f            | f                   | N/A                 | f to Op. 2                          | none                 |

| ABSf     | read.f             | write.f            | f                   | N/A                 | f to Op. 2                          | none                 |

| NEGf     | read.f             | write.f            | l f                 | N/A                 | f to Op. 2                          | none                 |

| CMPf     | read.f             | read.f             | f                   | f                   | l N/A                               | N,Z,L                |

| FLOORfi  | read.f             | write.i            | l f                 | N/A                 | i to Op. 2                          | none                 |

| TRUNCfi  | read.f             | write.i            | f                   | N/A                 | i to Op. 2                          | none                 |

| ROUNDfi  | read.f             | write.i            | l f                 | N/A                 | i to Op. 2                          | none                 |

| MOVFL    | read.F             | write.L            | F                   | N/A                 | L to Op. 2                          | none                 |

| MOVLF    | read.L             | write.F            | l L                 | N/A                 | F to Op. 2                          | none                 |

| MOVif    | read.i             | write.f            | Ī                   | N/A                 | f to Op. 2                          | none                 |

| LFSR     | read.D             | N/A                | l D                 | N/A                 | l N/A                               | none                 |

| SFSR     | N/A                | write.D            | N/A                 | N/A                 | D to Op. 2                          | none                 |

| SCALBf   | read.f             | rmw.f              | l f                 | l f                 | f to Op.2                           | none                 |

| LOGBf    | read.f             | write.f            | f                   | N/A                 | f to Op.2                           | none                 |

| DOTE     | read.f             | read.f             | f                   | f                   | *f to FO/L0                         | none                 |

| POLYf    | read.f             | read.f             | f                   | f                   | *f to F0/L0                         | none                 |

D = Double Word

i = Integer size (B, W, D) specified in mnemonic.

f = Floating-Point type (F, L) specified in mnemonic.

N/A = Not Applicable to this instruction.

<sup>\*</sup>The "returned value" can go to either F0 or L0 depending on the "f" bit in the opcode, i.e., whether "floating" or "long" data type is used.

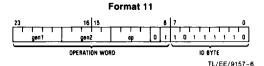

# 3.0 Functional Description (Continued) 7 0 ID Byte 15 7 0 OPCODE (Iow) OPCODE (high) Byte 1 Byte 0 Operation Word FIGURE 3-9. ID and OPCODE Format 18-Bit Slave Protocol

Byte 3 Byte 2 Byte 1 Byte 0

FIGURE 3-10. ID and OPCODE Format

32-Bit Siave Protocol

For the 16-bit Slave Protocol the CPU applies Status Code 1111 (Broadcast ID), and sends the ID Byte on the least significant half of the Data Bus (D0-D7). The CPU next sends the Operation Word while applying Status Code 1101 (Transfer Slave Operand). The Operation Word is swapped on the Data Bus; that is, bits 0-7 appear on pins D8-D15, and bits 8-15 appear on pins D0-D7.

For the 32-bit Slave Protocol the CPU applies Status Code 1111 and sends the ID Byte (different ID for each format) in byte 3 (D24-D31) and the Operation Word in bytes 1 and 2 in a single double word transfer. The Operation Word is swapped such that OPCODE low appears on byte 2 (D16-D23) and OPCODE high appears on byte 1 (D8-D15). Byte 0 (D0-D7) is not used.

All Slave Processors input and decode the data from these transfers. The Slave Processor selected by the ID Byte is activated and from this point on the CPU is communicating with it only. If any other slave protocol is in progress (e.g., an aborted Slave instruction), this transfer cancels it. Both the CPU and FPU are aware of the number and size of the operands at this point.

Using the Addressing Mode fields within the Operation Word, the CPU starts fetching operands and issuing them to the FPU. To do so, it references any Addressing Mode extensions appended to the FPU instruction. Since the CPU is solely responsible for memory accesses, these extensions are not sent to the Slave Processor. The Status Code applied is 1101 (Transfer Slave Processor Operand).

After the CPU has issued the last operand, the FPU starts the actual execution of the instruction. A one clock cycle SPC pulse is used to indicate the completion of the instruc-

tion and for the CPU to continue with the 16-Bit Slave Protocol by reading the FPU's Status Word Register.

For the 32-bit Slave Protocol, upon completion of the instruction, the FPU will signal the CPU by pulsing either SDNXXX or FSSR (Force Slave Status Read).

A half clock cycle SDN332 pulse with a NS32332 CPU, or a one clock cycle SDN532 pulse with a NS32532 or NS32GX32 CPU, indicates a valid completion of the instruction and that there is no need for the CPU to read its Status Word Register.

But if there is a need for the CPU to read FPU's Status Word Register, a two and a half clock cycle SDN332 (from NS32332) or a one clock cycle FSSR pulse (from NS32532 or NS32GX32) will be issued instead.

In all cases for both the 16-Bit and 32-Bit Slave Protocols the CPU will use \$\overline{SPC}\$ to read the Status Word from the FPU, while applying status code (1110). This word has the format shown in Figure 3-11. If the Q bit ("Quit", Bit 0) is set, this indicates that an error (TRAP) has been detected by the FPU. The CPU will not continue the protocol, but will immediately trap through the Slave vector in the Interrupt Table. If the instruction being performed is CMPf (Section 2.2.3) and the Q bit is not set, the CPU loads Processor Status Register (PSR) bits N, Z and L from the corresponding bits in the FPU Status Word. The FPU always sets the L bit to zero.

The last step will be for the CPU to read the result, provided there are no errors and the results destination is in memory. Here again the CPU uses SPC to read the result from the FPU and transfer it to its destination. These Read cycles from the FPU are performed by the CPU while applying Status Code 1101 (Transfer Slave Operand).

| 31   | 15 |      | 7  |   |   |     | 0   |

|------|----|------|----|---|---|-----|-----|

| ZERO | тѕ | ZERO | NZ | 0 | 0 | 0 L | 0 0 |

## Bit Description (0) Q: Set to "1" if an FPU TRAP (error) occurred.

- Cleared to '0" by a valid CMPf.

- (2) L: Cleared to "0" by the FPU.

- (6) Z: Set to "1" if the second operand is equal to the first operand. Otherwise it is cleared to "0".

- (7) N: Set to "1" if the second operand is less than the first operand. Otherwise it is cleared to "0"

- (15) TS: Set to "1" if the TRAP is (UND) and cleared to "0" if the TRAP is (FPU).

FIGURE 3-11, FPU Status Word Format

TL/EE/9157-17

FIGURE 3-13. 32-Bit General Slave Instruction Protocol: FPU Actions

END

#### 3.6.2 Early Done Algorithm

The NS32381 has the ability to modify the General Slave protocol sequences and to boost the performance of the FPU by 20% to 40%. This is called the Early Done Algorithm.

Early Done is defined by the fact that the destination of an instruction is an FPU register and that the instruction and range of operands cannot generate a TRAP (error). When these conditions are met the FPU will send a SDNXXX or SPC pulse after receiving all of the operands from the CPU and before executing the instruction. Hence this becomes an early done as compared to the General Slave Protocols. In the case of the 16-bit Slave Protocol in which the CPU always reads the slave status word, the FPU will force all zeroes to be read. The CPU can then send the next instruction to the FPU and save the general protocol overhead. The FPU will start the new instruction immediately after finishing the previous instruction.

SFSR, CMPF and CMPL do not generate an Early Done.

#### 3.6.3 Floating-Point Protocols

Table 3-3 gives the protocols followed for each floatingpoint instruction. The instructions are referenced by their mnemonics. For the bit encodings of each instruction, see section 2.2.3.

The Operand Class columns give the Access Classes for each general operand, defining how the addressing modes are interpreted by the CPU (see Series 32000 Instruction Set Reference Manual).

The Operand Issued columns show the sizes of the operands issued to the Floating-Point Unit by the CPU. "D" indicates a 32-bit Double Word. "j" indicates that the instruction specifies an integer size for the operand (B = Byte, W = Word). "f" indicates that the instruction specifies a floating-point size for the operand (F = 32-bit Standard Floating, L = 64-bit Long Floating).

The Returned Value Type and Destination column gives the size of any returned value and where the CPU places it. The PSR Bits Affected column indicates which PSR bits, if any, are updated from the FPU Status Word (Figure 3-11).

Any operand indicated as being of type "f" will not cause a transfer if the Register addressing mode is specified, because the Floating-Point Registers are physically on the Floating-Point Unit and are therefore available without CPU assistance

#### 4.0 Device Specifications

#### 4.1 PIN DESCRIPTIONS

#### 4.1.1 Supplies

GND

The following is a brief description of all NS32381 pins.

V<sub>CC</sub> Power: +5V positive supply.

Ground: Ground reference for both on-chip log-

ic and drivers connected to output pins.

#### 4.1.2 Input Signals

CLK Clock: TTL-level clock signal.

\*DDIN Data Direction In: Active low. Status signal indicating the direction of data transfers during a

bus cycle.

ST0-ST3 Status: Bus cycle status code from CPU. ST0 is the least significant and rightmost bit.

1100— Reserved

1101— Transferring Operation Word or Operand

1110- Reading Status Word

1111- Broadcasting Slave ID

Note: The NS32332 generates four status lines and the NS32532 generates five. The user should connect the status lines as shown below:

| NS32381 | NS32332 | NS32532 |

|---------|---------|---------|

| ST0     | ST0     | ST0     |

| ST1     | ST1     | ST1     |

| ST2     | ST2     | ST2     |

| ST3     | ST3     | ST4     |

RST Reset: Active low. Resets the last operation and clears the FSR register.

NOE New Opcode Enable: Active high. This signal enables the new opcodes available in the NS32361.

PS0, PS1 Protocol Select: Selects the slave protocol to be used. PS0 is the least significant and rightmost bit.

00-Selects 16-bit protocol.

01-Selects 32-bit protocol for NS32332.

10-Reserved.

11-Selects 32-bit protocol for NS32532.

#### 4.1.3 Output Signals

SDN332

Slave Done 332: Active low. This signal is for use with the NS32332 CPU only. If held active for a half clock cycle and released this pin indicates the successful completion of a floating-point instruction by the FPU. Holding this pin active for two and a half clock cycles indicates TRAP or that the CMPf instruction has been executed.

SDN532 Slave Done 532: Active low. This signal is for use with the NS32532 CPU only. When active it indicates successful completion of a floating-point instruction by the FPU.

FSSR Force Slave Status Read: Active low. This signal is for use with the NS32532 CPU only. When active it indicates TRAP or that the CMPf instruction has been executed.

#### 4.1.4 Input/Output Signals

\*D0~D31 Data Bus: These are the 32 signal lines which carry data between the NS32381 and the CPU.

SPC Slave Processor Control: Active low. This is the

Slave Processor Control: Active low. This is the data strobe signal for slave transfers. For the 32-bit protocol, SPC is only an input signal.

\*For the 16-bit Slave Protocol the upper sixteen data input signals (D16-D31) and  $\overline{\text{DDIN}}$  should be left floating.

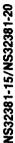

#### **Connection Diagrams**

TL/EE/9157-18

Order Number NS32381 See NS Package Number U68D

FIGURE 4-1. 68-Pin PGA Package NS32381 Pinout Descriptions

| Desc              | Pin |

|-------------------|-----|

| Vcc               | A2  |

| D1                | A3  |

| D0                | A4  |

| PS1 (Note 1)      | A5  |

| GND               | A6  |

| GND               | A7  |

| CLK               | A8  |

| RŠT               | A9  |

| Reserved (Note 2) | A10 |

| Reserved (Note 2) | B1  |

| D2                | B2  |

| D17               | B3  |

| D16               | B4  |

| PS0 (Note 1)      | B5  |

| GND               | B6  |

| NOE (Note 1)      | B7  |

| Reserved (Note 3) | B8  |

| Reserved (Note 2) | B9  |

| Vcc               | B10 |

| D15               | B11 |

| D18               | C1  |

| D3                | C2  |

| D31               | C10 |

| D14               | C11 |

| D19               | D1  |

| Vcc               | D2  |

| D30               | D10 |

| V <sub>CC</sub>   | D11 |

| D4                | E1  |

| D20               | E2  |

| D13               | E10 |

| D29               | E11 |

| Reserved (Note 3) | F1  |

| D5                | F2  |

| Desc              | Pin |

|-------------------|-----|

| D28               | F10 |

| GND               | F11 |

| GND               | G1  |

| D21               | G2  |

| D12               | G10 |

| D27               | G11 |

| D6                | H1  |

| D22               | H2  |

| D11               | H10 |

| SDN332            | H11 |

| D7                | J1  |

| D23               | J2  |

| SPC               | J10 |

| SDN532            | J11 |

| V <sub>CC</sub>   | K1  |

| D8                | K2  |

| GND               | К3  |

| D26               | K4  |

| GND               | K5  |

| V <sub>CC</sub>   | K6  |

| Reserved (Note 3) | K7  |

| ST0               | K8  |

| ST1               | K9  |

| Reserved (Note 3) | K10 |

| GND               | K11 |

| D24               | L2  |

| D25               | L3  |

| D9                | L4  |

| D10               | L5  |

| DDIN              | L6  |

| Vcc               | L7  |

| ST2               | L8  |

| ST3               | L9  |

| FSSR              | L10 |

Note 1: CMOS input; never float.

Note 2: Pin should be grounded.

Note 3: Pin should be left floating.

#### **4.2 ABSOLUTE MAXIMUM RATINGS**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Maximum Case Temperature

95°C

Storage Temperature

-65°C to +150°C

All Input or Output Voltages

with Respect to GND

**ESD Rating**

2000V (in human body model)

-0.5V to +7.0V

Note: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended; operation should be limited to those conditions specified under Electrical Characteristics.

4.3 ELECTRICAL CHARACTERISTICS  $T_{A}=0^{\circ}C$  to 70°C,  $V_{CC}=5V~\pm5\%, GND=0V$

| Symbol          | Parameter                                                      | Conditions                                                        | Min    | Тур | Max                   | Units |

|-----------------|----------------------------------------------------------------|-------------------------------------------------------------------|--------|-----|-----------------------|-------|

| V <sub>IH</sub> | High Level Input Voltage*                                      |                                                                   | 2.0    |     | V <sub>CC</sub> + 0.5 | V     |

| ViL             | Low Level Input Voltage*                                       |                                                                   | -0.5   |     | 0.8                   | ٧     |

| V <sub>OH</sub> | High Level Output Voltage                                      | I <sub>OH</sub> = -400 μA                                         | 2.4    |     |                       | ٧     |

| VOL             | Low Level Output Voltage                                       | I <sub>OL</sub> = 2 mA                                            |        |     | 0.4                   | V     |

| l <sub>l</sub>  | Input Load Current*                                            | 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                             | - 10.0 |     | 10.0                  | μΑ    |

| V <sub>IH</sub> | High Level Input Voltage for PS0, PS1, NOE                     |                                                                   | 3.5    |     | V <sub>CC</sub> + 0.5 | ٧     |

| VIL             | Low Level Input Voltage<br>for PS0, PS1, NOE                   |                                                                   | -0.5   |     | 1.5                   | ٧     |

| lį              | Input Load Current<br>for PS0, PS1, NOE                        | 0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>                             | -100   |     | 100                   | μА    |

| i <sub>L</sub>  | Leakage Current (Output and I/O Pins in TRI-STATE®/Input Mode) | 0.4 ≤ V <sub>OUT</sub> ≤ 2.4V                                     | -20.0  |     | 20.0                  | μА    |

| lcc             | Active Supply Current                                          | I <sub>OUT</sub> = 0, T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5V |        |     | 300                   | mA    |

| loc             | Power Down Current                                             | I <sub>OUT</sub> = 0, T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5V |        |     | 60                    | mA    |

<sup>\*</sup>Except PS0, PS1, NOE and Reserved pins.

Note: PS0, PS1 NOE pins have to be connected to either GND or V<sub>CC</sub> (possible via resistor) as it is shown in Figure 3-4a, 3-4b, 3-4c, and 3-4d.

#### **4.4 SWITCHING CHARACTERISTICS**

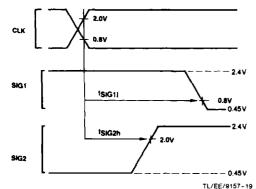

#### 4.4.1 Definitions

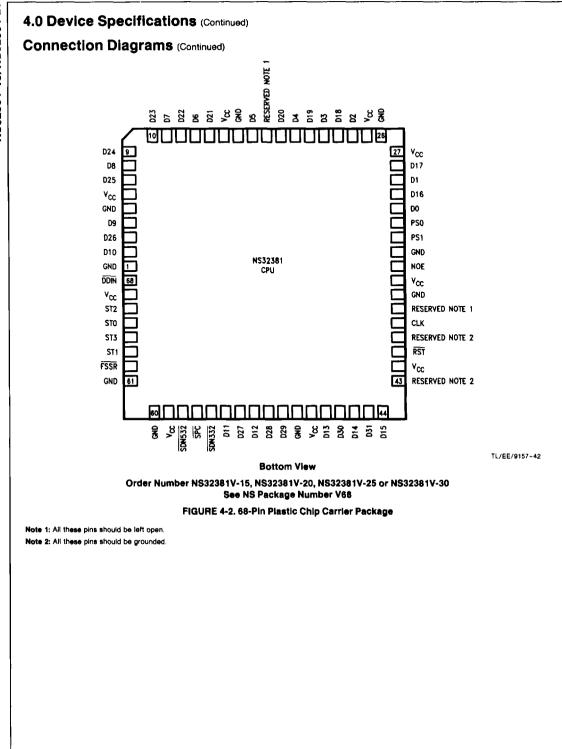

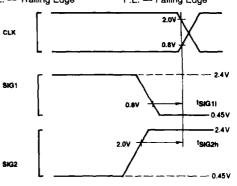

All the Timing Specifications given in this section refer to 0.8V and 2.0V on all the input and output signals as illustrated in *Figures 4.3* and *4.4*, unless specifically stated otherwise.

FIGURE 4-3. Timing Specification Standard (Signal Valid after Clock Edge)

#### ABBREVIATIONS

L.E. — Leading Edge R.E. — Rising Edge T.E. — Trailing Edge F.E. — Falling Edge

FIGURE 4-4. Timing Specification Standard (Signal Valid before Clock Edge)

- 4.4.2 Timing Tables (Maximum times assume temperature range 0°C to 70°C)

- 4.4.2.1 Output Signal Propagation Delays for all CPUs (16-Bit Slave Protocol) (Maximum times assume capacitive loading of 100 pF)

| Symbol Figure                     | Description | Reference/               | NS32381-15              |                        | NS32381-20             |                        | NS32                   | Units                  |                        |    |

|-----------------------------------|-------------|--------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----|

|                                   |             | Conditions               | Min                     | Max                    | Min                    | Max                    | Min                    | Max                    | 1                      |    |

| tspcf <sub>w</sub>                |             | SPC Pulse Width from FPU | At 0.8V<br>(Both Edges) | t <sub>CLKp</sub> - 10 | t <sub>CLKp</sub> + 10 | t <sub>CLKp</sub> - 10 | t <sub>CLKp</sub> + 10 | t <sub>CLKp</sub> - 10 | t <sub>CLKp</sub> + 10 | ns |

| tspcf <sub>a</sub>                | 4-18        | SPC Output Active        | After CLK R.E.          |                        | 17                     |                        | 17                     |                        | 15                     | ns |

| tspcria                           | 4-18        | SPC Output Inactive      | After CLK R.E.          |                        | 38                     | -                      | 33                     |                        | 25                     | ns |

| tspcF <sub>f</sub> <sup>(1)</sup> | 4-18        | SPC Output Floating      | After CLK F.E.          |                        | 35                     |                        | 30                     |                        | 25                     | ns |

#### 4.4.2.2 Output Signal Propagation Delays for the NS32008, NS32016 and NS32032 CPUs Maximum times assumes capacitive loading of 100 pF

NS32381-15 NS32381-20 NS32381-25 Reference/ **Symbol Figure** Description Units Conditions Min Min Max Max 4-8 After SPC L.E.  $t_{D_{\mathbf{v}}}$ Data Valid (D0-D15) 30 18 ns  $t_{D_f}^{(1)}$ 4-8 After SPC T.E. D0-D15 Floating 30 30 ns

### 4.4.2.3 Output Signal Propagation Delays for the 32-Bit Slave Protocol NS32332 CPU Maximum times assume capacitive loading of 100 pF unless otherwise specified

| Symbol                         | Figure   | Description                      | Reference/                            | NS32                      |                           |       |  |

|--------------------------------|----------|----------------------------------|---------------------------------------|---------------------------|---------------------------|-------|--|

| <b>Oy</b>                      | riguie   | Cescription                      | Conditions                            | Min                       | Max                       | Units |  |

| t <sub>Dv</sub>                | 4-10     | Data Valid                       | After SPC L.E.;<br>75 pF Cap. Loading |                           | 25                        | ns    |  |

| t <sub>Dh</sub>                | 4-10     | Data Hold                        | After SPC T.E.                        | 8                         |                           | ns    |  |

| t <sub>Df</sub> (1)            | 4-10     | Data Floating                    | After SPC T.E.                        |                           | 30                        | ns    |  |

| t <sub>SDNa</sub>              | 4-12, 13 | Slave Done Active                | After CLK F.E.                        | 3                         | 28                        | ns    |  |

| tsonh                          | 4-13     | Slave Done Hold                  | After CLK R.E.                        |                           | 33                        | ns    |  |

| t <sub>SDN<sub>w</sub></sub>   | 4-12     | Slave Done<br>Pulse Width        | At 0.8V<br>(Both Edges)               | 1/2 t <sub>CLKp</sub> -10 | ½ t <sub>CLKp</sub> + 10  | ns    |  |

| t <sub>SDNf</sub> (1)          | 4-12, 13 | Slave Done Floating              | After CLK R. E.                       |                           | 30                        | ns    |  |

| <sup>t</sup> STRP <sub>w</sub> | 4-13     | Slave Done (TRAP)<br>Pulse Width | At 0.8V<br>(Both Edges)               | 2½ t <sub>CLKp</sub> -10  | 2½ t <sub>CLKp</sub> + 10 | ns    |  |

Note 1: Not 100% tested.

## **4.4.2.4 Output Signal Propagation Delays for the 32-Bit Slave Protocol NS32532 CPU**Maximum times assume capacitive loading of 50 pF

|                                 | 1      |                                      | Reference/      | NS32381- |     |     |     |     |    |       |

|---------------------------------|--------|--------------------------------------|-----------------|----------|-----|-----|-----|-----|----|-------|

| Symbol                          | Figure | Description                          | Conditions      | 20       |     | 25  |     | 30  |    | Units |

|                                 |        |                                      | Min             | Max      | Min | Max | Min | Max |    |       |

| t <sub>Dv</sub>                 | 4-14   | Data Valid                           | After SPC L.E.  |          | 35  |     | 35  |     | 35 | ns    |

| t <sub>Dh</sub>                 | 4-14   | Data Hold                            | After CLK R.E.  | 3        |     | 3   |     | 3   |    | ns    |

| t <sub>Df</sub> (1)             | 4-14   | Data Floating                        | After SPC T.E.  |          | 30  |     | 30  |     | 30 | ns    |

| t <sub>SDa</sub>                | 4-16   | Slave Done Active                    | After CLK R.E.  |          | 35  |     | 25  |     | 20 | ns    |

| t <sub>SDh</sub>                | 4-16   | Slave Done Hold                      | After CLK R.E.  | 2        | 33  | 2   | 25  | 2   | 20 | ns    |

| t <sub>SDf</sub> <sup>(1)</sup> | 4-16   | Slave Done Floating                  | After CLK R. E. |          | 30  |     | 30  |     | 30 | ns    |

| t <sub>FSSRa</sub>              | 4-17   | Forced Slave Status<br>Read Active   | After CLK R.E.  |          | 35  |     | 25  |     | 20 | ns    |

| trssrh                          | 4-17   | Forced Slave Status<br>Read Hold     | After CLK R.E.  | 2        | 33  | 2   | 25  | 2   | 20 | ns    |

| t <sub>FSSRf</sub> (1)          | 4-17   | Forced Slave Status<br>Read Floating | After CLK R.E.  |          | 30  |     | 30  |     | 30 | ns    |

#### 4.4.2.5 Input Signal Requirements with all CPUs

|                   |        |                         |                          | NS32381- |     |     |     |       |     |     |     |       |    |  |       |

|-------------------|--------|-------------------------|--------------------------|----------|-----|-----|-----|-------|-----|-----|-----|-------|----|--|-------|

| Symbol            | Figure | Description             | Reference/<br>Conditions | 15       |     | 15  |     | 15 20 |     | 20  | 25  |       | 30 |  | Units |

|                   |        |                         |                          | Min      | Max | Min | Max | Min   | Max | Min | Max |       |    |  |       |

| tpwR              | 4-5    | Power-On Reset Duration | After CLK R.E.           | 30       |     | 30  |     | 30    |     | 30  |     | μs    |    |  |       |

| t <sub>RSTw</sub> | 4-6    | Reset Pulse Width       | At 0.8V (Both Edges)     | 64       |     | 64  |     | 64    |     | 64  |     | tCLKp |    |  |       |

| tests             | 4-7    | Reset Setup Time        | Before CLK R.E.          | 10       |     | 14  |     | 12    |     | 11  |     | ns    |    |  |       |

| testh             | 4-7    | Reset Hold              | After CLK R.E.           | 0        |     | 0   |     | 0     |     | 0   |     | ns    |    |  |       |

#### 4.4.2.6 Input Signal Requirements with the NS32008, NS32016, NS32032 CPUs

| Symbol            | Figure | Description              | Reference/<br>Conditions | NS32381-15 |     | NS32381-20 |     | NS32381-25 |     | Units |

|-------------------|--------|--------------------------|--------------------------|------------|-----|------------|-----|------------|-----|-------|

|                   | 1.3    |                          |                          | Min        | Max | Min        | Max | Min        | Max |       |

| tSs               | 4-8    | Status (ST0-ST1) Setup   | Before SPC L.E.          | 20         |     | 20         |     | 15         |     | ns    |

| t <sub>Sh</sub>   | 4-8    | Status (ST0-ST1) Hold    | After SPC L.E.           | 20         |     | 20         |     | 17         |     | ns    |

| t <sub>Ds</sub>   | 4-9    | Data Setup (D0-D15)      | Before SPC T.E.          | 25         |     | 20         |     | 15         |     | ns    |

| t <sub>Dh</sub>   | 4-9    | Data Hold (D0-D15)       | After SPC T.E.           | 20         |     | 20         |     | 15         |     | ns    |

| t <sub>SPCw</sub> | 4-8    | SPC Pulse Width from CPU | At 0.8V<br>(Both Edges)  | 35         |     | 35         |     | 28         |     | ns    |

Note 1: Not 100% tested.

#### 4.4.2.7 Input Signal Requirements with the 32-Bit Siave Protocol NS32332 CPU

| Symbol            | Figure  | Description     | Reference/           | NS323   | Units |    |  |

|-------------------|---------|-----------------|----------------------|---------|-------|----|--|

| Symbol .          | i iguit | Description     | Conditions           | Min Max |       | ]  |  |

| t <sub>STs</sub>  | 4-11    | Status Setup    | Before SPC L.E.      | 20      |       | ns |  |

| t <sub>STh</sub>  | 4-11    | Status Hold     | After SPC L.E.       | 20      |       | ns |  |

| t <sub>Ds</sub>   | 4-11    | Data Setup      | Before SPC T.E.      | 20      |       | ns |  |

| t <sub>Dh</sub>   | 4-11    | Data Hold       | After SPC T.E.       | 20      |       | ns |  |

| t <sub>SPCw</sub> | 4-11    | SPC Pulse Width | At 0.8V (Both Edges) | 35      |       | ns |  |

#### 4.4.2.8 input Signal Requirements with the 32-Bit Slave Protocol NS32532 CPU

|                    |          |                         | ,                        | NS32381 |     |     |     |     |     |       |

|--------------------|----------|-------------------------|--------------------------|---------|-----|-----|-----|-----|-----|-------|

| Symbol             | Figure   | Description             | Reference/<br>Conditions | 20      |     | 25  |     | 30  |     | Units |

|                    |          |                         | gon, antions             | Min     | Max | Min | Max | Min | Max |       |

| tsts               | 4-15     | Status Setup            | Before CLK (T2) R.E.     | 25      |     | 20  |     | 20  |     | ns    |

| tsT <sub>h</sub>   | 4-15     | Status Hold             | After CLK (T2) R.E.      | 20      |     | 10  |     | 10  |     | ns    |

| t <sub>DDINs</sub> | 4-15     | Data Direction In Setup | Before SPC L.E.          | 0       |     | 0   |     | 0   |     | ns    |

| t <sub>DDINh</sub> | 4-15     | Data Direction in Hold  | After SPC T.E.           | 10      |     | 10  |     | 10  |     | ns    |

| t <sub>Ds</sub>    | 4-15     | Data Setup              | Before SPC T.E.          | 6       |     | 6   |     | 4   |     | ns    |

| t <sub>Dh</sub>    | 4-15     | Data Hold               | After SPC T.E.           | 20      |     | 10  |     | 10  |     | ns    |

| tspcs              | 4-14, 15 | SPC Setup               | Before CLK R.E.          | 20      |     | 20  |     | 20  |     | ns    |

| tspch              | 4-14, 15 | SPC Hold                | After CLK R.E.           | 0       |     | 0   |     | 0   |     | ns    |

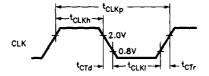

#### 4.4.2.9 Clocking Requirements with all CPUs

|                                 | ibol Figure Description |                 |                           | NS32381 |      |     |      |     |      |      |      |       |

|---------------------------------|-------------------------|-----------------|---------------------------|---------|------|-----|------|-----|------|------|------|-------|

| Symbol                          |                         |                 | n Reference/              |         | 15   |     | 20   |     | 25   |      | 30   |       |

|                                 |                         |                 | - Containions             | Min     | Max  | Min | Max  | Min | Max  | Min  | Max  | Units |

| tcLKh                           | 4-4                     | Clock High Time | At 2.0 V (Both Edges)     | 25      | 1000 | 20  | 1000 | 16  | 1000 | 13   | 1000 | ns    |

| <sup>t</sup> CLK <sub>I</sub>   | 4-4                     | Clock Low Time  | At 0.8V (Both Edges)      | 25      | DC   | 20  | DC   | 16  | DC   | 13   | DC   | ns    |

| t <sub>CTr</sub> <sup>(1)</sup> | 4-4                     | Clock Rise Time | Between 0.8V and 2.0V     |         | 7    |     | 5    |     | 4    |      | 3    | ns    |

| t <sub>CTd</sub> <sup>(1)</sup> | 4-4                     | Clock Fall Time | Between 2.0V and 0.8V     |         | 7    |     | 5    |     | 4    |      | 3    | ns    |

| t <sub>CLKp</sub>               | 4-4                     | Clock Period    | CLK R.E. to Next CLK R.E. | 66      | DC   | 50  | DC   | 40  | DC   | 33.3 | DC   | ns    |

Note 1: Not 100% tested.

#### 4.4.3 Timing Diagrams

FIGURE 4-5. Clock Timing

TL/EE/9157-21

TL/EE/9157-22

TL/EE/9157-23 FIGURE 4-7. Non-Power-On Reset

TL/EE/9157-24

FIGURE 4-8. AST Release Timing

Note: The rising edge of RST must occur while CLK is high, as shown.

FIGURE 4-9. Read Cycle from FPU (NS32008, NS32016, NS32032 CPUs)

#### Appendix A

#### **NS32381 PERFORMANCE ANALYSIS**

The following performance numbers were taken from simulations using the 381 SIMPLE model. The timing terms have been designed to provide performance numbers which are CPU independent. Numbers were obtained from SIMPLE simulations, taking the average execution times using 'typical' operands.

Listed below are definitions of the timing terms:

- EXT (EXecution Time) This is the time from the last data sent to the FPU, until the early DONE is issued. (FPU Pipe is empty)

- EDD (Early Done Delta) This is the time from when the early DONE is issued until the execution of the next instruction may start.

Provided that the CPU can transfer the ID/OPCODE and any operands to the FPU during the EDD time, the average system execution time for an instruction (keeping the FPU pipe filled) is: EXT + EDD.

The system execution time for a single FPU instruction with FPU register destination and early done is: EXT plus the protocol time. (FPU pipe is initially empty)

| Instruction    | EXT' | EDD. | Total* |

|----------------|------|------|--------|

| LFSR any, reg  | 5    | 8    | 13     |

| MOVF any, reg  | 5    | 6    | 11     |

| MOVL any, reg  | 5    | . 8  | 13     |

| MOVif any, reg | _ 5  | 45   | 50     |

| MOVFL any, reg | 9    | 6    | 15     |

| ADDF any, reg  | 11   | 31   | 42     |

| ADDL any, reg  | 11   | 31   | 42     |

| SUBF any, reg  | 11   | 31   | 42     |

| SUBL any, reg  | 11   | 31   | 42     |

| MULF any, reg  | 11   | 20   | 31     |

| MULL any, reg  | 11   | 27   | 38     |

| DIVF any, reg  | 11   | 45   | 56     |

| DIVL any, reg  | 11   | 59   | 70     |

| POLYF any, any | 15   | 46   | 61     |

| POLYL any, any | 15   | 53   | 68     |

| DOTF any, any  | 15   | 46   | 61     |

| DOTL any, any  | 15   | 53   | 68     |

<sup>\*</sup>Measured in the number of clock cycles.

#### **NS32381 PERFORMANCE ANALYSIS**

The following instructions do not generate an early done. In this case, EXT is the time from the last data sent to the FPU, until the normal DONE is issued. (FPU Pipe is empty)

| Instru  | Instruction |    |  |  |  |

|---------|-------------|----|--|--|--|

| SFSR    | reg, mem    | 7  |  |  |  |

| MOVLF   | any, any    | 18 |  |  |  |

| ROUNDfi | any, mem    | 46 |  |  |  |

| FLOORfi | any, mem    | 46 |  |  |  |

| TRUNCfi | any, mem    | 46 |  |  |  |

| CMPF    | any, any    | 17 |  |  |  |

| CMPL    | any, any    | 17 |  |  |  |

| ABSf    | any, any    | 9  |  |  |  |

| NEGf    | any, any    | 9  |  |  |  |

| SCALBf  | any, any    | 49 |  |  |  |

| LOGBf   | any, any    | 36 |  |  |  |