## Advanced Micro Devices

## Am79C83

## Fiber Optic Ring Media Access Controller (FORMAC)

#### DISTINCTIVE CHARACTERISTICS

- Implements Media Access Control (MAC) layer protocol for the ANSI X3T9.5 standard (Fiber Distributed Data Interface, FDDI)

- Error detection capability

- Cyclic redundancy checking and generation

- Token claiming and beacon modes

- Diagnostics Features

- Four loopback modes

- Status bit collection

- Supports data rates up to 100 Mbps

- Supports group, individual, and broadcast addressing

- Allows external address detection circuits

- Useful in bridge applications

- Supports prioritized transmission of asynchronous messages

- Promiscuous mode for network monitoring

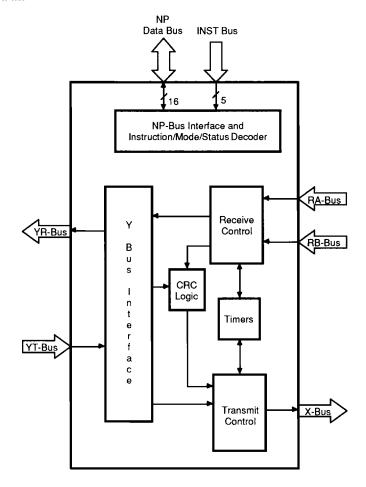

#### **BLOCK DIAGRAM**

09731-001A

Publication# 09731 Rev. D Amendment/0

Issue Date: October 1991

#### **GENERAL DESCRIPTION**

The Am79C83A Fiber Optic Ring Media Access Controller (FORMAC) is a CMOS device which implements the timed token passing protocol specified by the FDDI standard. It performs frame formation functions such as generating preamble, CRC, and status information. It

facilitates error recovery with token claiming and beaconing capability. Information needed by station-management software for ring diagnostics and statistical network characterization is also provided by the FORMAC.

#### Notes:

The word "frame" is used in the SUPERNET data sheets to describe three different groups of information.

1. One group is passed over the network media and has the following structure:

| Frame    | Start     | Frame   | Destination | Source  |             | Frame          | End       | Frame  |

|----------|-----------|---------|-------------|---------|-------------|----------------|-----------|--------|

| Preamble | Delimiter | Control | Address     | Address | Information | Check Sequence | Delimiter | Status |

The others are stored in buffer memory and are structured as follows:A) Transmit frame

|            | Frame   | Destination | Source  |             | Frame          |         |

|------------|---------|-------------|---------|-------------|----------------|---------|

| Descriptor | Control | Address     | Address | Information | Check Sequence | Pointer |

B) Receive frame

|            | Frame   | Destination | Source  |             | Frame          |

|------------|---------|-------------|---------|-------------|----------------|

| Descriptor | Control | Address     | Address | Information | Check Sequence |

### **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                                   | . 4–1 |

|---------------------------------------------------------------|-------|

| BLOCK DIAGRAM                                                 | . 4–1 |

| GENERAL DESCRIPTION                                           | . 4–2 |

| CONNECTION DIAGRAM                                            | . 4–9 |

| LOGIC SYMBOL                                                  |       |

| ORDERING INFORMATION                                          |       |

| PIN DESCRIPTION                                               |       |

| FUNCTIONAL DESCRIPTION                                        |       |

|                                                               |       |

| Overview of User-Accessible Resources Programmable Resources  |       |

| Hardwired Resources                                           |       |

| Block Diagram                                                 |       |

| Operational Modes                                             |       |

| Initialization Initialization                                 |       |

| On-Line                                                       |       |

| Loopback                                                      |       |

| HOLD <sub>1</sub> Operation                                   |       |

| FORMAC Programming                                            |       |

| Instruction Set                                               |       |

| Address Registers (ADRSo-7)                                   |       |

| MAC Information Register (MIR <sub>0-1</sub> )                |       |

| TMAX Register (TMAX)                                          |       |

| TVX Register (TVX)                                            |       |

| State Machine Register (STAT)                                 |       |

| Status Register and Interrupts Interrupt Mask Register (IMSK) |       |

| Asynchronous Priority Register (TPRI)                         |       |

| Frame Status Register (FRSTAT)                                |       |

| Data Handling and Formats                                     | 4-40  |

| FDDI Frame Formats                                            |       |

| Network Data Format                                           |       |

| User Test Modes                                               |       |

| ABSOLUTE MAXIMUM RATINGS                                      |       |

| OPERATING RANGES                                              | 4–41  |

| DC CHARACTERISTICS                                            | 4-41  |

| CAPACITANCE                                                   | 4-41  |

| SWITCHING CHARACTERISTICS                                     | 4-42  |

| SWITCHING WAVEFORMS                                           |       |

| SWITCHING TEST CIRCUIT                                        |       |

|                                                               |       |

| SWITCHING TEST WAVEFORM                                       | 4-50  |

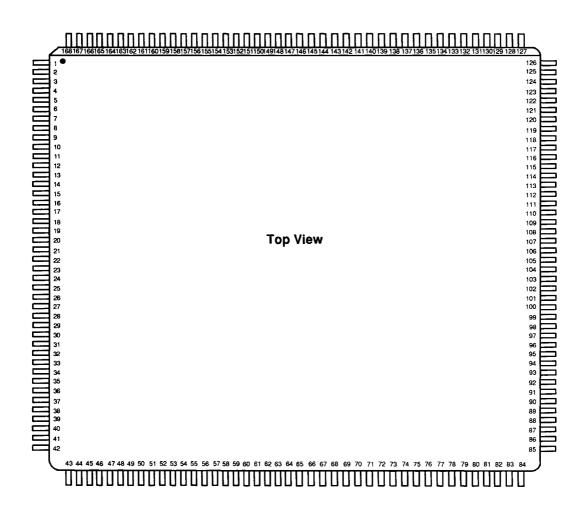

# CONNECTION DIAGRAM PGA Bottom View (Pins facing up)

|    | Α       | В       | С       | D       | E       | F      | G      | Н      | J    | K      | L      | М      | N          | Р     | R    |    |

|----|---------|---------|---------|---------|---------|--------|--------|--------|------|--------|--------|--------|------------|-------|------|----|

| 1  | vcc     | R∕₩     | INST2   | INST1   | DS      | NP15   | NP13   | NP11   | NP8  | NP4    | NP2    | NP1    | NAME       | READY | RAP  | 1  |

| 2  | i NC    | RESET   | INST3   | टडा     | NP14    | NP12   | NP10   | NC     | NP6  | NP5    | NP3    | NPO    | HOLD1      | HOLD2 | RACU | 2  |

| 3  | NC NC   | YR7     | BCLK    | INSTO   | GND     | BMODE  | GND    | NP9    | vcc  | NP7    | GND    | митя   | LPBEN      | RA6   | RACL | 3  |

| 4  | YR5     | YR4     | YR6     | •       |         |        |        |        |      |        |        |        | GND        | RA7   | NC   | 4  |

| 5  | YA2     | YRO     | YRP     |         |         |        |        |        |      |        |        |        | RA2        | RA4   | RA5  | 5  |

| 6  | ΥΠ      | YR3     | GND     |         |         |        |        |        |      |        |        |        | RA3        | RA1   | RA0  | 6  |

| 7  | vcc     | YTP     | YR1     |         |         |        |        |        |      |        |        |        | vcc        | RBP   | RBCU | 7  |

| 8  | YT6     | GND     | GND .   |         |         |        | Botto  | om Vie | ew   |        |        |        | RBCL       | RB7   | NC   | 8  |

| 9  | YT4     | YT5     | YT1     |         |         |        |        |        |      |        |        |        | GND        | RB5   | RB6  | 9  |

| 10 | YT2     | YT0     | RDYTBYT |         |         |        |        |        |      |        |        |        | RB4        | RB3   | FIB2 | 10 |

| 11 | XMTABTI | YT3     | XMEDAVA |         |         |        |        |        |      |        |        |        | GND        | RB1   | RB0  | 11 |

| 12 | XMTABTO | XMEDAVS | GND     |         |         |        |        |        |      |        |        |        | ХР         | xcu   | XCL  | 12 |

| 13 | RECEIVE | XFRBYTE | FULL    | MEDREGA | GND     | LNGADR | XSAMAT | GND    | S1   | LSTING | X2     | TOKISŌ | <b>X</b> 7 | X5    | X6   | 13 |

| 14 | DAVALID | RCVABTI | MISFRM  | MEDREOS | INICLEN | XDAMAT | соит   | GND    | AOUT | FRINC  | ERRING | GND    | Χo         | vcc   | X4   | 14 |

| 15 | FSHRCVF | RCVABTO | SI      | TEST    | CLM/BEC | FSVLO  | SDACVD | vcc    | ÉOUT | S0     | S2     | S3     | So         | Хı    | хз   | 15 |

| ٠  | A       | В       | С       | D       | E       | F      | G      | н      | J    | к      | Ł      | м      | N          | Р     | R    |    |

NC = No Connection

09731-002A

### **PIN DESIGNATIONS**

### (Sorted by Pin Number)

| Pin  |                   | Pin  |                   | Pin  |                   | Pin  |                   |

|------|-------------------|------|-------------------|------|-------------------|------|-------------------|

| No.  | Pin Name          |

| A-1  | Vcc               | C-7  | YR <sub>1</sub>   | H-13 | GND               | N-10 | RB <sub>4</sub>   |

| A-2  | NC                | C-8  | GND               | H-14 | GND               | N-11 | GND               |

| A-3  | NC                | C-9  | YT <sub>1</sub>   | H-15 | Vcc               | N-12 | XP                |

| A-4  | YR5               | C-10 | RDYTBYT           | J-1  | NP8               | N-13 | X7                |

| A-5  | YR <sub>2</sub>   | C-11 | XMEDAVA           | j-2  | NP <sub>6</sub>   | N-14 | X <sub>0</sub>    |

| A-6  | YT <sub>7</sub>   | C-12 | GND               | J-3  | vcc               | N-15 | So                |

| A-7  | Vcc               | C-13 | FULL              | J-13 | S <sub>1</sub>    | P-1  | READY             |

| A-8  | YT <sub>6</sub>   | C-14 | MISFRM            | J-14 | AOUT              | P2   | HOLD <sub>2</sub> |

| A-9  | YT <sub>4</sub>   | C-15 | SI                | J-15 | EOUT              | P-3  | RA <sub>6</sub>   |

| A-10 | YT <sub>2</sub>   | D1   | INST <sub>1</sub> | K-1  | NP <sub>4</sub>   | P-4  | RA <sub>7</sub>   |

| A-11 | XMTABTI           | D-2  | CSI               | K-2  | NP <sub>5</sub>   | P-5  | RA₄               |

| A-12 | XMTABTO           | D-3  | INST <sub>0</sub> | K-3  | NP <sub>7</sub>   | P–6  | RA <sub>1</sub>   |

| A-13 | RECEIVE           | D-4  | GUIDE PIN         | K-13 | LSTINC            | P-7  | RBP               |

| A14  | DAVALID           | D-13 | MEDREQA           | K-14 | FRINC             | P-8  | RB <sub>7</sub>   |

| A-15 | FSHRCVF           | D-14 | MEDREQS           | K-15 | S <sub>0</sub>    | P-9  | RB₅               |

| B-1  | R/W               | D-15 | TEST              | L-1  | NP <sub>2</sub>   | P10  | RB₃               |

| B-2  | RESET             | E-1  | DS                | L-2  | NP <sub>3</sub>   | P-11 | RB <sub>1</sub>   |

| B-3  | YR <sub>7</sub>   | E2   | NP <sub>14</sub>  | L-3  | GND               | P-12 | xcu               |

| B-4  | YR₄               | E-3  | GND               | L-13 | X <sub>2</sub>    | P-13 | X5                |

| B–5  | YR₀               | E-13 | GND               | L-14 | ERRINC            | P-14 | vcc               |

| B–6  | YR <sub>3</sub>   | E-14 | INICLBN           | L-15 | S <sub>2</sub>    | P-15 | X1                |

| B–7  | YTP               | E-15 | CLM/BEC           | M-1  | NP <sub>1</sub>   | R-1  | RAP               |

| B-8  | GND               | F1   | NP <sub>15</sub>  | M-2  | NP <sub>0</sub>   | R-2  | RACU              |

| B-9  | YT <sub>5</sub>   | F2   | NP <sub>12</sub>  | M-3  | MINTR             | R-3  | RACL              |

| B-10 | YT <sub>0</sub>   | F-3  | BMODE             | M-13 | TOKISD            | R-4  | NC                |

| B-11 | YT <sub>3</sub>   | F-13 | LNGADR            | M-14 | GND               | R-5  | RA <sub>5</sub>   |

| B-12 | XMEDAVS           | F-14 | XDAMAT            | M-15 | S <sub>3</sub>    | R-6  | RA0               |

| B-13 | XFRBYTE           | F15  | FSVLD             | N-1  | NMINTR            | R-7  | RBCU              |

| B-14 | RCVABTI           | G-1  | NP <sub>13</sub>  | N-2  | HOLD <sub>1</sub> | R-8  | NC                |

| B-15 | RCVABTO           | G–2  | NP <sub>10</sub>  | N-3  | LPBEN             | R-9  | RB <sub>6</sub>   |

| C-1  | INST <sub>2</sub> | G-3  | GND               | N-4  | GND               | R-10 | RB <sub>2</sub>   |

| C-2  | INST <sub>3</sub> | G-13 | XSAMAT            | N-5  | RA <sub>2</sub>   | R-11 | RB₀               |

| C-3  | BCLK              | G-14 | COUT              | N-6  | RA <sub>3</sub>   | R-12 | XCL               |

| C-4  | YR <sub>6</sub>   | G-15 | SDRCVD            | N-7  | vcc               | R-13 | X <sub>6</sub>    |

| C-5  | YRP               | H-1  | NP <sub>11</sub>  | N-8  | RBCL              | R-14 | X4                |

| C6   | GND               | H-2  | NC                | N-9  | GND               | R-15 | X3                |

|      |                   | H-3  | NP <sub>9</sub>   |      |                   |      |                   |

### **PIN DESIGNATIONS**

## (Sorted by Pin Name)

| Pin  |                   | Pin  |                  | Pin  |                 | Pin  | Ī               |

|------|-------------------|------|------------------|------|-----------------|------|-----------------|

| No.  | Pin Name          | No.  | Pin Name         | No.  | Pin Name        | No.  | Pin Name        |

| J-14 | AOUT              | F-13 | LNGADR           | P11  | RB <sub>1</sub> | P-13 | X5              |

| C-3  | BCLK              | N-3  | LPBEN            | R-10 | RB2             | R-13 | X <sub>6</sub>  |

| F-3  | BMODE             | K-13 | LSTINC           | P-10 | RB₃             | N-13 | X7              |

| E-15 | CLM/BEC           | D-13 | MEDREQA          | N-10 | RB <sub>4</sub> | R-12 | XCL             |

| G-14 | COUT              | D-14 | MEDREQS          | P-9  | RB₅             | P-12 | xcu             |

| D-2  | <u>CSI</u>        | M-3  | MINTR            | R-9  | RB <sub>6</sub> | F-14 | XDAMAT          |

| A-14 | DAVALID           | C-14 | MISFRM           | P8   | RB <sub>7</sub> | B-13 | XFRBYTE         |

| E-1  | DS                | N-1  | NMINTR           | N8   | RBCL            | C-11 | XMEDAVA         |

| J-15 | EOUT              | M-2  | NP₀              | R-7  | RBCU            | B-12 | XMEDAVS         |

| L14  | ERRINC            | M-1  | NP <sub>1</sub>  | P-7  | RBP             | A-11 | XMTABTI         |

| K-14 | FRINC             | L-1  | NP <sub>2</sub>  | B-14 | RCVABTI         | A-12 | XMTABTO         |

| A-15 | FSHRCVF           | L-2  | NP <sub>3</sub>  | B15  | RCVABTO         | N-12 | XP              |

| F-15 | FSVLD             | K-1  | NP <sub>4</sub>  | C-10 | RDYTBYT         | G-13 | XSAMAT          |

| C-13 | FULL              | K-2  | NP <sub>5</sub>  | P-1  | READY           | B5   | YR0             |

| H-14 | GND               | J-2  | NP <sub>6</sub>  | A-13 | RECEIVE         | C-7  | YR <sub>1</sub> |

| E-13 | GND               | K-3  | NP <sub>7</sub>  | B-2  | RESET           | A-5  | YR2             |

| B-8  | GND               | J-1  | NP <sub>8</sub>  | K-15 | So              | B-6  | YR₃             |

| G-3  | GND               | H-3  | NP <sub>9</sub>  | J-13 | S <sub>1</sub>  | B-4  | YR4             |

| N-9  | GND               | G-2  | NP <sub>10</sub> | L-15 | S <sub>2</sub>  | A-4  | YR 5            |

| E-3  | GND               | H-1  | NP <sub>11</sub> | M-15 | S <sub>3</sub>  | C-4  | YR6             |

| C-6  | GND               | F-2  | NP <sub>12</sub> | G-15 | SDRCVD          | B-3  | YR7             |

| M-14 | GND               | G-1  | NP <sub>13</sub> | C-15 | SI              | C5   | YRP             |

| N-11 | GND               | E-2  | NP <sub>14</sub> | N-15 | so              | B10  | YT <sub>0</sub> |

| C-8  | GND               | F-1  | NP <sub>15</sub> | D-15 | TEST            | C-9  | YT <sub>1</sub> |

| N-4  | GND               | B-1  | R/W              | M-13 | TOKISD          | A10  | YT <sub>2</sub> |

| C-12 | GND               | R-6  | RA0              | A-1  | vcc             | B-11 | YT <sub>3</sub> |

| H–13 | GND               | P-6  | RA <sub>1</sub>  | N-7  | Vcc             | A-9  | YT4             |

| L-3  | GND               | N-5  | RA <sub>2</sub>  | J-3  | Vcc             | B-9  | YT5             |

| D-4  | GUIDE PIN         | N-6  | RA <sub>3</sub>  | A-7  | Vcc             | A8   | YT <sub>6</sub> |

| N-2  | HOLD <sub>1</sub> | P-5  | RA <sub>4</sub>  | P-14 | Vcc             | A6   | YT <sub>7</sub> |

| P-2  | HOLD₂             | R-5  | RA <sub>5</sub>  | H-15 | Vcc             | B-7  | YTP             |

| E-14 | INICLBN           | P-3  | RA <sub>6</sub>  | N-14 | Χo              | R-4  | NC              |

| D-3  | INST <sub>0</sub> | P-4  | RA <sub>7</sub>  | P-15 | X1              | A3   | NC              |

| D-1  | INST <sub>1</sub> | R-3  | RACL             | L-13 | X <sub>2</sub>  | A-2  | NC              |

| C-1  | INST <sub>2</sub> | R-2  | RACU             | R15  | х3              | R-8  | NC              |

| C-2  | INST <sub>3</sub> | R-1  | RAP              | R-14 | X4              | H-2  | NC              |

|      |                   | R-11 | RB0              |      |                 |      |                 |

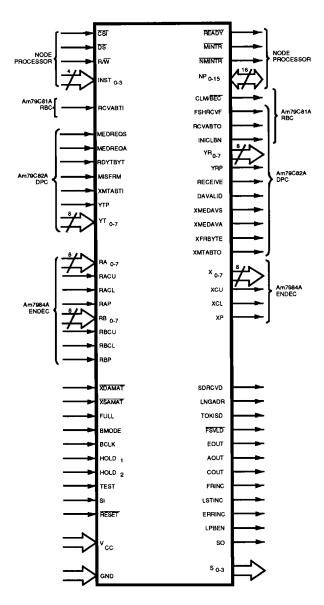

# CONNECTION DIAGRAM 168-Pin PQFP

09731-001A/1

## PIN DESIGNATIONS

## Plastic Quad Flat Package

| Pin |          | Pin |          | Pin |          | Pin |           |

|-----|----------|-----|----------|-----|----------|-----|-----------|

| No. | Pin Name  |

| 1   | NC       | 43  | NC       | 85  | NC       | 127 | NC        |

| 2   | NC       | 44  | NC       | 86  | NC       | 128 | NC NC     |

| 3   | NC       | 45  | NC       | 87  | NC       | 129 | NC        |

| 4   | RESET    | 46  | RCVABTI  | 88  | VCC      | 130 | HOLD1     |

| 5   | BCLK     | 47  | RCVABTO  | 89  | X4       | 131 | HOLD2     |

| 6   | YRP      | 48  | MISFRM   | 90  | X5       | 132 | LPBEN     |

| 7   | YR7      | 49  | FULL     | 91  | X6       | 133 | READY     |

| 8   | YR6      | 50  | GND      | 92  | X7       | 134 | MINTR     |

| 9   | YR5      | 51  | SI       | 93  | XCL      | 135 | NMINTR    |

| 10  | GND      | 52  | TEST     | 94  | GND      | 136 | GND       |

| 11  | YR4      | 53  | MEDREQS  | 95  | XCU      | 137 | NP0       |

| 12  | YR3      | 54  | MEDREQA  | 96  | ΧP       | 138 | NP1       |

| 13  | YR2      | 55  | INICLBN  | 97  | RB0      | 139 | NP2       |

| 14  | YR1      | 56  | CLM/BEC  | 98  | RB1      | 140 | NP3       |

| 15  | YR0      | 57  | FSVLD    | 99  | RB2      | 141 | NP4       |

| 16  | YTP      | 58  | XSAMAT   | 100 | RB3      | 142 | NP5       |

| 17  | YT7      | 59  | XDAMAT   | 101 | RB4      | 143 | NP6       |

| 18  | YT6      | 60  | LNGADR   | 102 | RB5      | 144 | NP7       |

| 19  | vcc      | 61  | SDRCVD   | 103 | RB6      | 145 | NP8       |

| 20  | NC       | 62  | COUT     | 104 | GND      | 146 | vcc       |

| 21  | GND      | 63  | GND      | 105 | GND      | 147 | NC        |

| 22  | GND      | 64  | GND      | 106 | GND      | 148 | GND       |

| 23  | GND      | 65  | GND      | 107 | NC       | 149 | GND       |

| 24  | YT5      | 66  | NC       | 108 | VCC      | 150 | GND       |

| 25  | YT4      | 67  | vcc      | 109 | NC       | 151 | NP9       |

| 26  | YT3      | 68  | AOUT     | 110 | RB7      | 152 | NP10      |

| 27  | YT2      | 69  | EOUT     | 111 | RBCL     | 153 | NP11      |

| 28  | YT1      | 70  | FRINC    | 112 | RBCU     | 154 | NP12      |

| 29  | YT0      | 71  | LSTINC   | 113 | RBP      | 155 | NP13      |

| 30  | RDYTBYT  | 72  | ERRINC   | 114 | RA0      | 156 | NP14      |

| 31  | XMTABTI  | 73  | S0       | 115 | RA1      | 157 | NP15      |

| 32  | NC       | 74  | S1       | 116 | RA2      | 158 | BMODE     |

| 33  | XMTABTO  | 75  | S2       | 117 | RA3      | 159 | DS        |

| 34  | XMEDAVS  | 76  | S3       | 118 | RA4      | 160 | GND       |

| 35  | XMEDAVA  | 77  | GND      | 119 | RA5      | 161 | <u>cs</u> |

| 36  | XFRBYTE  | 78  | TOKISD   | 120 | RA6      | 162 | INST0     |

| 37  | GND      | 79  | so       | 121 | RA7      | 163 | INST1     |

| 38  | RECEIVE  | 80  | X0       | 122 | GND      | 164 | INST2     |

| 39  | DAVALID  | 81  | X1       | 123 | RACL     | 165 | INST3     |

| 40  | FSHRCVF  | 82  | X2       | 124 | RACU     | 166 | R/₩       |

| 41  | NC       | 83  | Х3       | 125 | RAP      | 167 | vcc       |

| 42  | NC       | 84  | NC       | 126 | NC       | 168 | NC        |

### LOGIC SYMBOL

09731-003A

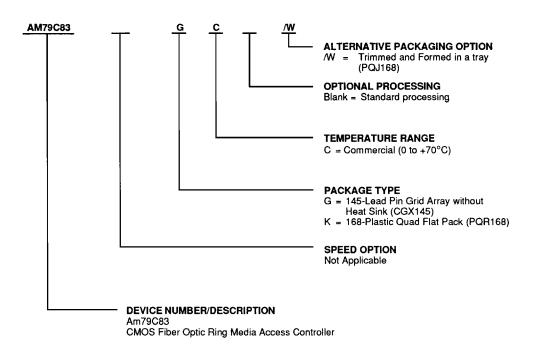

### ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of these elements:

| Valid Combinations |              |  |  |  |  |

|--------------------|--------------|--|--|--|--|

| AM79C83            | GC, KC, KC/W |  |  |  |  |

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

#### PIN DESCRIPTION

#### **RBC** Interface

#### **RCVABTI**

#### Receive Abort In (Input; Active HIGH)

This input indicates that an external event has caused a received frame to be aborted. One such event may be when Buffer Memory is full. The FORMAC will set the C\_indicator on address-recognized frames unless RCVABTI or MISFRM goes HIGH or the FORMAC is forced out of the receive state, as evidenced by RCVABTO being driven HIGH. RCVABTI will cause the FORMAC to drive the RECEIVE, DAVALID, and FSHRCVF outputs LOW and three state the YR-bus until the next frame is received.

#### **DPC Interface**

All output pins which go to the DPC change state synchronously with BCLK. All input pins which are driven by the DPC must be asserted synchronously with BCLK.

#### CLM/BEC

#### Claim/Beacon (Output)

The CLM/BEC pin is used in conjunction with INICLBN. CLM/BEC is a level signal that is HIGH when a claim is required for transmission.

#### DAVALID

#### Data Valid (Output: Active HIGH)

The DAVALID signal indicates that the FORMAC has placed valid data on the YR-bus. If DAVALID is HIGH when RECEIVE is HIGH, the data output to the YR-bus is part of the frame received from the media. If DAVALID is HIGH and RECEIVE is LOW, the data output to the YR-bus represents status information. This occurs on the clock cycle when RECEIVE is brought LOW. DAVALID remains HIGH for an integral number of clock cycles. DAVALID will also go LOW during frame reception when the FORMAC is put on "hold" by a HIGH HOLD; input.

#### **FSHRCVF**

#### Flush Received Frame (Output; Active HIGH)

The FSHRCVF pin is used to inform the RBC and DPC that the frame currently being received should not be copied. FSHRCVF is asserted on two conditions. One condition is when the frame being received is a fragment. This occurs when the FORMAC encounters a non-data symbol in the frame stream before the End Delimiter is encountered. (FSHRCVF will be asserted the cycle prior to RECEIVE going LOW). Alternatively, the FSHRCVF output may indicate the result of the FORMAC address detect comparison. The pin is activated for one BCLK cycle while RECEIVE is HIGH when the destination address (DA) of the received frame does not match the node's own address. This condition is indi-

cated when neither the internal address detect logic nor the XDAMAT input result in a match condition.

#### INICLBN

#### Initialize Claim/Beacon (Output; Active HIGH)

The INICLBN pin is set HIGH for one cycle, indicating a need to issue claim or beacon frames. The type of frame required is determined by the CLM/BEC output. After activating INICLBN, the FORMAC expects the proper frame to be queued for transmission via an S-frame media request (MEDREQS). The claim or beacon should be continuously queued until the FORMAC indicates otherwise. This indication can come in two forms. First, if the FORMAC wishes to switch from issuing claims to issuing beacons (or vise versa), INICLBN will be asserted again. Secondly, if the FORMAC transmit state machine returns to idle, then the FORMAC will assert XMTABTO.

#### **MEDREQA**

#### Media Request Asynchronous (Input; Active HIGH)

The MEDREQA input indicates a DPC request for access to the medium so that A-frames may be transmitted. If MEDREQA is HIGH, MEDREQS is LOW, and the medium is available; then the FORMAC will assert the XMEDAVA line.

#### **MEDREQS**

#### Media Request Synchronous (Input; Active HIGH)

The MEDREQS input indicates a DPC request for access to the medium so that S-frames may be transmitted. If MEDREQS is HIGH and the medium is available then the FORMAC will assert the XMEDAVS line.

#### **MISFRM**

#### Missed Frame (Input; Active HIGH)

Missed Frame is generated by the DPC when frames cannot be copied due to inter-frame gap error. The DPC handles this condition differently from the case of a receive abort. The FORMAC, however, treats these cases identically. The FORMAC will inhibit setting the C\_indicator of the second frame when the MISFRM is received. RECEIVE, DAVALID, and FSHRCVF are dropped and the YR-bus is set to the high-impedance state.

#### **RCVABTO**

#### Receive Abort Out (Output; Active HIGH)

The RCVABTO pin is asserted for one BCLK cycle when the FORMAC receiver is interrupted while the RECEIVE output is HIGH. Such an interruption occurs when the FORMAC transmitter leaves the idle or repeat states due to a network event or an instruction to enter a new state.

#### **RDYTBYT**

#### Ready to Transmit Byte (Input; Active HIGH)

The RDYTBYT is an indication from the DPC that it has filled its internal FIFO and can guarantee transmission of a continuous frame. Normally, RDYTBYT will remain HIGH until the FORMAC receives the entire frame. In case of an abort, it can go LOW before the frame transmission is complete. RDYTBYT must never be HIGH if XMEDAVS and XMEDAVA are both LOW.

#### RECEIVE

#### Receive Frame (Output; Active HIGH)

The RECEIVE signal indicates that a received frame is being sent from the FORMAC to the DPC. Each frame is bound by an active RECEIVE signal. It is set HIGH when the frame control (FC) field is clocked onto the YR-bus. RECEIVE goes LOW one byte after the final byte of the frame's Frame Check sequence (or information field) is sent onto the YR-bus.

#### **XFRBYTE**

#### Transfer Byte (Output; Active HIGH)

The XFRBYTE output is asserted by the FORMAC in response to the RDYTBYT input. It indicates that the FORMAC is ready to read a byte from the YT-bus. XFRBYTE may stay HIGH for one or more cycles. XFRBYTE can go HIGH only if RDYTBYT is asserted.

#### **XMEDAVA**

## Transmit Media Available for Asynchronous (Output; Active HIGH)

The XMEDAVA is a handshake signal between the DPC and FORMAC that is generated when MEDREQA is HIGH and a usable token is captured or held. XMEDAVA is analogous to the XMEDAVS signal. XMEDAVA will not be asserted when XMEDAVS is active (i.e., S-frames take precedent).

#### **XMEDAVS**

## Transmit Media Available for Synchronous (Output; Active HIGH)

The XMEDAVS is a handshake signal between the DPC and FORMAC that is generated in response to both of the following conditions: 1) MEDREQS is HIGH and a usable token is captured or held, or 2) MEDREQS is HIGH and the FORMAC has received an ILDSNDM instruction. XMEDAVS goes LOW after the frame is transmitted (end of frame is signified by the RDYTBYT input going LOW). If the MEDREQS remains HIGH and the FORMAC determines that another transmission opportunity exists, the XMEDAVS will go HIGH again in the next clock cycle.

#### **XMTABTI**

#### Transmit Abort In (Input; Active HIGH)

If an abort is initiated through the DPC, then MEDREQS, MEDREQA, and RDYTBYT are set LOW. One cycle later, the XMTABTI pin is asserted. Upon detecting XMTABTI HIGH, the FORMAC aborts the outgoing frame by ensuring that the FCS and FS fields are not appended to the frame.

#### **XMTABTO**

#### Transmit Abort Out (Output; Active HIGH)

XMTABTO is generated when the FORMAC exits the claim/beacon mode.

#### YR0-7

#### Y Receive Bus (Output; Three State)

The YR-bus is used to transfer data received from the media to the DPC. The YR-bus is also used to send status information to the DPC at the end of a frame transfer. The YR-bus is active when either the RECEIVE or DAVALID outputs are HIGH.

When the FORMAC receives a frame from the media and the transmitter is in the idle or repeat state (in half-duplex mode), the YR-bus is enabled and the RECEIVE line is set HIGH. DAVALID is asserted as the data is sent to the Y-bus. In full-duplex mode, YR is always configured for output. Frames received from the media are presented on the YR-bus regardless of the transmitter state.

Status information is also passed over the YR-bus. The received frame's status is stored as a byte in the FOR-MAC, appended to the end of the frame and output to the Y-bus. The FORMAC indicates this status byte with a special handshake. When the status is placed on the bus, DAVALID is set HIGH while RECEIVE remains LOW.

#### **YRP**

## Y Receive Bus Parity (Output; Three State, Active HIGH)

YRP indicates odd parity on the YR-bus. This signal changes state at the same time as the YR-bus.

#### YT0-7

#### Y Transmit Bus (Inputs)

The YT-bus carries data to be transmitted on the media from the DPC to the FORMAC. The YT-bus interfaces to Y-bus of the DPC. In a half-duplex system, the YT input and YR output bus share the Y-bus of a common DPC. Data for transmission is passed to the FORMAC over the YT-bus synchronous to the BCLK. Data flow is controlled using a two-wire handshake. When the DPC is ready to transmit data, it sets the RDYTBYT line HIGH. When the FORMAC is ready to receive the frame, the XFRBYTE line is set HIGH.

#### **YTP**

### Y Transmit Bus Parity (Input; Active HIGH)

The YTP signal indicates odd parity on the YT-bus.

#### **ENDEC Interface**

The following sections describe the pins used to interface the FORMAC with the Am7984A ENDEC. All outputs to the ENDEC are driven synchronously with BCLK. All inputs must change state synchronously with BCLK.

#### **RA**0-7

#### Receive Bus A (Inputs)

The RA-bus is used to receive information from an EN-DEC. Bytes are clocked into the FORMAC RA-bus synchronously with BCLK.

#### **RACL**

#### Receive A Control Lower (Input; Active HIGH)

The RACL is driven HIGH to indicate that the lower nibble of the RA-bus (RAo-3) is a network control character.

#### RACU

#### Receive A Control Upper (Input; Active HIGH)

RACU is driven HIGH to indicate that the upper nibble of the RA-bus (RA4-7) is a network control character. When RACU is LOW, this nibble contains data.

#### RAP

#### Receive A Parity (Input; Active HIGH)

The RAP input reflects odd parity on the RAo-7, RACU, RACL, and RAP lines. If the number of "1s" on RAo-7, RACU, and RACL is odd, then RAP will be logic "0".

#### RB0-7

#### Receive Bus B (Inputs)

The RB-bus is used to receive information from an EN-DEC. Bytes are clocked into the FORMAC RB-bus synchronously with BCLK.

#### RBCL

#### Receive A Control Lower (Input; Active HIGH)

The RBCL is asserted to indicate that the lower nibble of the RB-bus (RBo-3) is a network control character. RBCL is synchronous with the BCLK.

#### RBCU

#### Receive B Control Upper (Input; Active HIGH)

RBCU is asserted to indicate that the upper nibble of the RB-bus (RB4-7) is a network control character. When RBCU is LOW, this nibble contains data. RBCU is synchronous with the BCLK.

#### RBP

#### Receive B Parity (Input; Active HIGH)

The RBP input reflects odd parity on the RBo-7, RBCU, RBCL, and RBP lines. If the number of "1s" on RBo-7, RBCU, and RBCL is odd, then RBP will be logic "0".

#### X0-7

#### **Transmit Bus (Outputs)**

This output bus is used as a path for control and data information which will be transmitted over the medium through the ENDEC.

#### XCL

#### Transmit Control Lower (Output; Active HIGH)

The XCL output signal is used to identify control symbols on the lower nibble of the transmit bus. If XCL is HIGH, the lower nibble of the X-bus is interpreted as a network control character. Otherwise, it is interpreted as a data nibble.

#### **XCU**

#### Transmit Control Upper (Output; Active HIGH)

The XCU output signal is used to flag control symbols on the upper nibble of the transmit bus. If XCU is HIGH, the upper nibble of the X-bus is interpreted as a network control character. Otherwise, it is interpreted as data nibble

#### ΧP

#### Transmit Parity (Output; Active HIGH)

This signal reflects odd parity on the X<sub>0-7</sub>, XCU, XCL, and XP lines. If the number of "1s" on X<sub>0-7</sub>, XCU, and XCL is odd, then XP will be logic "0".

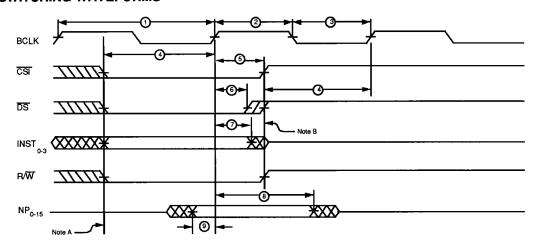

#### **Node Processor Interface**

All inputs from the Node Processor (NP) must be asserted synchronously with BCLK unless the FORMAC is in asynchronous mode (BMODE pin is LOW). All outputs to the NP change state synchronously with BCLK.

#### CSI

Am79C83

#### Chip Select Input (Input; Active LOW)

$\overline{\text{CSI}}$  enables read and write operations to the FORMAC. It is logically "ANDed" with the  $\overline{\text{DS}}$  line to enable transmit logic of the FORMAC. In synchronous mode  $\overline{\text{CSI}}$  must stay LOW one BCLK cycle longer than  $\overline{\text{DS}}$ .

#### $\overline{\mathsf{DS}}$

#### Data Strobe (Input; Active LOW)

This signal is logically "ANDed" with the  $\overline{CSI}$  line. The  $\overline{DS}$  input is part of the handshake between the NP and FORMAC when the FORMAC acts as bus slave. This input signal is set by the Node Processor to frame the data transfers between the NP and the FORMAC. The direction of the data transfer is dictated by the status of the  $\overline{NW}$  line. The NP sets  $\overline{DS}$  LOW, initiating a data transfer. The FORMAC reacts asynchronously to this signal when BMode is LOW.

#### INST<sub>0-3</sub>

#### Instruction 0-3 (Inputs)

The instruction input lines allow direct access to the FORMAC internal registers. These lines are used to place the FORMAC into different operating states. The instruction timing has been designed so that INSTo-3 can be tied to the address bus of a conventional microprocessor.

#### MINTR

## Maskable Interrupt (Output; Open Drain, Active LOW)

The MINTR output of the FORMAC is an attention line that indicates, when LOW, the status of one or more unmasked flags in the status registers.

#### **NMINTR**

## Non-Maskable Interrupts (Output; Open Drain, Active LOW)

The NMINTR output of the FORMAC is an attention line that indicates, when LOW, that one or more non-mask-able interrupt conditions have occurred.

#### $NP_{0-15}$

## Node Processor Data Bus (Input/Output; Three State)

The NP-bus is a 16-bit wide bidirectional data bus used to interface the FORMAC to the NP. Data transfer on the NP-bus can be synchronous or asynchronous depending upon the setting of the BMODE pin. For asynchronous operation, a two-wire handshake is provided through the  $\overline{\text{READY}}$  and  $\overline{\text{DS}}$  lines.

#### R/W

#### Read/Write (Input)

This pin allows the NP to read from or write into internal registers of the FORMAC.

#### READY

#### Ready (Output; Open Drain, Active LOW)

The READY output is used in the handshake between the NP and FORMAC. The FORMAC READY output provides an asynchronous acknowledgment to the NP that a data transfer is complete. The FORMAC asserts READY when it has put data onto the NP-bus during a read cycle or is about to take data off the NP-bus during

a write cycle. READY is a response to the DS and will return HIGH after the DS signal goes HIGH.

## Clocks, Control, and Special-Function Interfaces

#### **AOUT**

#### Address Indicator (Output; Active HIGH)

AOUT identifies the state of the A\_indicator which is received from frames whose source address match the local address. AOUT is HIGH for set indicators and LOW for indicators received as reset or not received. The state of EOUT is only meaningful when the FSVLD output is asserted. EOUT, AOUT, and COUT will retain their values until the next Start Delimiter is received. This allows simple latching of these status bits on the falling edge of FSVLD.

#### **BCLK**

#### Byte Clock (input)

The BCLK is the clock that runs the media access logic in the FORMAC. Data transmitted to and received from the ENDEC interface is synchronous to BCLK.

#### **BMODE**

#### **Bus Mode (Input)**

The BMODE input is strapped HIGH for synchronous operation of the NP-bus. A LOW level allows asynchronous operation of the NP-bus.

#### COUT

#### Copy Indicator (Output; Active HIGH)

COUT identifies the state of the C\_indicator received from frames whose source address match the node's address. COUT is HIGH for set indicators and LOW for indicators received as reset or not received. The state of COUT is only meaningful when the FSVLD output is asserted. EOUT, AOUT, and COUT will retain their values until the next Start Delimiter is received. This allows simple latching of these status bits on the falling edge of FSVLD.

#### **EOUT**

#### Error Indicator (Output; Active HIGH)

EOUT identifies the state of the E\_indicator received from frames whose source address match the node's address. EOUT is HIGH for set indicators and LOW for indicators received as reset or not received. The state of EOUT is only meaningful when the FSVLD output is asserted. EOUT, AOUT, and COUT will retain their values until the next Start Delimiter is received. This permits simple latching of these status bits on the falling edge of FSVLD.

#### **ERRINC**

#### Error Counter Increment (Output; Active HIGH)

ERRINC is synchronous with BCLK and remains HIGH for one BCLK cycle. ERRINC indicates reception of an

invalid FDDI frame (invalid data length or CRC) where the error indicator was not set by a previous station. This output can be used to increment a counter for the collection of ring statistics.

#### **FRINC**

#### Frame Counter Increment (Output; Active HIGH)

FRINC is synchronous with BCLK and remains HIGH for one BCLK cycle. FRINC indicates reception of a symbol stream which conforms to the FDDI frame format. FRINC can be used to increment an external counter for collection of ring statistics.

#### **FSVLD**

#### Frame Status Valid (Output; Active LOW)

This pin is used to indicate that valid status information is presented on the EOUT, AOUT, and COUT pins.  $\overline{\text{FSVLD}}$  is asserted when a frame whose source address equals the local address is received. This match is determined by either the internal address detection logic or the  $\overline{\text{XSAMAT}}$  input.  $\overline{\text{FSVLD}}$  as well as the EOUT, AOUT, and COUT indicators are asserted on the second cycle after the End Delimiter is received on the Rbus. The rising edge of  $\overline{\text{FSVLD}}$  can be used to clock EOUT, AOUT, and COUT into a register.

## FULL Full Duplex (Input; Active HIGH)

During normal operation, RECEIVE cannot go HIGH while the transmit state machine is in the transmit data, claim, or beacon states. The FULL pin overrides this requirement and is useful for implementing a full-duplex system.

#### HOLD<sub>1</sub>

#### Hold One (Input; Active HIGH)

HOLD<sub>1</sub> acts as a suspend/resume feature. When HOLD<sub>1</sub> is asserted, the FORMAC receive state machines and the internal pipelines will hold their present values. Bytes received during the cycle following HOLD<sub>1</sub> assertion are ignored. If the chip is transmitting or receiving on the Y-bus, HOLD<sub>1</sub> will also cause XFRBYT and/or DAVALID to go LOW. The TVX timer will be held and frame transmission suspended as a result of HOLD<sub>1</sub>. No other timers are affected by HOLD<sub>1</sub>.

#### HOLD<sub>2</sub>

#### Hold Two (Input; Active HIGH)

HOLD<sub>2</sub> holds the current state of the THT and TRT timers.

#### **LNGADR**

#### Long Address (Output; Active HIGH)

The LNGADR output becomes valid during the BCLK cycle after the SDRCVD pin is asserted. The LNGADR output value will hold until the next Start Delimiter is received. LNGADR is asserted if the frame's frame-control field indicates a 48-bit address. The LNGADR output is used in conjunction with the SDRCVD signal to support external address detection and token discrimina-

tion. Upon reception of a token, the LNGADR output will be HIGH if the frame-control field identifies the token as a restricted token.

#### LPBEN

#### Loopback Enable (Output; Active HIGH)

LPBEN is asserted when the FORMAC enters loopback mode. This pin is provided to support configurations using external hardware to store loopback frames.

#### LISTING

#### Lost Counter Increment (Output; Active HIGH)

LSTINC is synchronous with BCLK and remains HIGH for one BCLK cycle. LSTINC indicates reception of a non-data, non-End Delimiter symbol pair in the midst of frame. LSTINC can be used to increment an external counter for collection of ring statistics.

#### RESET

#### Reset (Input: Active LOW)

RESET is an asynchronous input which initializes the internal FORMAC state machines and registers. It must be held LOW for at least four BCLK cycles.

#### S0-3 Status Receive (Outputs)

The S pins indicate the type of frame received by the FORMAC (regardless of destination or source address match). The bit assignment is as follows:

| S <sub>3</sub> | S <sub>2</sub> | S <sub>1</sub> | So | Description                    |

|----------------|----------------|----------------|----|--------------------------------|

| 0              | 0              | 0              | 0  | Quiescent                      |

| 0              | 0              | 0              | 1  | Claim frame                    |

| 0              | 0              | 1              | 0  | Beacon frame                   |

| 0              | 0              | 1              | 1  | Other MAC frame                |

| 0              | 1              | 0              | 0  | NSA frame                      |

| 0              | 1              | 0              | 1  | Other SMT frame                |

| 0              | 1              | 1              | 0  | Implementor frame              |

| 0              | 1              | 1              | 1  | Reserved                       |

| 1              | 0              | 0              | 0  | Pass TokenUnrestricted         |

| 1              | 0              | 0              | 1  | Pass Token-Restricted          |

| 1              | 0              | 1              | 0  | Capture Token—<br>Unrestricted |

| 1              | 0              | 1              | 1  | Capture Token—Restricted       |

| 1              | 1              | 0              | 0  | Reserved                       |

| 1              | 1              | 0              | 1  | Reserved                       |

| 1              | 1              | 1              | 0  | Reserved                       |

| 1              | 1              | 1              | 1  | PH_Invalid Received            |

The S pins are set to logic "0" upon reset. They remain in this state until a frame is received from the ring. After the frame status field is received, the code corresponding to the frame type is driven onto the S pins for one BCLK cycle. PH\_Invalid is output upon receipt of the PH\_Invalid symbol from an ENDEC. PH\_Invalid is indicated by all "1s" on the upper nibble of the selected R-bus with the upper and lower control input held HIGH. These pins can be used by the NP in conjunction with external RS flip-flops.

#### **SDRCVD**

#### Start Delimiter Received (Output; Active HIGH)

The SDRCVD output is asserted after a Start Delimiter (JK) is received at the FORMAC input. The signal remains HIGH for one clock cycle. The SDRCVD pin is used to support external address detection.

#### SI

#### Shift In (Input)

The SI pin provides an input path for serial shift scan diagnostics. This pin must be left unconnected for normal operation.

#### SO

#### Shift Out (Output)

SO is the output for shift scan diagnostic data while in TEST mode. This pin must be left unconnected for normal operation.

#### **TEST**

#### Test Mode (Input; Active HIGH)

The TEST pin is used for factory and incoming testing of FORMAC. This pin must be strapped to ground for normal operation.

#### TOKISD

#### Token Issued (Output; Active HIGH)

The TOKISD pin indicates that the FORMAC issued a restricted or non-restricted token. The pin goes HIGH for

one BCLK cycle when the token End Delimiter is placed on the X-bus.

#### **XDAMAT**

## External Destination Address Match (Input; Active LOW)

This input provides a means for additional destination address detection outside of the FORMAC. In order to ensure proper setting of the A\_indicator and correct FSHRCVF operation, XDAMAT assertion must occur during a specific window of the frame arrival on the R-bus. This window begins on the third byte following the frame start delimiter and ends on the fifth byte of the information field.

#### **XSAMAT**

## External Source Address Match (Input; Active LOW)

This input provides a means for additional source address detection outside of the FORMAC. XSAMAT causes the received frame to be stripped from the ring. When XSAMAT is asserted, the byte present on the R-bus at the time of assertion and all following bytes of the frame will be stripped from the ring. This pin should be tied HIGH when external address detection is not used.

### **Power Supply**

#### **GND**

#### Ground (inputs)

There are fourteen GND pins. They must all be connected to the power return.

#### Vcc

#### Power (Inputs)

There are six Vcc pins. They must all be connected to a +5-V±5% supply.

#### **FUNCTIONAL DESCRIPTION**

### **Overview of User-Accessible Resources**

#### **Programmable Resources**

Several registers in the FORMAC can be accessed through the NP-bus. Through initialization of these registers, the user can tailor the device to fit a particular application. The instruction bus (R/W, INSTo-3) is used as a pointer to select the various internal registers.

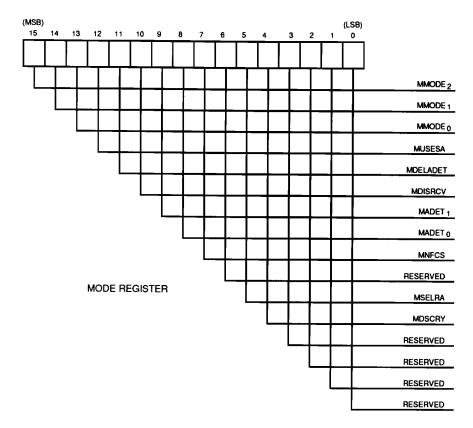

#### Mode Register (MODE)

The FORMAC contains a 16-bit mode register. When reset, the mode register is initialized so that all bits (except MSELRA) are inactive (LOW). The NP can access the mode register using the ILDMODE and IRDMODE instructions.

#### Address Registers (ADRSo-7)

The FORMAC address registers store the node's 48-bit address, 16-bit individual and 16-bit group address, and the station T\_Request time value. These registers are organized in a 8-by-16-bit structure that is loaded and read sequentially through the ILDADRS and IRDADRS instructions.

#### MAC Information Register 1-0 (MIR<sub>1-0</sub>)

The MIR is a read-only register. MIR is used to store the first four bytes of the information field of received MAC frames. MIR is also used to store the first four information bytes of a frame in loopback mode. It can be read with the IRDMIR<sub>1</sub> and IRDMIR<sub>0</sub> instructions.

#### Token Rotation Timer (TRT)

The TRT is used to implement the timed token access protocol specified by FDDI and determine certain error conditions on the ring. It can be read from or written to under processor control. The upper 16 bits of the TRT timer can be read directly with the IRDTRT instruction. The lower 5 bits are read with the IRDTLSB instruction. A single instruction, ILDTRT, loads the entire 21-bit TRT register, filling the upper 16 bits with the value stored in TMAX and writing "0s" into the lower 5 bits.

#### Timer Default Maximum (TMAX)

TMAX specifies the default token rotation time to be used during ring initialization and recovery. It is also used to hold a default TRT (TMAX) during the claim token process. This 16-bit register is loaded using the ILDTMAX instruction and read using IRDTMAX.

#### Valid Transmission Timer (TVX)

The 8-bit TVX counts the time between valid frame transmissions on the ring. If the time exceeds the value

loaded into TVX at initialization, then ring recovery will occur. Loading TVX (using the ILDTVXD instruction) writes the default number into a latch. Reading TVX (using the IRDTVXT instruction) places the TVX timer value on the most-significant byte of the NP-bus, and the previously written latch value on the least-significant byte of the NP-bus.

#### Negotiated Token Rotation Time (TNEG)

This 21-bit register stores the lowest 21 bits of the bid field of a received Higher Claim or My Claim frame. When the ring becomes operational, this register represents the winning value of the claim process. The upper 16 bits of TNEG can be read with the IRDTNEG instruction. The lower 5 bits are read with the IRDTLSB instruction.

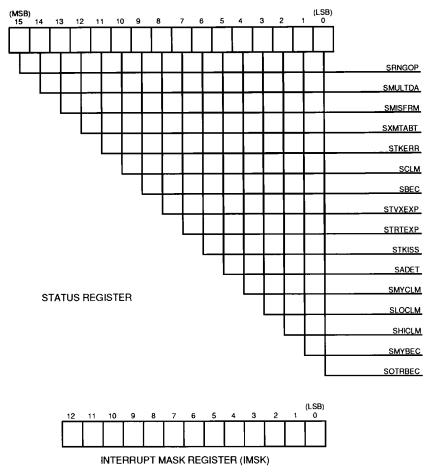

#### Status Register (STAT)

STAT is used to report error and operational conditions to the NP. Individual bits in the status register can be used to generate interrupts to the NP. Status is a read-only register which can be read using the IRDSTAT instruction.

#### Interrupt Mask Register (IMSK)

The FORMAC contains a 13-bit register used to control maskable interrupts. This register can be written and read via the NP-bus using the ILDIMSK and IRDIMSK instructions.

#### Frame Status Register (FRSTAT)

Frame status is generated and appended to the end of all frames when they are transferred to the YR-bus. Frame status is recognized by the DPC through a special handshake sequence. The DPC stores this byte (as external status) in the received frame header in the Buffer Memory.

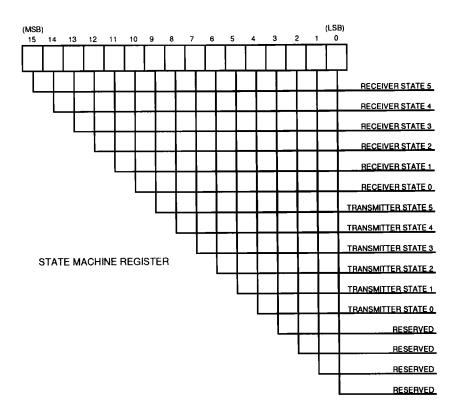

#### State Machine Register

The state machine register is a read-only register that contains the states of the machines as described in the FDDI MAC protocol specifications. It can be read using the IRDSTMC instruction and the NP-bus.

#### Asynchronous Priority Register (TPRI)

The TPRI register is used to control the priority of asynchronous messages. The value of TPRI is compared with TRT or THT. This register can be loaded from the NP-bus with an ILDTPRI instruction or read with an IRDTPRI instruction.

#### Instruction Set

The NP can issue software instructions to the FORMAC using the INST<sub>0-3</sub>,  $R/\overline{W}$  and NP<sub>0-15</sub> lines. INST<sub>0-3</sub> are normally connected to the address bus of the NP.

#### **Hardwired Resources**

The FORMAC provides two strap options that configure the FORMAC for special functionality. The FULL pin is used to select full-duplex operation at the FORMAC Y interface. The BMODE input can be strapped to Vcc for synchronous operation of the NP-bus.

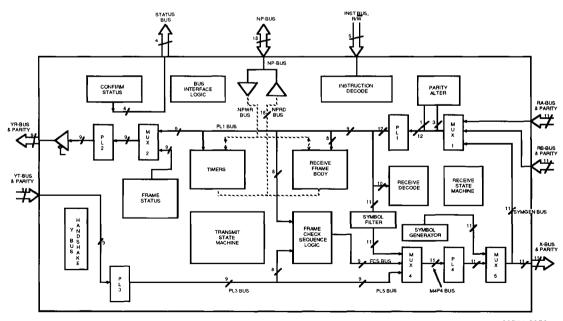

#### **Block Diagram**

#### **External Buses**

Seven buses are provided to interface the FORMAC with external hardware. The NP-bus provides a path for initialization and control of the chip. Associated handshake logic permits asynchronous communication over the NP-bus. The NP-bus can also be programmed for synchronous operation.

The two Y-buses are used to interface to the DPC. The YR-bus is the output for frames received from the media. The YT-bus is the input for data to be transmitted on the medium. Y-bus handshake logic provides control signals for data flow between devices. In addition, data on both YR- and YT-buses is protected with a parity signal.

The RA-, RB-, and X-buses comprise the FORMAC interface with the physical layer. Data received from the media is input via the selected R-bus. A MUX at the input of the FORMAC permits selection of the active R input bus. Data is sent to the media over the X-bus. Again, parity is provided on both buses.

Finally, an instruction bus input (R/W, INSTo-3) is used to select between read and write operations on the different registers within the chip.

#### MUX1

A MUX is provided at the input to the FORMAC to select the input to the receiver logic of the chip. Under normal operation, the MUX is used to select one of the R-buses as an input to the FORMAC. A HIGH MSELRA bit in the mode register selects the RA-bus as the chip input. MSELRA LOW selects RB. This control is provided to facilitate ring re-configuration.

There is a case when neither R-bus is used as the FOR-MAC input from the media. This occurs when the FOR-MAC is programmed for internal loopback; the FOR-MAC X-bus is used as the input to the chips internal receive path. This is useful for "in-circuit" testing of the FORMAC and associated hardware before a station is placed on the ring. When internal loopback is selected, data input on the RB- and RA-buses is ignored.

Figure 1. FORMAC Detailed Block Diagram

09731-005A

#### Pipeline1

Pipeline1 captures received data and brings it onto the internal PL1- bus. This latching allows appropriate setup time for decoding the frame control and address field of incoming frames.

#### **Parity Alter**

The parity alter logic changes the parity system used by the FORMAC. Odd parity is normally used on the selected R-bus, RCU, and RCL input signals. This parity system is altered to reflect odd parity on only the R-bus information, by setting input parity based on the state of the RCU and RCL signals. Thus, bad parity received on the RP input will yield bad parity output from this logic.

#### Receive Frame Logic

This block of logic consists of three basic elements. First a decoder is provided to interpret the frame control and other special symbols in the incoming frames. Frame validity logic within this block checks each frame against the FDDI criteria. Finally, the receive state machine is included in this block. The receive frame block provides many of the global signals used throughout the chip.

#### Receive Frame Body Logic

This logic sets the flags required for address detection and token claiming. The addresses and requested token time associated with the FORMAC are stored in registers within this block. An ALU compares these stored values with the address and T\_Bid\_Rc fields of received frames. A state machine within the block selects the proper address for comparison. The receive frame body logic uses the inputs from the receive frame logic block to determine the type of address being received (i.e., long/short, individual/group). The flags that are set by this block are used by the transmit state machine and the symbol generator. The flags are also input to the Ybus handshake block where they are used to generate some of the FORMAC-DPC interface signals.

#### **Timers**

The timer block contains the timers and registers required for the timed token protocol of FDDI. Three timers are contained within this block. The TVX timer is used to check the time between End Delimiters on the ring. Should TVX exceed the value programmed by the user, ring recovery is initiated through the claim process. The TVX timer is an 8-bit timer clocked once per 255 clock cycles. The TVX timer is loaded with the 8-bit TVX default value every time a valid frame of unrestricted token is received by the FORMAC. An instruction is provided to force the default value into the timer. The timer is also loaded each time the mode register is programmed to exit initialization mode.

The TRT timer counts the time between receipt of tokens. If the TRT exceeds 2 times the operative token rotation time (2 x TOPR) for the network, recovery action is required. When the ring is operational, TOPR will be the time negotiated through the claim process and is stored in TNEG. During ring initialization and recovery, TOPR is equal to the default value called TMAX. TMAX can be loaded directly via the NP-bus. Loading of TRT with TMAX can also be forced by an instruction. In addition, TRT is loaded with TMAX everytime the FORMAC is programmed to exit the initialization mode.

The third timer, the THT or token holding timer, controls the length of time that the node can hold a token for the purpose of transmitting A-frames, Functionally, THT can be thought of as a down counter. THT is loaded when the FORMAC captures a token. The value loaded is the difference between the time the FORMAC expected to capture a token (TOPR) and the actual time it took for the token to circulate the ring. If this is greater than the value loaded into TPRI (i.e., the token was received sooner than expected), the FORMAC can transmit asynchronously. The FORMAC can continue to transmit A-frames until the THT falls below the TPRI value. Both TRT and THT are implemented as 21-bit counters providing one BCLK resolution.

#### Bus Interface Logic

This block of logic controls the handshake pins required to interface the FORMAC with the NP.

#### Instruction Decode

The instruction decode logic decodes the instruction bus. The decoded outputs are used internally as pointers and control signals.

#### Status/Mode/Interrupts

This block is comprised of the status, mode, and interrupt logic. The status logic allows for error reporting to the NP. This status information can be read directly or reported using maskable and non-maskable interrupts. The mode register allows the NP to control the operation of the FORMAC.

#### Frame Status

This block is used to map the frame status (FS) of a received frame and other pertinent information into an 8-bit register. The R and S symbols received after the End Delimiter of the frame are decoded as a zero and one, respectively. The contents of the frame status register are appended to the receive frame and passed to the DPC.

#### MUX2

MUX2 is used to append the frame status byte to the frame being sent out to the Y-bus. The MUX will output data from the PL1-bus, while received FC and INFO data is contained internally. After the last byte of information has passed through the MUX, it will switch to select the receive frame status register.

#### Pipeline2

Pipeline2 latches the received frame information being sent out on the Y-bus. This ensures sufficient setup time at the FORMAC-DPC interface.

#### **Confirmation Status**

This block is used to confirm the received status of frames originating at the station associated with the FORMAC.

#### Transmit State Machine

This block implements the transmit state machine outlined in the FDDI MAC specification.

#### Y-bus Handshake

The Y-bus handshake logic controls all signals required to interface the FORMAC to the DPC.

#### Pipeline3

This pipeline latches frames before they are transmitted onto the FORMAC internal transmit path. This allows adequate setup time for the frame check sequence logic.

#### Frame Check Sequence (FCS)

This logic checks the FCS of received frames and generates FCS for transmitted frames. A MUX steers either the PL1 (internal receive) or the PL3– (internal transmit) bus into the CRC logic. The MUX normally selects the PL1-bus when the FORMAC is in the repeat or idle modes. When the FORMAC enters one of the transmit states, PL3 is selected. The CRC is calculated using a 32-bit Autodin II polynomial as specified by the FDDI MAC specification.

#### MUX4

MUX4 selects one of three different sources to be output on the X-bus. These sources are the output of the symbol filter, the FCS logic, and the PL3-bus.

#### Symbol Filter

The symbol filter logic alters the  $E_{\_}$ ,  $A_{\_}$ , and  $C_{\_}$  indicators on repeated frames as specified by the FDDI standard.

#### Symbol Generator State Machine

This logic generates the command symbols required for transmission on the media. These include idle symbols for preamble, as well as the set/reset and End Delimiter symbols appended to transmitted and repeated frames. This logic is also used to generate the tokens when they are issued.

#### MUX5

MUX5 selects between the internal transmit and repeat paths and the symbol generator output for transmission onto the X-bus.

#### Pipeline4

Pipeline4 guarantees ENDEC setup time.

### **Operational Modes**

This section describes the various control tasks performed by the FORMAC. The operation is broken down to three basic modes. Initialization mode is entered upon reset. On-line enables the receive and transmit state machines for operation on the ring. The four modes of loopback permit node self-test before entering the on-line state. Selection of these modes is performed through the mode register.

#### Initialization

The initialization mode is indicated by three zeros in the MMODE bits in the mode register. This mode is automatically entered on a pin or software reset. In this mode, the receive and transmit state machines are locked in the reset condition. The network data path is locked in a "blind repeat" configuration. In this fashion, data input to the selected R-bus is repeated on the X-bus with no protocol processing.

The FORMAC address registers can only be written and read properly with the chip in initialization mode. Although the timer default values can be written in any mode, changing these ring parameters while on-line may lead to undeterministic behavior. Network events can occur asynchronous to the loading of the registers. The timers can be loaded with the default at any time. The user cannot determine if the timer is operating with the new or old default time.

During initialization mode, no receiver protocol is executed. When the chip is placed in this mode, certain ring events such as claim or beacon frames may be missed. Thus, a FORMAC leaving the initialization mode may not be operating with current parameters such as the negotiated token rotation time for the ring. Also, the Claim/Listen and Beacon/Listen instructions do not operate in the initialization mode.

Even though the transmit state machine will not process the information, the internal timers (TRT and THT) continue to operate. This permits rough timer checkout before going on-line. On reset, TVX is loaded with its terminal count value. This timer, during non-initialization operations, will expire in 255 clock cycles. Status is set accordingly. TVX will stop once expired until it is reloaded.

TRT and THT are cleared on reset. They expire in  $2_{21}$  BCLK cycles. THT will stop when the terminal count is reached. TRT will reload with the current TMAX value and resume counting.

All counters resume sequencing when reloaded. Reloading can be forced with the instruction commands provided. These instructions can be used with the timer expiration bits in the status register to verify timer operation against "soft" timers during power on confidence testing of the node hardware. It should also be noted that the timers are loaded with their default values when the Mode register MMODE bits are programmed to exit the initialization mode.

#### On-Line

The on-line mode is entered by writing the appropriate bit pattern to the MMODE bits. When this mode is entered, the FORMAC performs the operational sequences required for the FDDI. The chip exits the online mode if the MMODE bits are altered or a chip reset occurs. The on-line sequences can be examined further by investigating the functions of the chips receiver and transmitter.

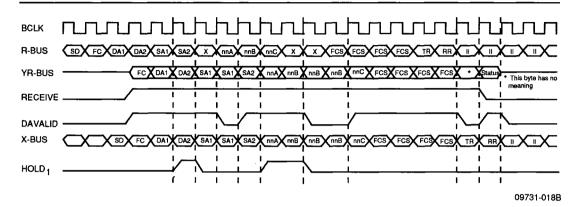

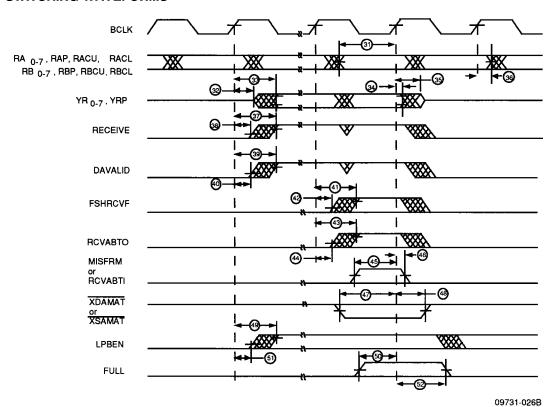

#### Receiver

When "on-line" the FORMAC continually processes the incoming symbol stream as per the FDDI receiver state machines. The actions of the receiver can be further categorized. The fundamental actions are frame reception and frame repetition control. The receiver also con-

trols some special function outputs that are used to log ring statistics, support external addressing and provide general status information.

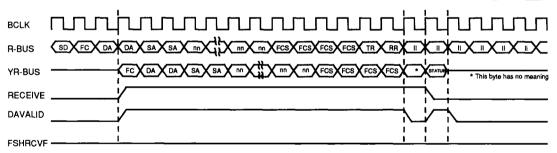

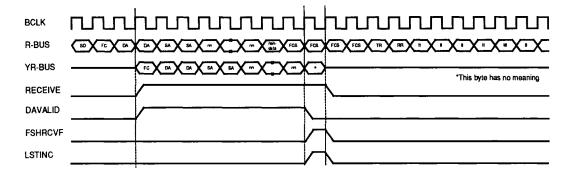

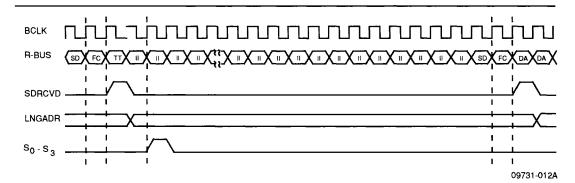

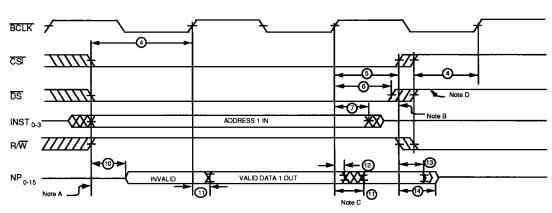

Frame Reception. Frame reception refers to the action of placing network data on the YR-bus and setting the control signals on the bus accordingly. There are four basic actions that can occur when the head of a frame is received from the selected R-bus. First, normal frame reception can occur. This case is illustrated in Figure 2. Here the RECEIVE and DAVALID outputs from the FORMAC go HIGH as the YR-bus is activated. DAVALID goes LOW after the last byte of the frame is output. RECEIVE stays HIGH. In the next cycle, DAVALID goes HIGH while RECEIVE drops, indicating that the contents of the frame status register have been placed on the YR-bus.

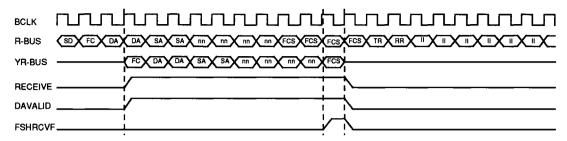

The second case of frame reception is the flushed frame. There are two criteria for flushing a frame. First, flush occurs at the end of a properly formed frame when the address matching criteria are not met. The address match criteria includes the internal and external address match decisions and the state of the MDELADET and MADET bits in the mode register. The frame will also be flushed if the frame ends on an uneven byte boundary. Figure 3 illustrates a case of a flush due to an address mismatch. If no valid address match occurs (either internal or external) by the fifth byte of the frame following the SA (when MDELADET = 0), FSHRCVF is asserted.

Figure 2. Normal Frame Reception

09731-006B

(Case A) Flush on Address Mismatch: frame with 5 or more data bytes following SA field boundary and MDELADET = 0

(Case B) Flush on Address Mismatch: less than 5 data bytes following SA field boundary or when 5 or more data bytes follow SA field and MDELADET = 1

09731-007B

Figure 3. Flush Cases A and B

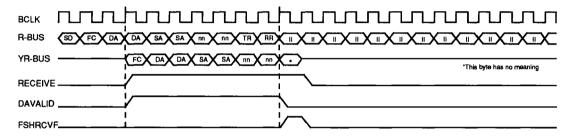

FSHRCVF is also asserted during reception of a stripped or lost frame. Stripped frames are frames that were partially repeated by a node. Before the End Delimiter is repeated, the node began to transmit idle. The resultant symbol stream is referred to as a stripped frame. A lost frame is one whose symbol stream is corrupted so that a symbol encountered after the Start Delimiter results in a non-data, non-End Delimiter symbol. These frames are flushed in a similar fashion to the stripped frame case. This is illustrated in Figure 4.

The next case that needs to be examined are those of non-reception. In these cases, the RECEIVE, DAVALID and YR-bus outputs never go active. In order to activate these signals, the receive state machine must be in the awaiting SD state. A valid Start Delimiter followed by two data symbols must be received. The two data sym-

bols are interpreted as the frame control (FC) field. If FC indicates a claim frame or token, frame reception will not occur. If all criteria have been met, the state of the transmitter must be considered. The transmitter must be in the idle or repeat states for frame reception. The only exception is when the FULL strap option is tied HIGH. Finally, reception will not occur if the mode register is programmed to disable receive.

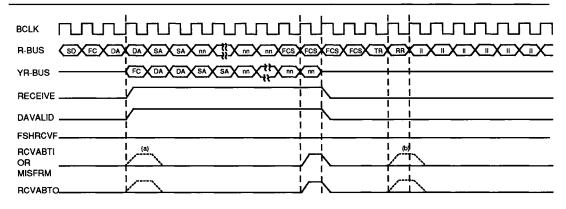

The final case of frame reception deals with the frame abort action. This action is indicated in Figure 5. The abort action occurs when the RCVABTI or MISFRM inputs are activated within the proper time periods shown. The abort action also occurs if the FORMAC enters a non-repeat, non-idle transmit state during frame reception or the disable receive mode register setting is programmed while frame reception is taking place.

Flush on stripped or corrupted frame

09731-008B

Figure 4. Flush Case C

Note:

MISFRM/RCVABTI will be processed correctly at cycle times from (a) and (b).

09731-009B

Figure 5. RCVABTI/MISFRM Reception

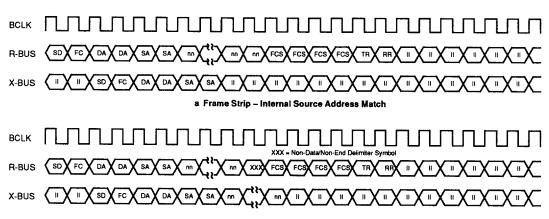

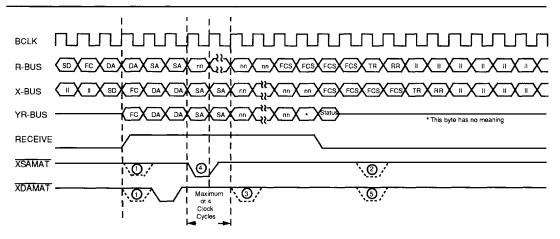

Frame Repetition. Frames received on the selected R-bus are repeated on the X-bus. In a normal case the entire frame is repeated with the frame status (FS) indicators modified according to the FDDI specification. The FORMAC transmitter can leave the repeat mode for several reasons. When this occurs, the frame received at that time is said to have been stripped.

One primary cause for stripping is the recognition of a frame whose source address (SA) equals the nodes corresponding address (my address or MA)(when comparing the receive source address against MA, the most-significant bit of the address is ignored). This is the mechanism for removing frames once they've circulated the ring. An example is illustrated in Figure 6–a. Stripping also occurs when a lost frame is encountered. The byte containing the offensive symbol as well as all subsequent bytes are removed from the ring. This case is illustrated in Figure 6–b. Tokens are also stripped when the FORMAC decides to capture. In this case, only the Start Delimiter of the token is repeated on the X-bus.

Frame status indicators are repeated, stripped, or modified according to the FDDI protocol. The FORMAC will repeat an infinite number of symbols following the frame

provided they are properly formed. The first control symbol encountered must be a "T" in the most-significant nibble of the R-bus. This signifies termination of the frame. If the first control character encountered is a "T" in the least-significant nibble, the frame has an uneven number of symbol pairs. The octet containing the "T" is repeated and all subsequent indicators are stripped. In a properly formed frame, the "T" is present in the mostsignificant nibble of the byte. The symbol after the "T" in the least- significant nibble is the error indicator. The error indicator received should be an "S" or "R" symbol. If the error indicator is not an "S" or "R", an "S" is assumed and the FORMAC will assume that frame status (FS) reception is complete. The FORMAC will recover the missing error indicator by transmitting an "S". Aside from the error indicator, no other indicator will be recovered. If a byte of FS is received with a non-"S" or "R" symbol in the most-significant nibble or non-"S", "R", or "T" symbol in the least-significant nibble, FS processing is completed. That byte and subsequent bytes of status are stripped.

Frames are not repeated when the FORMAC transmitter is in the transmit data, issue token, claim, or beacon states.

b Frame Strip - Corrupted Frame

09731-010A

Figure 6. Frame Stripping

Special Function Operation. The FORMAC receiver processes additional status information that is output via some special function pins. Special inputs are available to allow the user to supplement the FORMAC's internal address detect logic with additional hardware. This section covers the operation of these pins.

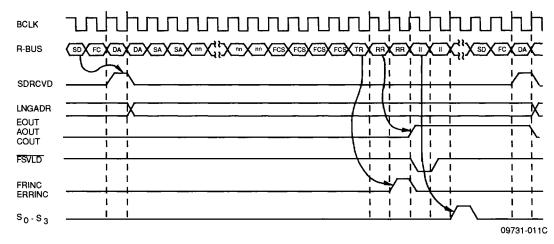

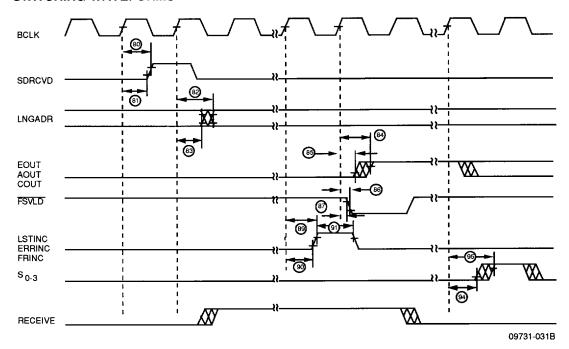

Figure 7 illustrates the relative timing of the SDRCVD, LNGADR, FSVLD, EOUT, AOUT, COUT, ERRINC, FRINC, and So-3 outputs to the received symbol stream. SDRCVD goes HIGH indicating a valid Start Delimiter is received. The LNGADR output retains the state of the last frame until the new SD is received. FSVLD, along with the E/A/COUT pins, goes HIGH at the end of frames whose SA = MA. FSVLD, EOUT, AOUT, and COUT go HIGH after the byte containing the A and

C\_indicators is received. The FRINC and ERRINC go HIGH when the ED is received. The So-3 pins go HIGH when the first byte of non-status information is received.

Figure 8 shows the operation of SDRCVD, LNGADR, and S<sub>0-3</sub> with relation to a token. In this case, the LNGADR output changes to reflect the type of token rather than the address length.

External address detection is illustrated in Figure 9. This figure shows the standard case for address detection with the solid lines. Either the XDAMAT or XSAMAT inputs can be set as early as indicated by note 1. This is the third byte following the SD on the R-bus. Although the FORMAC can handle this case, it may be difficult to achieve since the DA is still being received in the 48-bit case and the SA has not yet begun.

Figure 7. Special Function Outputs for Frame Reception

Figure 8. Special Function Outputs for Token Reception

The XSAMAT input can come as late as the appearance of the End Delimiter on the R-bus (shown as 2 on Figure 9). There is an important issue to consider regarding the timing of the XSAMAT pin. The XSAMAT will result in a stripping action beginning with the byte being received on the R-bus at the time assertion. According to the FDDI state machines, stripping for SA = MA frames should begin with the byte following the last SA byte (the solid line timing). Later assertion of XSAMAT, though in violation of the spec, will not cause inoperability problems so long as the End Delimiter is stripped. For stripping of the frame after the SA field, XSAMAT should be asserted in the cycle shown as 4 in Figure 9.

For proper setting of the FSHRCVF pin, based on external address detection, XDAMAT must be asserted in the cycle shown as cycle 3 when MDELADET = 0 or in cycle 2 when MDELADET = 1. If source address matching is being used as a criteria for frame reception (programmed in the mode register), the XSAMAT pin should also be asserted at cycle 3 to prevent the frame from being flushed, when MDELADET = 0, or at cycle 2 when MDELADET = 1.

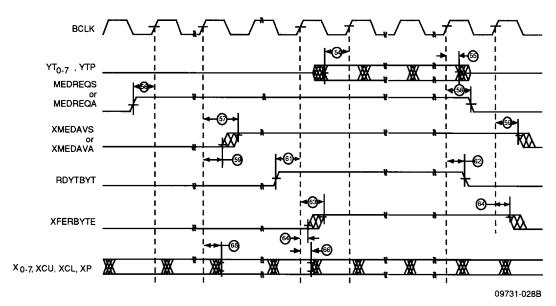

#### Transmitter

The FORMAC transmitter controls the timing of node transmission as a result of network activity. The transmitter reacts to timer expiration and received MAC frames to queue the claim and beacon frames. The transmitter controls the node's flow of data by indicating XMEDAVS or XMEDAVA as a result of token capture. The transmitter makes capture and pass decisions based upon the state of the MEDREQ inputs and token control register when the token is received.

The FORMAC asserts XMEDAVA and XMEDAVS based upon the corresponding request and the timer values. Only one XMEDAV output will be HIGH at a given time. XMEDAVS is given priority when conditions indicate that both S- and A-frames can be transmitted. When XMEDAVS is asserted, the THT timer is held. This keeps the S-frame transmission from eating into the A-frame bandwidth. The FORMAC re-evaluates the decision to transmit each time the RDYTBYT input goes LOW. If a MEDREQ input remains HIGH, the FORMAC will check the token holding criteria to determine whether another frame can be sent (see FDDI spec).

The FORMAC transmitter enters the transmit idle state when reset.

- 1 Earliest allowed assertion

- 2 Latest allowed assertion still stripping 'ED'

- 3 Latest allowed assertion suppressing FSRCVF and setting A indicator (if MDELADET = 0)

- 4 Latest allowed assertion still stripping after SA

- 5 Latest allowed assertion suppressing FSRCVF and A\_indicator (if MDELADET = 1)

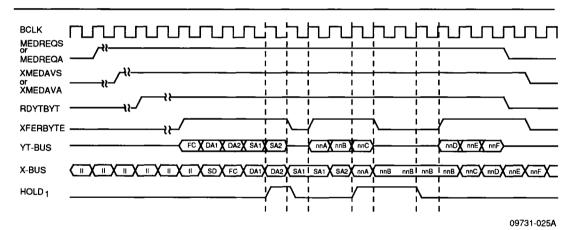

09731-013B

Figure 9. External Address Detection

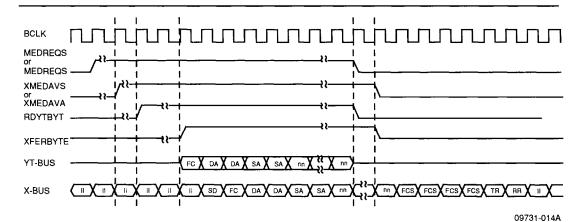

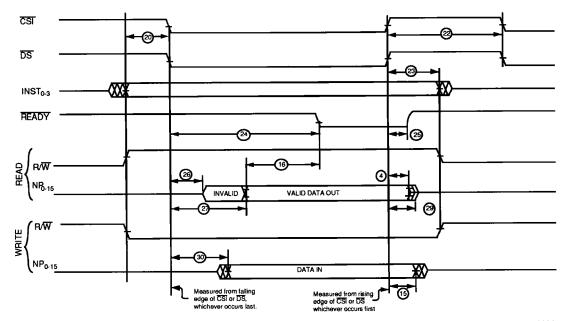

Frame Transmission. Figure 10 gives an example of a transmitted frame. The XMEDAVS or XMEDAVA is asserted based on a corresponding MEDREQS or MEDREQA. The delay from the request to the acknowledgement is based on the time required to capture a token. Once XMEDAV is given, the FORMAC waits for RDYTBYT input. RDYTBYT guarantees a continuous frame is available at the YT-bus for transmission. The FORMAC will wait to assert XFRBYT, if required, to ensure that at least 8 bytes (16 symbols) of preamble have been transmitted.

The FORMAC will encapsulate all bytes input on the YT-bus when XFRBYTE and RDYTBYT signals are active. An SD is output on the X-bus immediately prior to transmission of the first YT byte. The frame check sequence (FCS) is appended after the last byte given on YT. FCS will not be appended if the MNFCS bit is set in the FORMAC mode register. After the FCS field, a "T" and "R" symbol are output on the most- and least-significant nib-

ble of the X-bus, respectively. This is the frame's End Delimiter and error status indicator. This is followed by two more "Rs" for the address and copy indication.

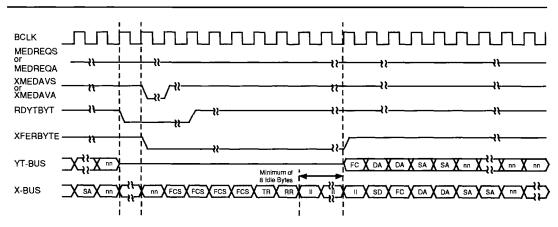

In Figure 10, the frame transmitted is the final frame in the queue. This is determined by the MEDREQ going LOW with RDYTBYT. Figure 11 gives the case where another frame should be transmitted from the queue. Here MEDREQ remains HIGH. The FORMAC will lower XMEDAV as a result of RDYTBYT going LOW. If the network conditions for sending another frame can be met. XMEDAV is asserted in the next cycle.

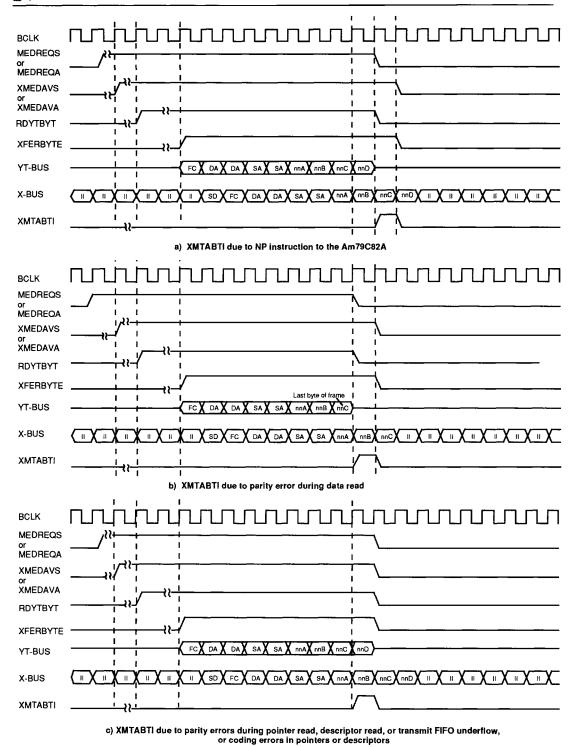

A transmit abort is indicated by the XMTABTI input pin going HIGH. In this case, the next byte to be placed on the X-bus is replaced by idle. The FORMAC transmit state machine will be reset to the idle state. XMTABTI is asserted in the cycle after MEDREQ (S or A) and RDYTBYT are lowered. This case is given in Figure 12.

Figure 10. Frame Transmission: Last Frame on the Queue

Figure 11. Frame Transmission: Another Frame

09731-015A

Figure 12. Frame Transmission: Transmit Abort

09731-016B

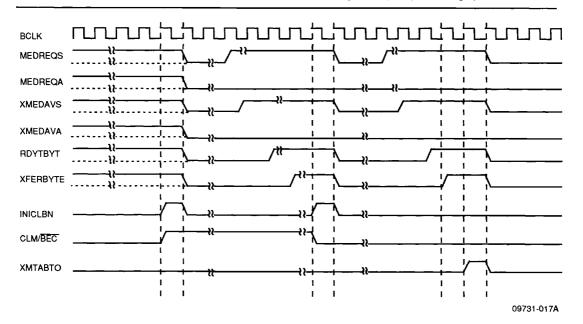

Recovery Operation. The FORMAC transmitter can go into recovery based upon frames received, instructions from the NP, and timer expiration. There are two recovery states specified in the FDDI. These are the claim and beacon states. Claim is used to negotiate the operative time for token rotation and determine which node will issue the token. Beacon is used to guarantee ring integrity by verifying the path of the ring.

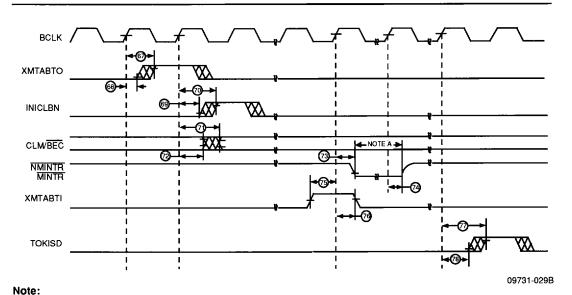

Claim and beacon state can be entered at any given time. Once claim or beacon is entered, the FORMAC must respond by placing the corresponding claim or beacon frames on the X-bus. The FORMAC signals the claim or beacon state so that the proper frame can be queued for transmission. This is shown in Figure 13.