### RS8228/M28228

### Octal ATM Transmission Convergence PHY Device

The RS8228 Octal ATM Transmission Convergence PHY device dramatically improves performance for switch and access system low-speed ports by integrating all the ATM physical layer processing functions found in the ATM Forum Cell Based Transmission Convergence Sublayer specification (af-phy-0043.000) for eight individual ports. Each port can be independently configured for operation at speeds ranging from 64 kbps to 52 Mbps. There is also a powerdown mode option for each TC port. A UTOPIA Level 2 Multi-PHY interface connects the device to the host switch or terminal system and concentrates the ATM cell traffic onto one interface.

Typical system implementations center around the concentration of ATM cells over standard PDH data rates such as T1/E1 lines, DS3/E3 lines, and multiple Digital Subscriber Line (DSL) formats such as HDSL, ADSL or VDSL\*. For each format, external devices perform the appropriate Physical Media Dependent (PMD) layer functions and present the RS8228 with a payload bit stream. The RS8228 then performs all cell alignment functions on that bit stream. This gives system designers a simple, modular, and low-cost architecture for supporting all UNI and NNI ATM interfaces below 52 Mbps. Because the RS8228 performs only the cell-based portion of the protocol stack, designers can select the most integrated framer and Line Interface Unit (LIU) available or reuse existing devices and software.

The RS8228 can also be used in combination with a Conexant Segmentation and Reassembly (SAR) device. The RS8228 gluelessly connects to the SAR via the UTOPIA and microprocessor interfaces. The device can be configured and controlled optionally through a generic microprocessor interface. The RS8228's chip-select feature allows the microprocessor to select any of the framers through the PHY. The RS8228's eight interrupt inputs provide an internal mechanism for registering and controlling generated interrupts.

\* The term xDSL is used throughout this document to refer to the various DSL formats as a group.

### **Distinguishing Features**

- 8 cell-based TC Ports

- UTOPIA interface

- Level 2

- 8/16 bit modes

- Multi-PHY

- Redundant channel

- · Glueless interface to Conexant's:

- T1/E1 framers

- T3/E3 framers

- HDSL/SDSL devices

- SAR devices

- · Software reference material provided

- 8 chip selects for external framers

- 8 interrupt inputs for external framers

- · Octet- and bit-level cell delineation

- ITU I.432-compliant

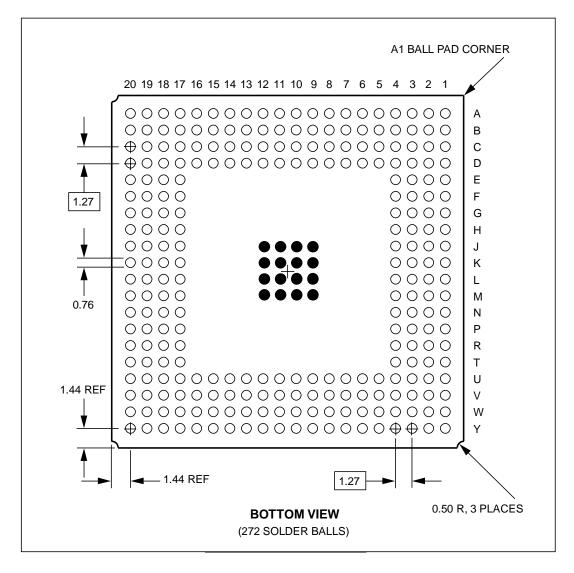

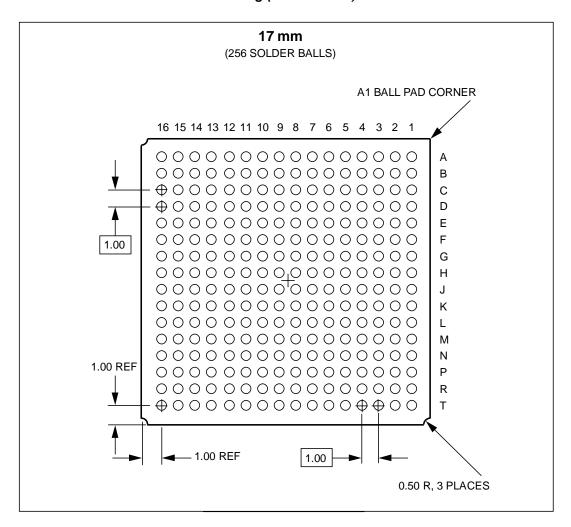

- Available in either 27 mm or 17 mm BGA packages

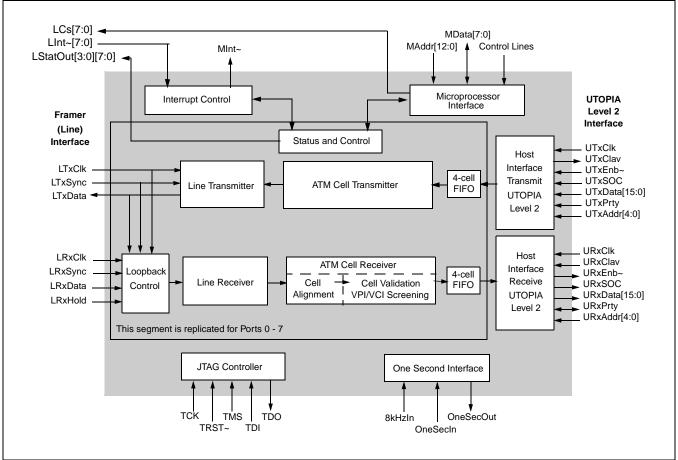

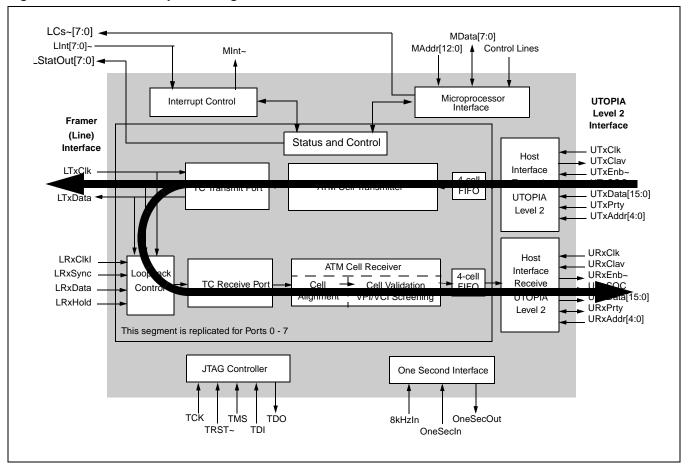

### **Functional Block Diagram**

### **Ordering Information**

| Model Number | Manufacturing<br>Part Number | Product<br>Revision | Package             | Operating Temperature |  |

|--------------|------------------------------|---------------------|---------------------|-----------------------|--|

| RS8228EBG    | 28228-11                     | А                   | 272-ball, 27 mm BGA | -40 °C to 85 °C       |  |

| RS8228EBGB   | 28228-12                     | В                   | 272-ball, 27 mm BGA | -40 °C to 85 °C       |  |

| M28228       | 28228-21                     | А                   | 256-ball, 17 mm BGA | –40 °C to 85 °C       |  |

### **Revision History**

| Revision | Level | Date          | Description                                                                                                                                          |  |  |  |

|----------|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| С        | _     | April 2005    | Corrected 0x05—IOMODE (Input/Output Mode Control Register), bits 5 and 3.                                                                            |  |  |  |

| В        | _     | November 2003 | Placed registers in numerical order.                                                                                                                 |  |  |  |

| A        | _     | November 2001 | This version has the 17 mm BGA information included. Note that this document was previously released under the document numbers 100064A and 100064B. |  |  |  |

© 2005 Mindspeed Technologies<sup>TM</sup>, Inc. All rights reserved.

Information in this document is provided in connection with Mindspeed Technologies<sup>TM</sup> ("Mindspeed<sup>TM</sup>") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Except as provided in Mindspeed's Terms and Conditions of Sale for such products or in any separate agreement related to this document, Mindspeed assumes no liability whatsoever. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.

### Framer (Line) Interface Section

- · Programmable bit or byte synchronous serial interface

- · Direct connection to external Conexant components for:

- T1/F1

- DS3

- E3

- J2

- xDSL

- General purpose mode

- Interrupt and chip select signals for each external framer

### **Cell Alignment Framing Section**

- Supports ATM cell interface for:

- Circuit-based physical layer

- Cell-based physical layer

- Passes or rejects idle cells or selected cells based on header register configuration

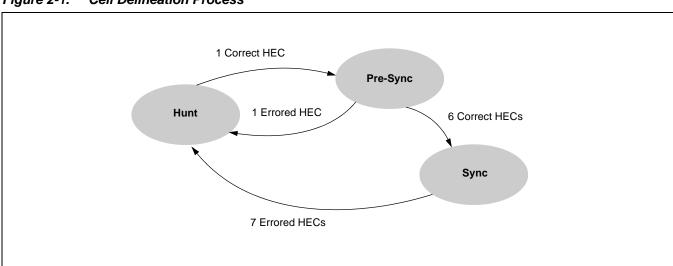

- Recovers cell alignment from Header Error Correction (HEC)

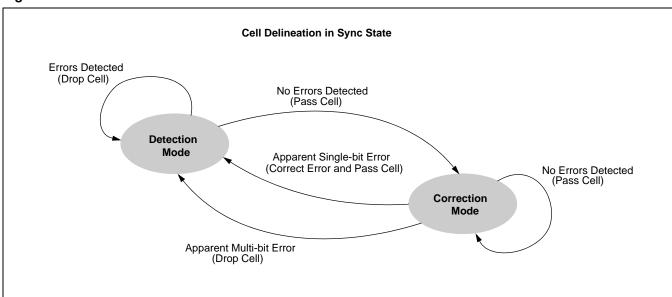

- Performs single-bit HEC correction and single- or multiple-bit detection

- · Generates cell status bits, cell counts, and error counts

- Inserts headers and generates HEC

- · Inserts idle cells when no traffic is ready

#### **UTOPIA** Level 2 Interface

- · PHY cell to UTOPIA interface

- · 50 MHz maximum clock rate

- 8/16-bit data path interface

· Multi-PHY capability

### **Control and Status**

#### Microprocessor Interface

- · Asynchronous SRAM-like interface mode

- Synchronous, glueless Bt8233/RS8234 SAR interface mode

- 8-bit data bus

- Open-drain interrupt output

- · Open-drain ready output

- 8–50 MHz operation

- All control registers are read/write

- Four programmable status indicator signals per port

### Counters/Status Register Section

- · Summary interrupt indications

- Configuration of interrupt enables

- · One-second counter latching

- Counters for:

- LOCD events

- Corrected HEC errors

- Uncorrected HEC errors

- Transmitted cells

- Matching received cells

- Non-matching received cells

# **Table of Contents**

|     | List | of Figu        | res                                |

|-----|------|----------------|------------------------------------|

|     | List | of Table       | esviii                             |

| 1.0 | Prod | duct Des       | scription                          |

|     | 1.1  | Applica        | tion Overview                      |

|     | 1.2  |                | Diagram                            |

|     | 1.3  | •              | Pin Diagram and Definitions        |

|     | 1.4  |                | Pin Diagram and Definitions        |

|     | 1.5  |                | Diagram and Descriptions           |

| 2.0 | Fun  | ctional        | Description                        |

|     | 2.1  |                | ell Processor                      |

|     | 2.1  | 2.1.1          | ATM Cell Transmitter               |

|     |      | 2.1.1          | 2.1.1.1 HEC Generation             |

|     |      | 2.1.2          | ATM Cell Receiver                  |

|     |      | 2.1.2          | 2.0.0.1 Cell Delineation           |

|     |      |                | 2.0.0.2 Cell Screening             |

|     |      | 2.1.3          | Cell Scrambler                     |

|     |      | 2.1.5          | 2.0.0.1 SSS Scrambling             |

|     |      |                | 2.0.0.2 DSS Scrambling             |

|     | 2.2  | Framin         | g Modes                            |

|     | 2.2  | 2.2.1          | T1/E1 Timing for the CX28229       |

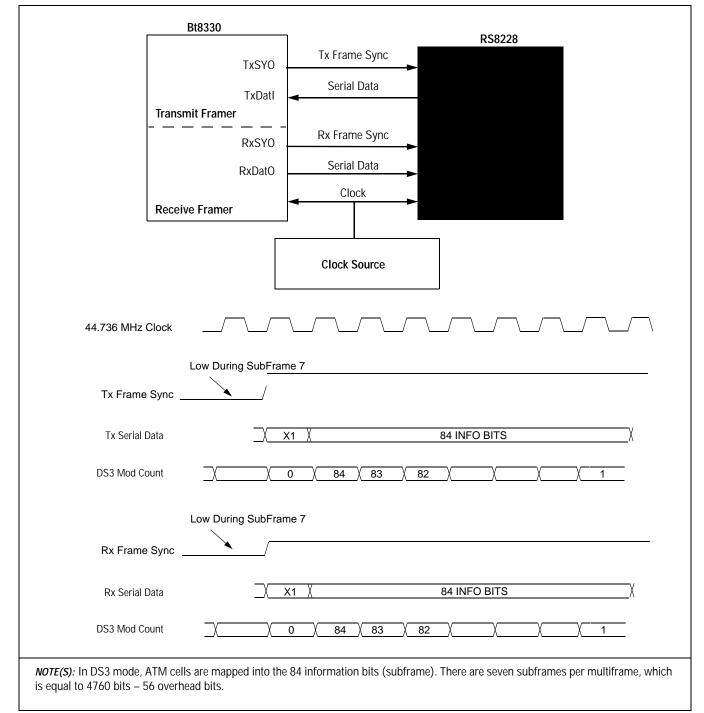

|     |      | 2.2.1          | DS3 Interface                      |

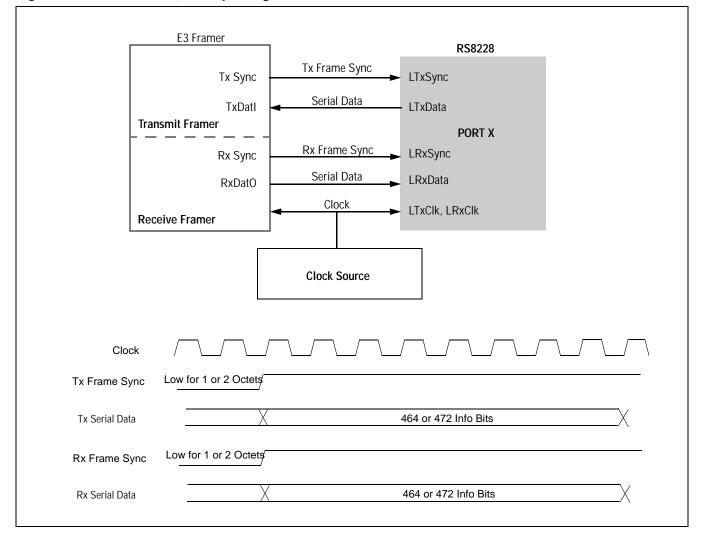

|     |      | 2.2.3          | E3/G.832 34.368 Mbps Interface     |

|     |      | 2.2.4          | J2 6.312 Mbps Interface            |

|     |      | 2.2.5          | General Purpose Mode Interface     |

|     | 2.3  | UTOPIA         | A Interface                        |

|     |      | 2.3.1          | UTOPIA Transmit and Receive FIFOs  |

|     |      | 2.3.2          | UTOPIA 8-bit and 16-bit Bus Widths |

|     |      | 2.3.3          | UTOPIA Parity                      |

|     |      | 2.3.4          | UTOPIA Multi-PHY Operation         |

|     |      | 2.3.5          | UTOPIA Addressing                  |

|     | 2.4  | 2.3.6          | Handshaking                        |

|     | 2.4  |                | rocessor Interface                 |

|     |      | 2.4.1<br>2.4.2 | Resets                             |

|     |      | 2.4.2          | Status Pins                        |

|     |      | 2.4.3          | One-second Latching                |

|     |      | Z.T.T          | - One south $\mathbf{Laterniag}$   |

|     |     | 2.4.5  |          | amer Interrupts and Chip Selects              |    |

|-----|-----|--------|----------|-----------------------------------------------|----|

|     |     | 2.4.6  |          |                                               |    |

|     |     |        |          | Interrupt Routing                             |    |

|     |     |        |          | Interrupt Servicing                           |    |

|     | 2.5 | Source | Loopback |                                               | 21 |

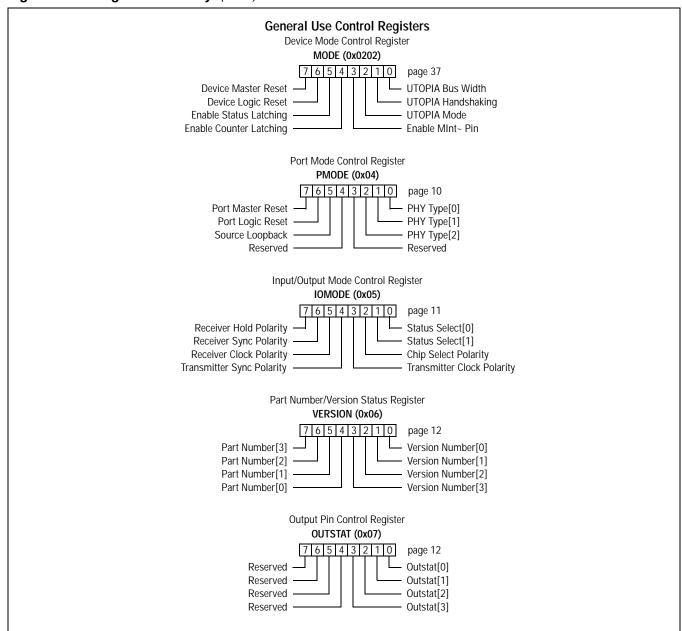

| 3.0 | Dog | ictore |          |                                               | 1  |

| 3.0 | Key |        |          |                                               |    |

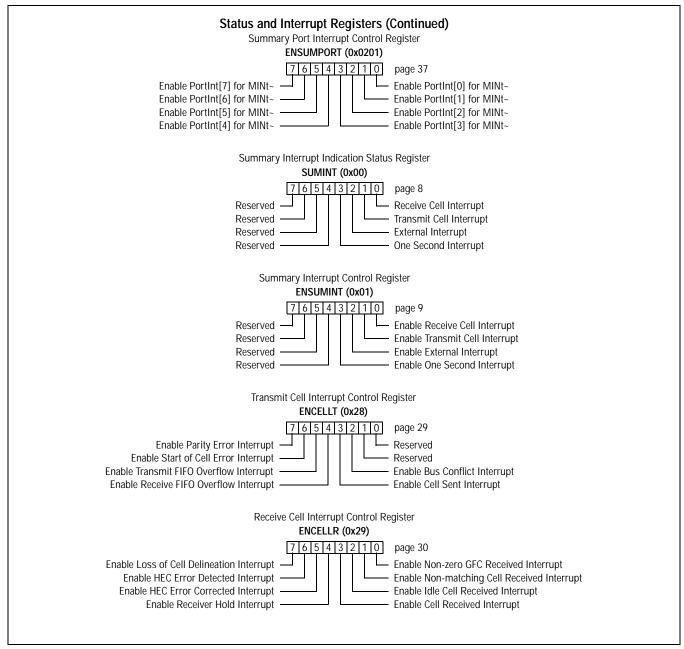

|     |     |        |          | Summary Interrupt Indication Status Register) |    |

|     |     |        |          | T (Summary Interrupt Control Register)        |    |

|     |     |        |          | Port Mode Control Register)                   |    |

|     |     |        |          | Input/Output Mode Control Register)           |    |

|     |     |        |          | (Part Number/Version Status Register)         |    |

|     |     |        |          | (Output Pin Control Register)                 |    |

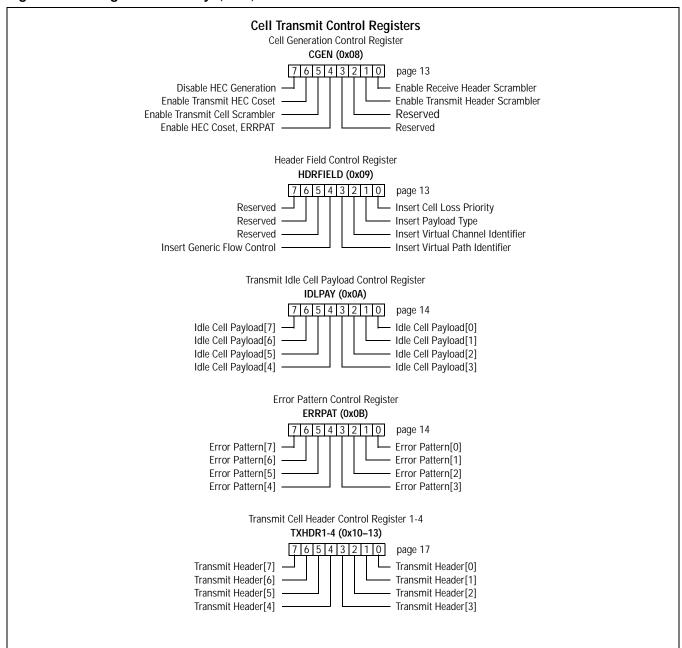

|     |     |        |          | Il Generation Control Register)               |    |

|     |     |        |          | (Header Field Control Register)               |    |

|     |     |        |          | Transmit Idle Cell Payload Control Register)  |    |

|     |     |        |          | Error Pattern Control Register)               |    |

|     |     |        | · ·      | I Validation Control Register)                |    |

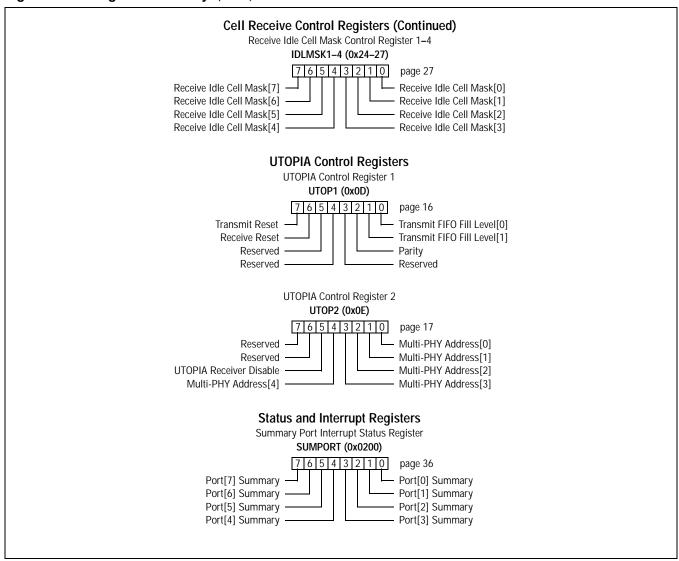

|     |     |        |          | TOPIA Control Register 1)                     |    |

|     |     |        | •        | TOPIA Control Register 2)                     |    |

|     |     |        |          | Transmit Cell Header Control Register 1)      |    |

|     |     |        |          | Transmit Cell Header Control Register 2)      |    |

|     |     |        |          | Transmit Cell Header Control Register 3)      |    |

|     |     |        |          | Transmit Cell Header Control Register 4)      |    |

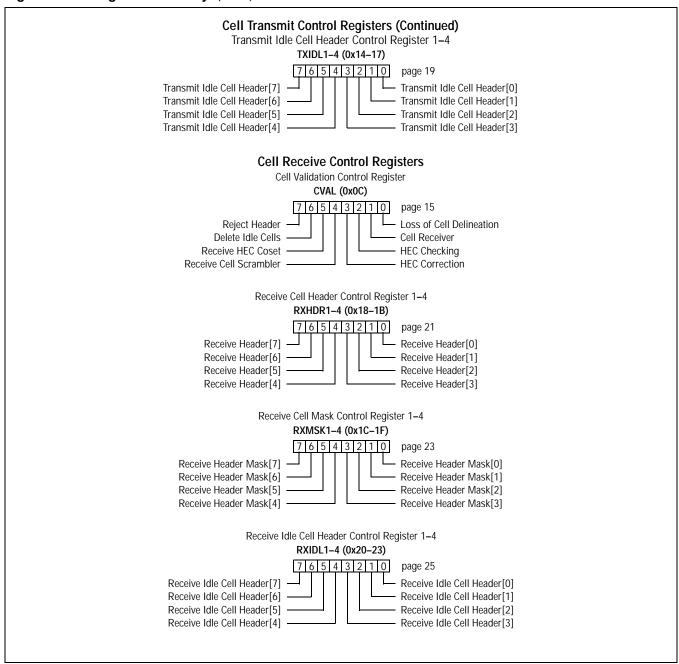

|     |     |        | · ·      | ransmit Idle Cell Header Control Register 1)  |    |

|     |     |        |          | ransmit Idle Cell Header Control Register 2)  |    |

|     |     |        | · ·      | ransmit Idle Cell Header Control Register 3)  |    |

|     |     |        |          | ransmit Idle Cell Header Control Register 4)  |    |

|     |     |        |          | Receive Cell Header Control Register 1)       |    |

|     |     |        |          | Receive Cell Header Control Register 2)       |    |

|     |     |        |          | (Receive Cell Header Control Register 3)      |    |

|     |     |        |          | (Receive Cell Header Control Register 4)      |    |

|     |     |        |          | (Receive Cell Mask Control Register 1)        |    |

|     |     |        |          | (Receive Cell Mask Control Register 2)        |    |

|     |     |        |          | (Receive Cell Mask Control Register 3)        |    |

|     |     |        |          | Receive Cell Mask Control Register 4)         |    |

|     |     |        |          | Receive Idle Cell Header Control Register 1)  |    |

|     |     |        |          | Receive Idle Cell Header Control Register 2)  |    |

|     |     |        |          | Receive Idle Cell Header Control Register 3)  |    |

|     |     |        |          | Receive Idle Cell Header Control Register 4)  |    |

|     |     |        |          | (Receive Idle Cell Mask Control Register 1)   |    |

|     |     |        |          | (Receive Idle Cell Mask Control Register 2)   |    |

|     |     |        |          | (Receive Idle Cell Mask Control Register 3)   |    |

|     |     |        |          | (Receive Idle Cell Mask Control Register 4)   |    |

|     |     |        |          | (Transmit Cell Interrupt Control Register)    |    |

|     |     | 0x29-  | -ENCELLR | (Receive Cell Interrupt Control Register)     | 30 |

### Octal ATM Transmission Convergence PHY Device

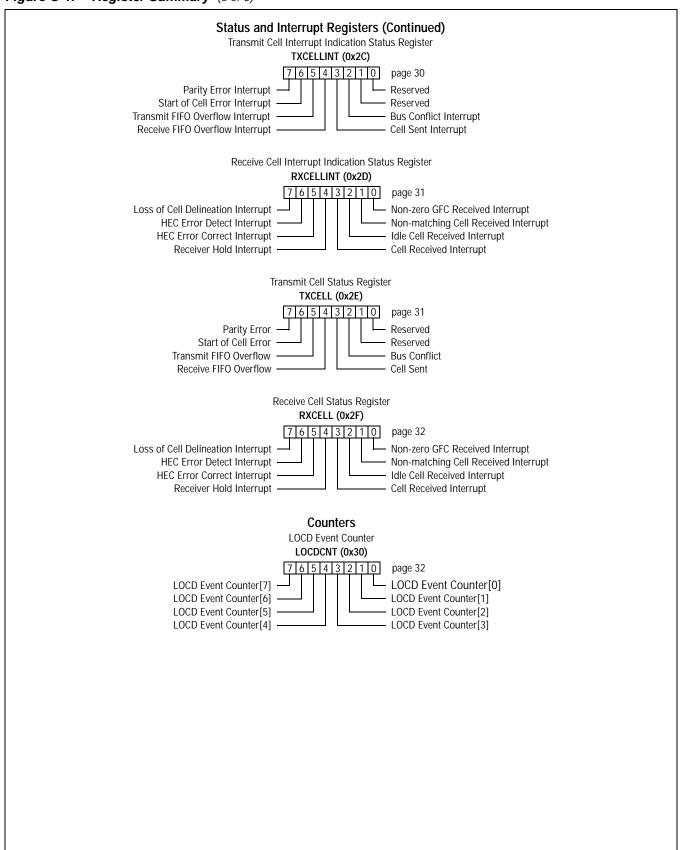

|       |       | 0x2C—TXCELLINT (Transmit Cell Interrupt Indication Status Register)                                 |

|-------|-------|-----------------------------------------------------------------------------------------------------|

|       |       | 0x2D—RXCELLINT (Receive Cell Interrupt Indication Status Register)                                  |

|       |       | 0x2E—TXCELL (Transmit Cell Status Register)                                                         |

|       |       | 0x2F—RXCELL (Receive Cell Status Register)                                                          |

|       |       | 0x30—LOCDCNT (LOCD Event Counter)                                                                   |

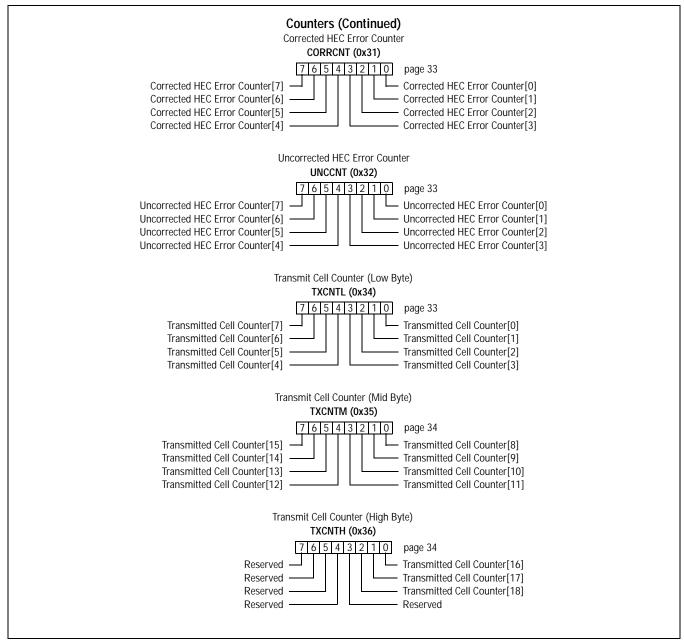

|       |       | 0x31—CORRCNT (Corrected HEC Error Counter)33                                                        |

|       |       | 0x32—UNCCNT (Uncorrected HEC Error Counter)33                                                       |

|       |       | 0x34—TXCNTL (Transmitted Cell Counter [Low Byte])                                                   |

|       |       | 0x35—TXCNTM (Transmitted Cell Counter [Mid Byte])                                                   |

|       |       | 0x36—TXCNTH (Transmitted Cell Counter [High Byte])                                                  |

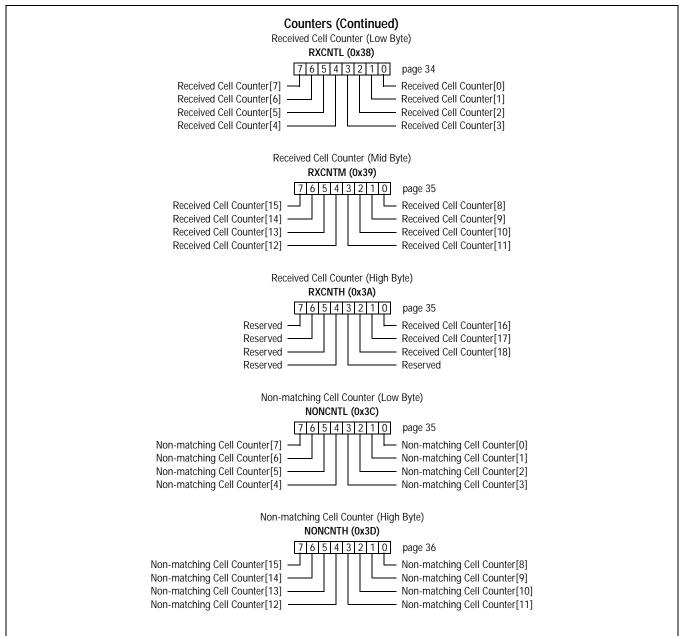

|       |       | 0x38—RXCNTL (Received Cell Counter [Low Byte])                                                      |

|       |       | 0x39—RXCNTM (Received Cell Counter [Mid Byte])                                                      |

|       |       | 0x3A—RXCNTH (Received Cell Counter [High Byte])35                                                   |

|       |       | 0x3C—NONCNTL (Non-matching Cell Counter [Low Byte])                                                 |

|       |       | 0x3D—NONCNTH (Non-matching Cell Counter [High Byte])                                                |

|       |       | 0x0200—SUMPORT (Summary Port Interrupt Status Register)                                             |

|       |       | 0x0201—ENSUMPORT (Summary Port Interrupt Control Register)                                          |

|       |       | 0x0202—MODE (Device Mode Control Register)                                                          |

| 40 5  |       | Litratian I Mantagarta I Constitution                                                               |

| 4.0 E | leci  | trical and Mechanical Specifications                                                                |

| 4     | .1    | Timing Specifications                                                                               |

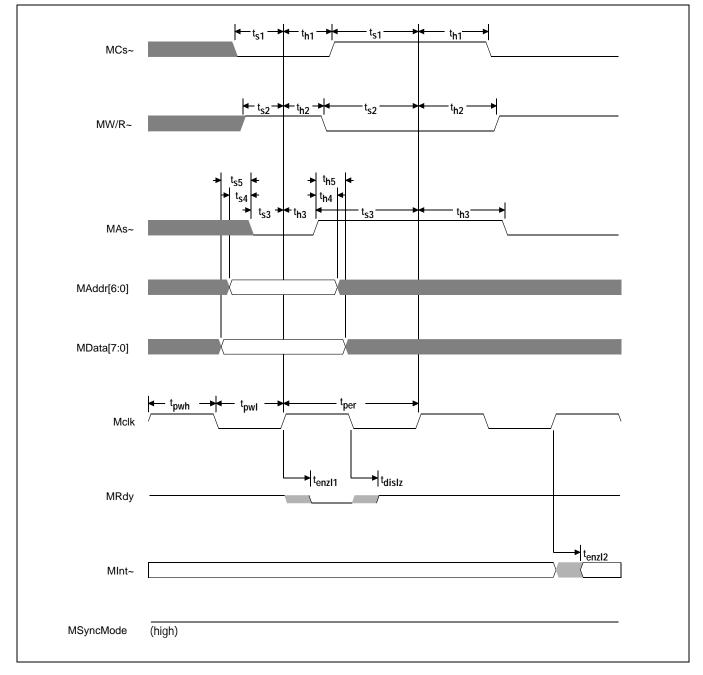

|       |       | 4.1.1 Microprocessor Timing                                                                         |

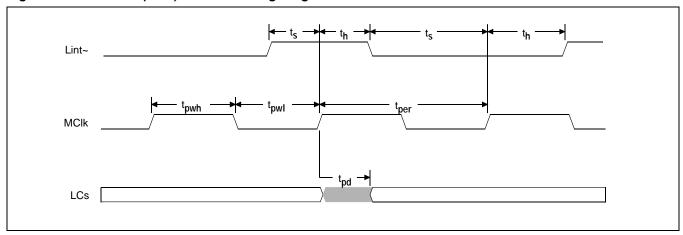

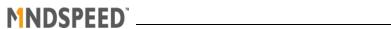

|       |       | 4.1.2 Framer (Line) Interface Timing                                                                |

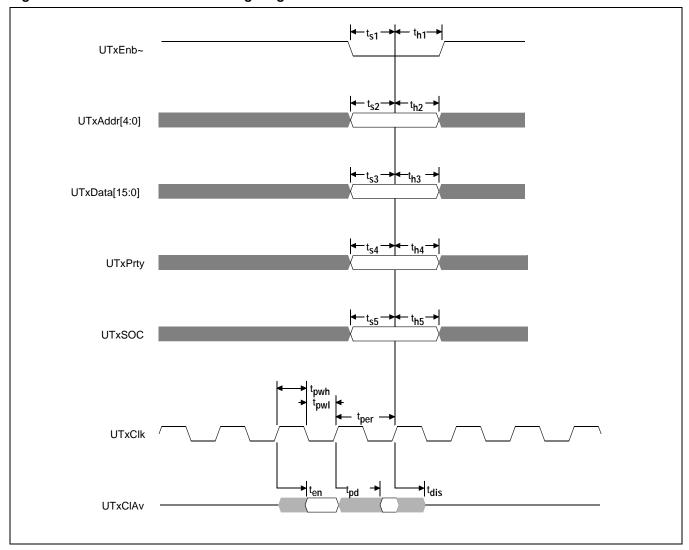

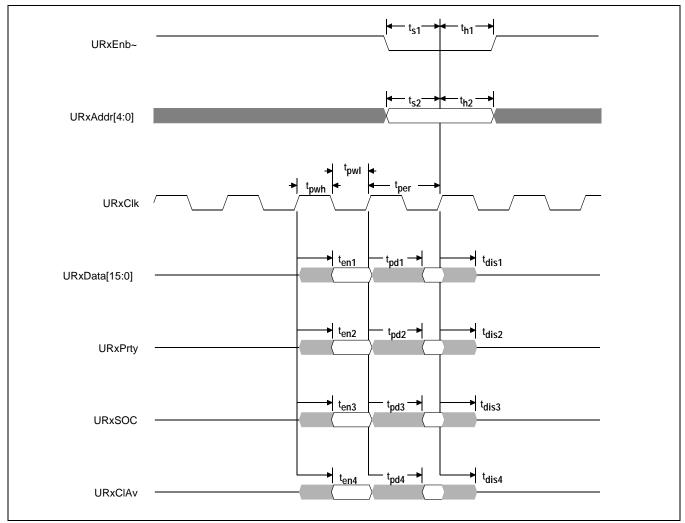

|       |       | 4.1.3 UTOPIA Interface Timing                                                                       |

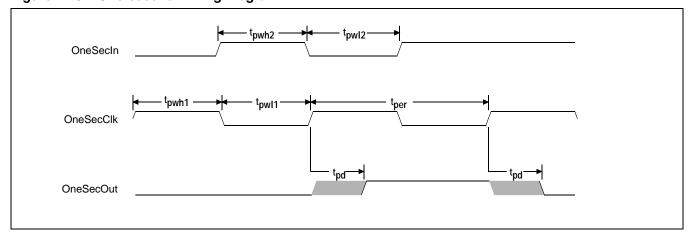

|       |       | 4.1.4       JTAG Interface Timing       16         4.1.5       One-second Interface Timing       17 |

| 4     | .2    | Absolute Maximum Ratings                                                                            |

| 4     | .3    | DC Characteristics                                                                                  |

| 4     | .4    | 27 mm Mechanical Drawing                                                                            |

|       | .5    | 17 mm Mechanical Drawing                                                                            |

|       |       |                                                                                                     |

| Appen | dix   | A:Related Standards                                                                                 |

| _     |       |                                                                                                     |

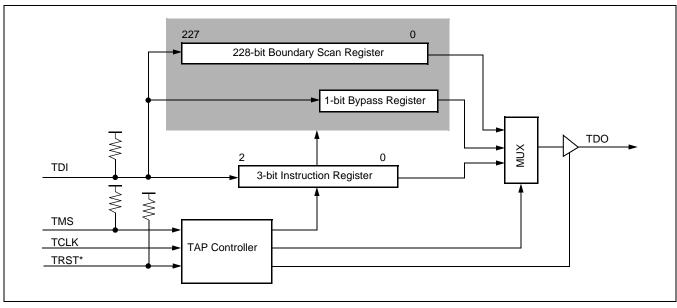

| Appen | dix   | B:Boundary Scan                                                                                     |

| В     | 3.1   | Instruction Register                                                                                |

| В     | 3.2   | BYPASS Register                                                                                     |

|       |       |                                                                                                     |

| Appen | dix ( | C:Register Summary                                                                                  |

# **List of Figures**

| Figure 1-1.  | RS8228 Connected to a RS8398 Transceiver             | . 2 |

|--------------|------------------------------------------------------|-----|

| Figure 1-2.  | RS8228 Logic Diagram                                 | . 3 |

| Figure 1-3.  | RS8228 27 mm Pinout Diagram (Top View)               | 4   |

| Figure 1-4.  | M28228 17 mm Pinout Diagram (Top View)               | 6   |

| Figure 1-5.  | RS8228 Block Diagram                                 | 27  |

| Figure 2-1.  | Cell Delineation Process                             | . 2 |

| Figure 2-2.  | Header Error Check Process                           | . 3 |

| Figure 2-3.  | Bt8370 Interface Diagram                             | 6   |

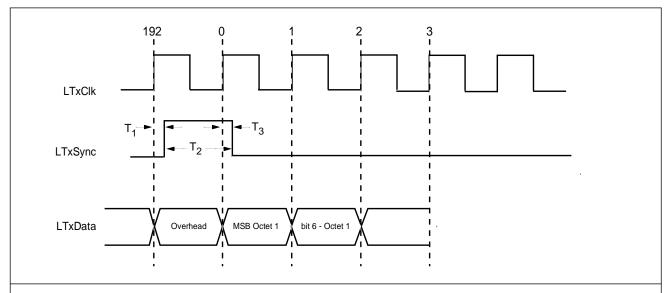

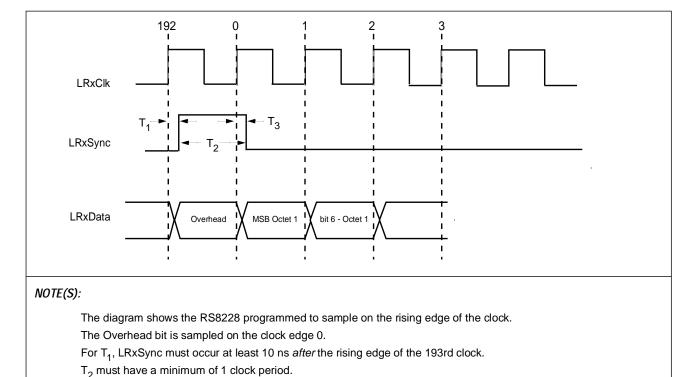

| Figure 2-4.  | Transmit Waveforms                                   | . 7 |

| Figure 2-5.  | Receive Waveforms                                    | 8   |

| Figure 2-6.  | Bt8330 Interface Diagram                             | 9   |

| Figure 2-7.  | E3/G.832 36,368 kbps Diagram                         | 0   |

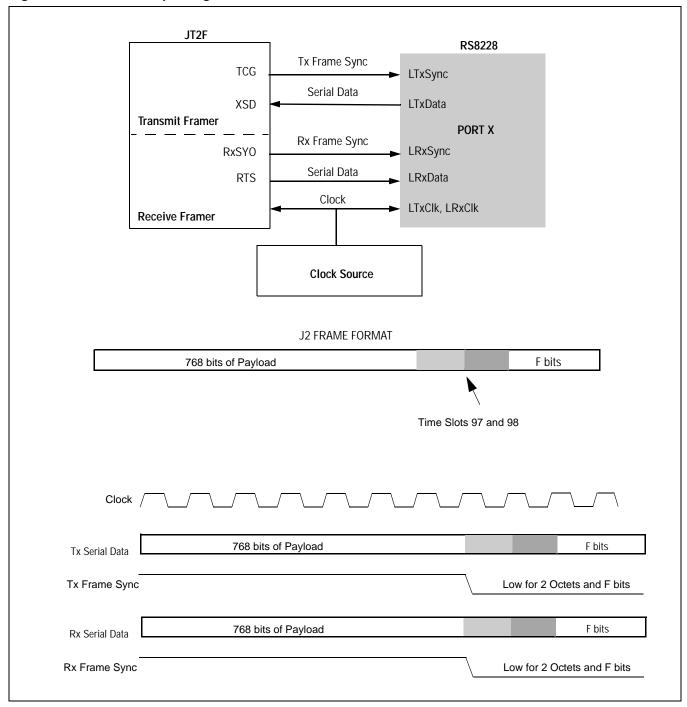

| Figure 2-8.  | J2 6312 kbps Diagram                                 | 1   |

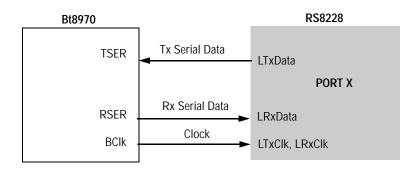

| Figure 2-9.  | General Purpose Mode                                 | 2   |

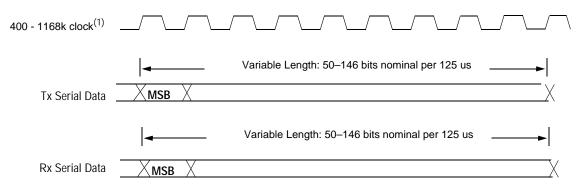

| Figure 2-10. | Interrupt Indication Flow Chart                      | 9   |

| Figure 2-11. | Interrupt Indication Diagram                         | 20  |

| Figure 2-12. | Source Loopback Diagram                              | 22  |

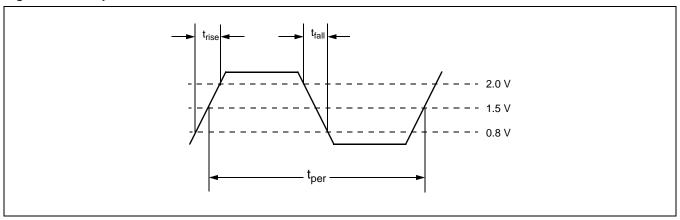

| Figure 4-1.  | Input Waveform                                       |     |

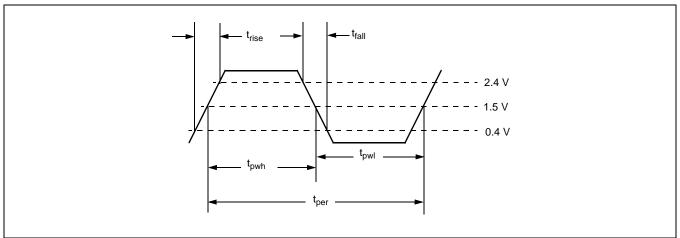

| Figure 4-2.  | Output Waveform                                      | . 4 |

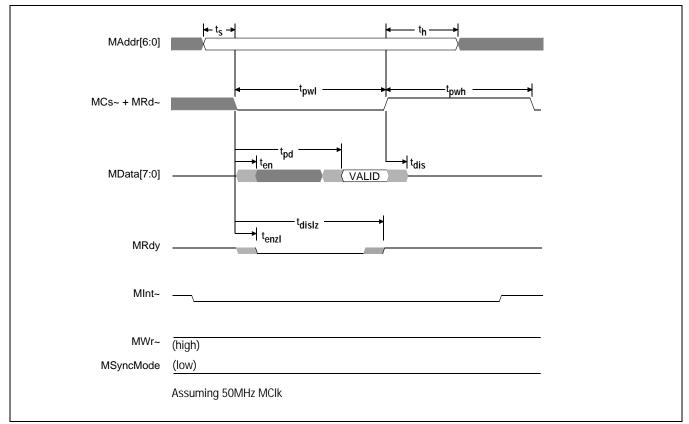

| Figure 4-3.  | Microprocessor Timing Diagram—Asynchronous Read      | . 5 |

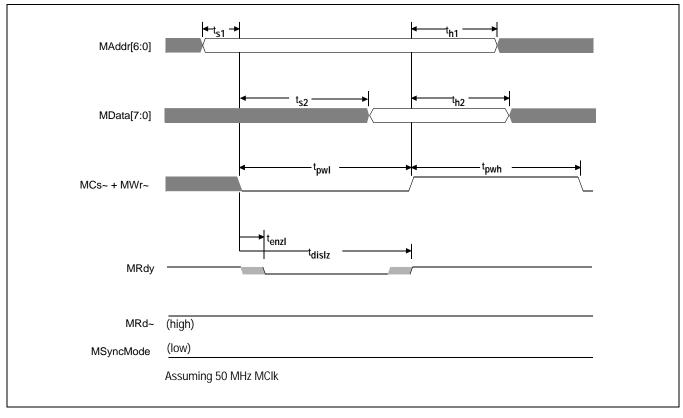

| Figure 4-4.  | MIcroprocessor Timing Diagram—Asynchronous Write     |     |

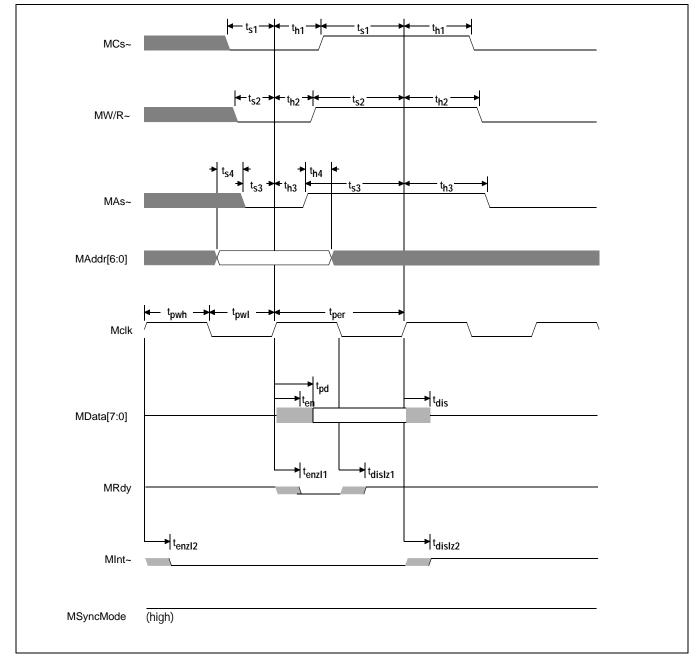

| Figure 4-5.  | Microprocessor Timing Diagram—Synchronous Read       | . 7 |

| Figure 4-6.  | Microprocessor Timing Diagram—Synchronous Write      |     |

| Figure 4-7.  | Framer (Line) Control Timing Diagram                 |     |

| Figure 4-8.  | Framer (Line) Transmit Timing Diagram                | 1   |

| Figure 4-9.  | Framer (Line) Receive Timing Diagram                 | 2   |

| Figure 4-10. | UTOPIA Transmit Timing Diagram                       |     |

| Figure 4-11. | UTOPIA Receive Timing Diagram                        |     |

| Figure 4-12. | JTAG Timing Diagram                                  | 6   |

| Figure 4-13. | One-second Timing Diagram                            |     |

| Figure 4-14. | RS8228 27 mm Mechanical Drawing (Bottom View)        |     |

| Figure 4-15. | RS8228 27 mm Mechanical Drawing (Top and Side Views) |     |

| Figure 4-16. | M28228 17 mm Mechanical Drawing (Bottom View)        |     |

| Figure 4-17. | M28228 17 mm Mechanical Drawing (Top and Side Views) |     |

| Figure B-2.  | Test Circuitry Block Diagram                         | . 2 |

| Figure C-1.  | Register Summary                                     | .1  |

# **List of Tables**

| Table 1-1.  | RS8228 27 mm Pin Descriptions                  | . ၁ |

|-------------|------------------------------------------------|-----|

| Table 1-2.  | RS8228 17 mm Pin Descriptions                  | 17  |

| Table 2-1.  | Cell Screening—Matching                        | . 4 |

| Table 2-2.  | Cell Screening—Accept/Reject Cell              | . 4 |

| Table 2-3.  | Cell Format for 8-bit Mode                     | 13  |

| Table 2-4.  | Cell Format for 16-bit Mode                    | 14  |

| Table 2-5.  | LStatOut Configuration                         | 16  |

| Table 2-6.  | Chip Selects                                   | 18  |

| Table 3-1.  | Address Ranges                                 | .1  |

| Table 3-2.  | Device Control and Status Registers            | . 2 |

| Table 3-3.  | Port Control and Status Registers              | . 2 |

| Table 3-4.  | General Use Registers                          | . 4 |

| Table 3-5.  | Cell Transmit Registers                        | . 5 |

| Table 3-6.  | Cell Receive Registers                         | . 5 |

| Table 3-7.  | UTOPIA Registers                               | .6  |

| Table 3-8.  | Status and Interrupt Registers                 | . 6 |

| Table 3-9.  | Counters                                       | .7  |

| Table 4-1.  | Timing Diagram Nomenclature                    |     |

| Table 4-2.  | Microprocessor Timing Table—Asynchronous Read  | . 5 |

| Table 4-3.  | Microprocessor Timing Table—Asynchronous Write |     |

| Table 4-4.  | Microprocessor Timing Table—Synchronous Read   | .8  |

| Table 4-5.  | Microprocessor Timing Table—Synchronous Write  | 10  |

| Table 4-6.  | Framer (Line) Control Timing Table             |     |

| Table 4-7.  | Framer (Line) Transmit Timing Table            | 11  |

| Table 4-8.  | Framer (Line) Receive Timing Table             | 12  |

| Table 4-9.  | UTOPIA Transmit Timing Table                   | 14  |

| Table 4-10. | UTOPIA Receive Timing Table                    |     |

| Table 4-11. | JTAG Timing Table                              | 17  |

| Table 4-12. | One-second Timing Table                        |     |

| Table 4-13. | Absolute Maximum Ratings                       | 18  |

| Table 4-14. | DC Characteristics                             |     |

| Table B-1.  | Boundary Scan Signals                          |     |

| Table 2-3.  | IEEE Std. 1149.1 Instructions                  | . 2 |

| Table 2-4.  | Boundary Scan Register Cells                   | .3  |

## 1.0 Product Description

The RS8228 Octal ATM Transmission Convergence (TC) PHY device dramatically increases the level of integration for switches and access systems. The RS8228 integrates all the ATM Layer processing functions found in the ATM Forum Cell Based Transmission Convergence Sublayer specification (af-phy-0043.000) in each of eight individual ports.

A UTOPIA Level 2 Multi-PHY interface connects the device to the host switch or terminal system and concentrates the ATM cell traffic onto one bus interface. Because the RS8228 performs only the cell-based portion of the protocol stack, designers may choose the line formatter. Each port may be configured for operation at speeds from 64 kbps to 52 Mbps, allowing a maximum aggregate bandwidth of 416 Mbps for all active ports.

Typical system implementations center around the concentration of multiple standard data rates such as T1 and E1 lines, DS3 and E3 lines, and multiple Digital Subscriber Line (DSL) formats such as HDSL, ADSL or VDSL. For each specific format, external devices perform the appropriate PMDlayer functions and present the RS8228 with a payload bit stream. The RS8228 then performs all cell alignment functions on that bit stream. This gives system designers a simple, modular, and low-cost architecture for supporting all ATM interfaces below 52 Mbps. It also enables them to select the most integrated framer and LIU available, or reuse existing devices and software. The RS8228 device provides a low-cost ATM interface architecture for UNI or NNI interfaces.

NOTE: Both the 27 mm and 17 mm packages use the same silicon die. All references to the RS8228 apply to the M28228.

### 1.1 Application Overview

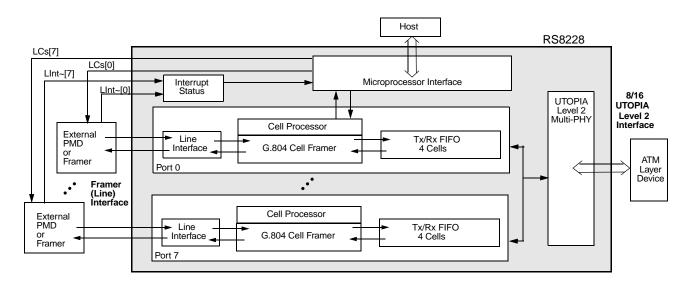

The RS8228 is typically used with line framer devices like the RS8398 T1/E1 octal transceiver, the Bt8970 Zip Wire or the Bt8953 HDLC Framer. It provides a chip-select feature that allows the microprocessor to select any framer connected to it. The RS8228 also has eight interrupt inputs so interrupts from the framers can be registered and controlled in the PHY. Figure 1-1 illustrates a typical application.

Figure 1-1. RS8228 Connected to a RS8398 Transceiver

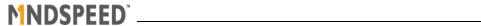

## 1.2 Logic Diagram

Figure 1-2 illustrates a logic diagram of the RS8228's functional modules. Pin descriptions are listed in Table 1-1.

Figure 1-2. RS8228 Logic Diagram

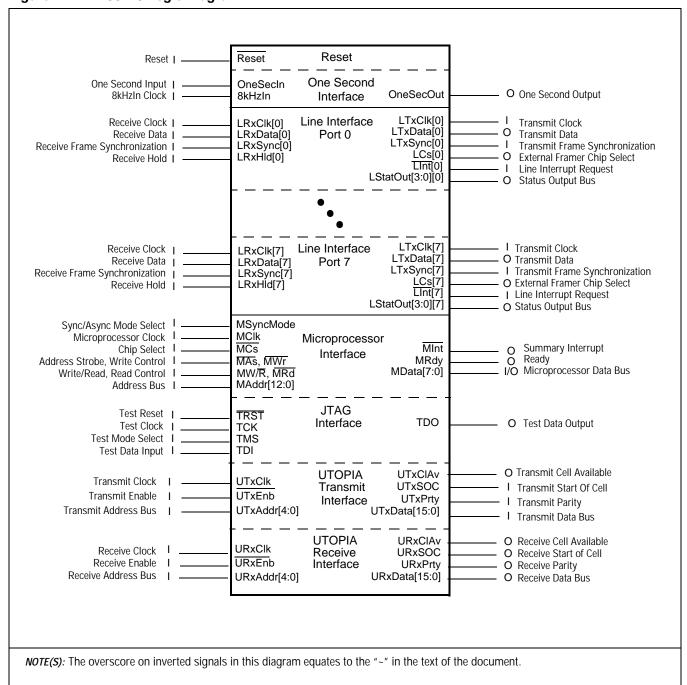

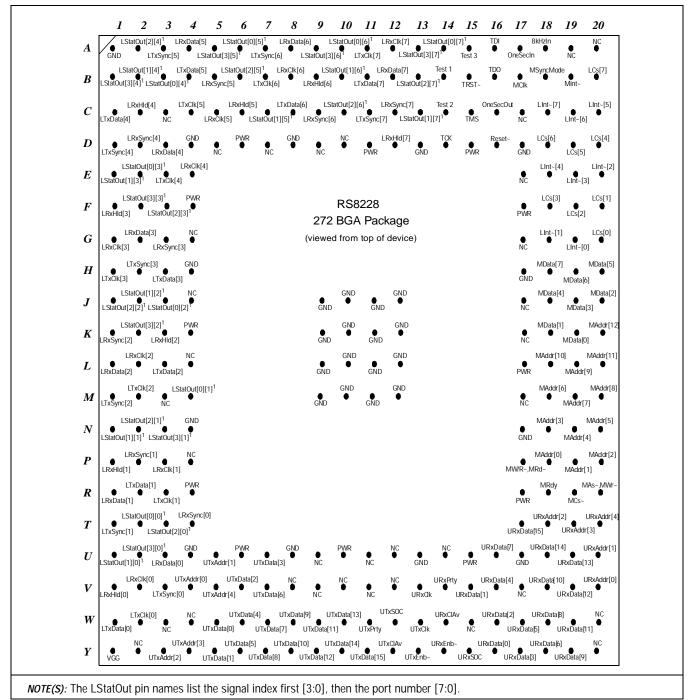

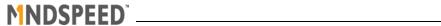

## 1.3 27 mm Pin Diagram and Definitions

Figure 1-3 illustrates a pinout diagram for the RS8228. It is a single CMOS integrated circuit packaged in a 272-pin BGA. All unused input pins should be connected to ground or power. Unused outputs should be left unconnected.

NOTE: The port numbers following the pin names in the Port Interface section represent each of the eight ports as follows:

LTxSync[0]—Line transmit sync for port 0.

LStatOut[3][0]—Line status output bit number 3 for port 0.

Figure 1-3. RS8228 27 mm Pinout Diagram (Top View)

**Table 1-1. RS8228 27 mm Pin Descriptions** (1 of 11)

|                  | Pin Label | Signal Name                         | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                                                               |

|------------------|-----------|-------------------------------------|-----|------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset            | Reset~    | Device Reset                        | D16 | TTL  |                    | Ι   | When asserted low, resets the device.                                                                                                                                                                                                                                                                                                     |

| Second Interface | OneSecIn  | One-Second Input                    | A17 | TTL  |                    | 1   | When asserted high, the device may latch and hold its status, provided either EnStatLat (bit 5) or EnCntLat (bit 4) in the MODE register (0x0202) are written to a logic 1. This pin is typically strobed at one-second intervals. It is typically driven by OneSecOut (pin C16) but can also be driven by an external one-second source. |

| One Second       | OneSecOut | One-Second Output                   | C16 | TTL  | 4 mA               | 0   | When active high, indicates that 8000 periods of the 8kHzIn input (pin A18) have passed. Typically active at one second intervals. Remains active for one period of the 8kHzIn pin. It typically drives OneSecIn.                                                                                                                         |

|                  | 8kHzIn    | One-Second<br>Reference Clock Input | A18 | TTL  | _                  | I   | A clock input used to derive OneSecOut (pin C16). Typically operates at a frequency of 8 kHz).                                                                                                                                                                                                                                            |

**Table 1-1. RS8228 27 mm Pin Descriptions** (2 of 11)

|                                      | Pin Label                                                                                                    | Signal Name                                           | No.                                           | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------|------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | LTxClk[0] LTxClk[1] LTxClk[2] LTxClk[3] LTxClk[4] LTxClk[5] LTxClk[6] LTxClk[6]                              | Line Transmit Clock<br>Input (ports 0–7)              | W2<br>R3<br>M2<br>H1<br>E3<br>C4<br>B7<br>A11 | TTL  | 1                  | -   | Used for the framer (line) transmit timing source. The polarity is set by TxClkPol (bit 3) in the IOMODE register (0x05).                                                                                    |

| 0-7)                                 | LTxData[0]<br>LTxData[1]<br>LTxData[2]<br>LTxData[3]<br>LTxData[4]<br>LTxData[5]<br>LTxData[6]<br>LTxData[7] | Line Transmit Data<br>Output (ports 0–7)              | W1<br>R2<br>L3<br>H3<br>C1<br>B4<br>C8<br>B11 | TTL  | 4 mA               | 0   | Used for serial transmit output data.                                                                                                                                                                        |

| Framer (Line) Interfaces (ports 0-7) | LTxSync[0] LTxSync[1] LTxSync[2] LTxSync[3] LTxSync[4] LTxSync[5] LTxSync[6] LTxSync[6]                      | Line Transmit Frame<br>Synchronization<br>(ports 0–7) | V3<br>T1<br>M1<br>H2<br>D1<br>A3<br>A7<br>C11 | TTL  | 1                  | 1   | When transferring framed data, must be connected to the framer's start-of-frame output. In general purpose mode, this pin is ignored. The polarity is set by TxMrkPol (bit 4) in the IOMODE register (0x05). |

| Fram                                 | LRxClk[0] LRxClk[1] LRxClk[2] LRxClk[3] LRxClk[4] LRxClk[5] LRxClk[6] LRxClk[6]                              | Line Receive Clock<br>Input (ports 0–7)               | V2<br>P3<br>L2<br>G1<br>E4<br>C5<br>B8<br>A12 | TTL  | _                  | 1   | Used for the framer (line) receive timing source. The polarity is set by RxClkPol (bit 5) in the IOMODE register (0x05).                                                                                     |

|                                      | LRxData[0] LRxData[1] LRxData[2] LRxData[3] LRxData[4] LRxData[5] LRxData[6] LRxData[7]                      | Line Receive Data<br>Input (ports 0–7)                | U3<br>R1<br>L1<br>G2<br>D3<br>A4<br>A8<br>B12 | TTL  | _                  | 1   | Used for serial receive input data.                                                                                                                                                                          |

**Table 1-1. RS8228 27 mm Pin Descriptions** (3 of 11)

|                                                  | Pin Label                                                                                                                                                                               | Signal Name                                          | No.                                                  | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | LRxSync[0] LRxSync[1] LRxSync[2] LRxSync[3] LRxSync[4] LRxSync[5] LRxSync[6] LRxSync[7]                                                                                                 | Line Receive Frame<br>Synchronization<br>(ports 0-7) | T4<br>P2<br>K1<br>G3<br>D2<br>B5<br>C9<br>C12        | TTL  | _                  | I   | When transferring framed data, must be connected to the framer's start-of-frame output. In general purpose mode, this pin is ignored. The polarity is set by RxSyncPol (bit 4) in the IOMODE register (0x05).                                                                                              |

| nued)                                            | LRxHId[0] Line Receiver Hold Input (ports 0-7) LRxHId[2] LRxHId[3] LRxHId[4] LRxHId[5] LRxHId[6] LRxHId[6] LRxHId[7]                                                                    |                                                      | V1<br>P1<br>K3<br>F1<br>C2<br>C6<br>B9<br>D12        | TTL  | _                  | ı   | Stops receive cell processing when asserted. The polarity is set by RxHIdPol (bit 7) in the IOMODE register (0x05). When asserted, all receiver state machines are held in reset. Tie to 3.3 V for normal operation.                                                                                       |

| Framer (Line) Interfaces (ports 0-7) (Continued) | LCs[0]       Line External Framer         LCs[1]       Chip Select         LCs[2]       (ports 0-7)         LCs[3]       LCs[4]         LCs[5]       LCs[6]         LCs[7]       LCs[7] |                                                      | G20<br>F20<br>F19<br>F18<br>D20<br>D19<br>D18<br>B20 | TTL  | 4 mA               | 0   | When asserted, the corresponding external framer will be selected. The polarity is set by CsPoI (bit 2) in the IOMODE register (0x05).                                                                                                                                                                     |

| Framer (Line) In                                 | Lint~[0]<br>Lint~[1]<br>Lint~[2]<br>Lint~[3]<br>Lint~[4]<br>Lint~[5]<br>Lint~[6]<br>Lint~[6]                                                                                            | Line Interrupt Request<br>(ports 0-7)                | G19<br>G18<br>E20<br>E19<br>E18<br>C20<br>C19<br>C18 | TTL  | _                  | ı   | When asserted low, the corresponding framer needs servicing. The RS8228 may be used to transfer the interrupt request to the microprocessor via MInt~ (pin B19) if it is enabled. These pins have pull-up resistors.                                                                                       |

|                                                  | LStatOut[3][0]<br>LStatOut[3][1]<br>LStatOut[3][2]<br>LStatOut[3][3]<br>LStatOut[3][4]<br>LStatOut[3][5]<br>LStatOut[3][6]<br>LStatOut[3][7]                                            | Line Status Output 3 (ports 0-7)                     | U2<br>N3<br>K2<br>F2<br>B1<br>A5<br>A9<br>A13        | TTL  | 4 mA               | 0   | Reflects port signals based on the value of StatSel (bits 0 and 1) in the IOMODE register (0x05):  LStatOut StatSelect RcvrHld[7:0] 00 NonMatch[7:0] 01 RxOvfl[7:0] 10 OutStat[3][7:0](0x07, bit 3) 11  Eight RcvrHld, NonMatch, and RxOvfl signals (0–7) have numbers that correspond to the eight ports. |

**Table 1-1. RS8228 27 mm Pin Descriptions** (4 of 11)

|                                                 | Pin Label                                                                                                                                    | Signal Name                         | No.                                            | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------|------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ned)                                            | LStatOut[2][0]<br>LStatOut[2][1]<br>LStatOut[2][2]<br>LStatOut[2][3]<br>LStatOut[2][4]<br>LStatOut[2][5]<br>LStatOut[2][6]<br>LStatOut[2][7] | Line Status Output 2 (ports 0-7)    | T3<br>N2<br>J1<br>F3<br>A2<br>B6<br>C10<br>B13 | TTL  | 4 mA               | 0   | Reflects various port signals based on the value of StatSel (0x05, bits 0 and 1):  LStatOut[3] StatSelect HECCorr[7:0] 00 IdleRcvd[7:0] 01 TxOvfl[7:0] 10 OutStat[2][7:0](0x07, bit 2) 11  Eight HECCorr, IDIRcvd, and TxOvfl signals (0–7) have numbers that correspond to the eight ports.             |

| Framer (Line) Interfaces (port 0-7) (Continued) | LStatOut[1][0]<br>LStatOut[1][1]<br>LStatOut[1][2]<br>LStatOut[1][3]<br>LStatOut[1][4]<br>LStatOut[1][5]<br>LStatOut[1][6]<br>LStatOut[1][7] | Line Status Output 1<br>(ports 0-7) | U1<br>N1<br>J2<br>E1<br>B2<br>C7<br>B10<br>C13 | TTL  | 4 mA               | 0   | This pin reflects various port signals depending on the value of StatSel (0x05, bits 0 and 1):  LStatOut[3] StatSelect HECDet[7:0] 00 CellRcvd[7:0] 01 SOCErr[7:0] 10 OutStat[1][7:0](0x07, bit 1) 11  Eight HECDet, CellRcvd, and SOCErr signals (0–7) have numbers that correspond to the eight ports. |

| Frame                                           | LStatOut[0][0]<br>LStatOut[0][1]<br>LStatOut[0][2]<br>LStatOut[0][3]<br>LStatOut[0][4]<br>LStatOut[0][5]<br>LStatOut[0][6]<br>LStatOut[0][7] | Line Status Output 0<br>(ports 0-7) | T2<br>M4<br>J3<br>E2<br>B3<br>A6<br>A10<br>A14 | TTL  | 4 mA               | 0   | This pin reflects various port signals depending on the value of StatSel (0x05, bits 0 and 1):  LStatOut[3] StatSelect LOCD[7:0] 00 CellSent[7:0] 01 ParErr[7:0] 10 OutStat[0][7:0](0x07, bit 0) 11  Eight LOCD, CellSent, and ParErr signals (0–7) have numbers that correspond to the eight ports.     |

**Table 1-1. RS8228 27 mm Pin Descriptions** (5 of 11)

|                          | Pin Label | Signal Name                                                       | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|-----------|-------------------------------------------------------------------|-----|------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | MCIk      | Microprocessor Clock                                              | B17 | TTL  |                    | _   | An 8–50 MHz clock signal input. The RS8228 samples the microprocessor interface pins (MCs~, MW/R~, MAs~, MAddr[6:0], and MData[7:0]) on the rising edge of this signal. The microprocessor interface output pins (MData[7:0], MInt~) are clocked on the rising edge of MClk.                                                                                                                                                         |

| Microprocessor Interface | MSyncMode | Microprocessor<br>Synchronous/<br>Asynchronous Bus<br>Mode Select | B18 | TTL  | _                  | I   | Selects synchronous or asynchronous bus mode, which determines the functions of two pins, MW/R~,MRd~ (pin P17) and MAs~,MWr~ (pin R20). A logic 1 selects the synchronous bus mode, compatible with Bt8230 and Bt8233. In this mode, these pins are defined as follows: MW/R~ (P17) and MAs~ (R20). A logic 0 selects the asynchronous SRAM-type bus mode. In this mode, the pins are defined as follows: MRd~ (P17) and MWr~ (R20). |

| Micr                     | MCs~      | Microprocessor Chip<br>Select                                     | R19 | TTL  | _                  | I   | When asserted low, the device is selected for read and write accesses. When asserted high, the device will not respond to input signal transitions on MClk, MW/R~, MRd~, or MAs~, MWr~. Additionally, when MCs~ is asserted high, the MData[7:0] pins are in a high-impedance state but the MInt~pin remains operational.  **NOTE(S): MCs~ must be asserted when using the LCs pins to select external framers.                      |

**Table 1-1. RS8228 27 mm Pin Descriptions** (6 of 11)

|                                      | Pin Label | Signal Name                            | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|-----------|----------------------------------------|-----|------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (pər                                 | MW/R~     | Microprocessor Write/<br>Read  or      | P17 | TTL  | _                  | ı   | When MSyncMode is asserted high, this pin is a read/write control pin. In this mode, when MW/R~ is asserted high, a write access is enabled and the MData[7:0] pin values will be written to the memory location indicated by the MAddr[6:0] pins. Also, when MW/R~ is asserted low in this mode, a read access is enabled and the memory location indicated by the MAddr[6:0] pins is read. Its value is placed on the MData[7:0] pins. Both read and write accesses assume the device is chip selected (MCs~ = 0), the address is valid (MAs~ = 0), and the device is not being reset (Reset~ = 1). |

| Microprocessor Interface (Continued) | MRd~      | Read Control                           |     |      |                    |     | When MSyncMode is asserted low, this pin is a read control pin. In this mode, when MRd~ is asserted low, a read access is enabled and the memory location indicated by the MAddr[6:0] pins is read. Its value is placed on the MData[7:0] pins. The read access assumes the device is chip selected (MCs~ = 0), a write access is not being requested (MWr~ = 1), and the device is not being reset (Reset~ = 1).                                                                                                                                                                                     |

| Microproc                            | MAs~      | Microprocessor<br>Address Strobe<br>or | R20 | TTL  | _                  | I   | When MSyncMode is asserted high, this pin is an address strobe pin. When the MAs~ pin is asserted low, it indicates a valid address, MAddr[6:0]. This signal is used to qualify read and write accesses.                                                                                                                                                                                                                                                                                                                                                                                              |

|                                      | MWr~      | Write Control                          |     |      |                    |     | When MSyncMode is asserted low, this pin is a write control pin. When MWr $\sim$ is asserted low, a write access is enabled and the MData[7:0] pin values will be written to the memory location indicated by the MAddr[6:0] pins. The write access assumes the device is chip selected (MCs $\sim$ = 0), a read access is not being requested (MRd $\sim$ = 1), and the device is not being reset (Reset $\sim$ = 1).                                                                                                                                                                                |

**Table 1-1. RS8228 27 mm Pin Descriptions** (7 of 11)

|                                      |           |                                     | •   |      |                    |     |                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|-----------|-------------------------------------|-----|------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | Pin Label | Signal Name                         | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                                                                                                                              |

|                                      | MAddr[12] | Microprocessor                      | K20 | TTL  | _                  | I   | These 13 bits are an address input for identifying the register                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[11] | Address Bus                         | L20 | TTL  |                    | I   | to access. Registers are mapped into the address space 0000–1FFF.                                                                                                                                                                                                                                                                                                                        |

|                                      | MAddr[10] |                                     | L18 | TTL  |                    | I   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[9]  |                                     | L19 | TTL  |                    | I   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[8]  |                                     | M20 | TTL  |                    | I   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[7]  |                                     | M19 | TTL  |                    | I   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[6]  |                                     | M18 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[5]  |                                     | N20 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[4]  |                                     | N19 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[3]  |                                     | N18 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MAddr[2]  |                                     | P20 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

| nued                                 | MAddr[1]  |                                     | P19 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

| Conti                                | MAddr[0]  |                                     | P18 | TTL  |                    | ı   |                                                                                                                                                                                                                                                                                                                                                                                          |

| ace (                                | MData[7]  | Microprocessor Data                 | H18 | TTL  | 8 mA               | I/O | A bidirectional data bus for transferring read and write data.                                                                                                                                                                                                                                                                                                                           |

| nterf                                | MData[6]  | Bus                                 | H19 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

| sorl                                 | MData[5]  |                                     | H20 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

| Microprocessor Interface (Continued) | MData[4]  |                                     | J18 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

| icrop                                | MData[3]  |                                     | J19 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

| Σ                                    | MData[2]  |                                     | J20 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MData[1]  |                                     | K18 | TTL  | 8 mA               | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MData[0]  |                                     | K19 | TTL  | 8 mA               | I/O |                                                                                                                                                                                                                                                                                                                                                                                          |

|                                      | MRdy      | Microprocessor<br>Ready             | R18 | TTL  | 4 mA               | 0   | When active high, the current read or write transaction has been completed. For a read transaction, the data is ready to be transferred to the microprocessor. For a write transaction, the data provided by the microprocessor has been written. This pin is an open drain output for an external wired OR logic implementation. An external pull-up resistor is required for this pin. |

|                                      | MInt~     | Microprocessor<br>Interrupt Request | B19 | TTL  | 2 mA               | 0   | When active low, the device needs servicing. It remains active until the pending interrupt is processed by the Interrupt Service Routine. This pin is an open drain output for an external wired OR logic implementation. See Section 2.4.6. An external pull-up resistor is required for this pin.                                                                                      |

**Table 1-1. RS8228 27 mm Pin Descriptions** (8 of 11)

|                 | Pin Label  | Signal Name              | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                            |

|-----------------|------------|--------------------------|-----|------|--------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1149.1a-1993)   | TRST~      | Test Reset               | B15 | TTL  |                    | I   | When asserted, the internal boundary-scan logic is reset. This pin has a pull-up resistor. Do not assert this reset unless a clock is provided on TCK. |

| 1149.1          | TCK        | Test Clock               | D14 | TTL  |                    | I   | Samples the value of TMS and TDI on its rising edge to control the boundary scan operations.                                                           |

| JTAG (see IEEE  | TMS        | Test Mode Select         | C15 | TTL  |                    | I   | Controls the boundary-scan Test Access Port (TAP) controller operation. This pin has a pull-up resistor.                                               |

| AG (            | TDI        | Test Data Input          | A16 | TTL  | _                  | I   | The serial test data input. This pin has a pull-up resistor.                                                                                           |

| 15              | TDO        | Test Data Output         | B16 | TTL  | 4 mA               | 0   | The serial test data output.                                                                                                                           |

|                 | UTxClk     | UTOPIA Transmit<br>Clock | W13 | TTL  |                    | 1   | A clock input used to synchronize transmitted data.                                                                                                    |

| nit             | UTxEnb~    | Transmit Enable          | Y13 | TTL  | _                  | I   | Enables data transmission when asserted low.                                                                                                           |

| UTOPIA Transmit | UTxAddr[0] | LSB                      | V4  | TTL  | _                  | I   | The address of the PHY device being selected for                                                                                                       |

| PIA T           | UTxAddr[1] |                          | U5  | TTL  |                    | I   | transmission. Address 11111 (31 decimal) indicates a null PHY port.                                                                                    |

| UTO             | UTxAddr[2] | UTOPIA Transmit          | Y3  | TTL  |                    | I   |                                                                                                                                                        |

|                 | UTxAddr[3] | Address                  | Y4  | TTL  |                    |     |                                                                                                                                                        |

|                 | UTxAddr[4] | MSB                      | V5  | TTL  |                    | I   |                                                                                                                                                        |

**Table 1-1. RS8228 27 mm Pin Descriptions** (9 of 11)

|                             |             |                                   | -   |      | Deimon             |     |                                                                                                                                                                                                                                                                               |

|-----------------------------|-------------|-----------------------------------|-----|------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | Pin Label   | Signal Name                       | No. | Туре | Driver<br>Strength | I/O | Description                                                                                                                                                                                                                                                                   |

|                             | UTxData[0]  | LSB                               | W5  | TTL  |                    |     | Transmit data from the ATM layer.                                                                                                                                                                                                                                             |

|                             | UTxData[1]  |                                   | Y5  | TTL  |                    |     |                                                                                                                                                                                                                                                                               |

|                             | UTxData[2]  |                                   | V6  | TTL  |                    |     |                                                                                                                                                                                                                                                                               |

|                             | UTxData[3]  | UTOPIA Transmit Data              | U7  | TTL  |                    | -   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[4]  |                                   | W6  | TTL  |                    | I   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[5]  |                                   | Y6  | TTL  |                    | -   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[6]  |                                   | V7  | TTL  |                    | I   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[7]  |                                   | W7  | TTL  |                    | I   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[8]  |                                   | Y7  | TTL  |                    |     |                                                                                                                                                                                                                                                                               |

| (peni                       | UTxData[9]  |                                   | W8  | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

| ontir                       | UTxData[10] |                                   | Y8  | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

| nit (C                      | UTxData[11] |                                   | W9  | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

| UTOPIA Transmit (Continued) | UTxData[12] |                                   | Y9  | TTL  |                    | -   |                                                                                                                                                                                                                                                                               |

| PIA T                       | UTxData[13] |                                   | W10 | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

| UTO                         | UTxData[14] |                                   | Y10 | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

|                             | UTxData[15] | MSB                               | Y11 | TTL  |                    | _   |                                                                                                                                                                                                                                                                               |

|                             | UTxPrty     | UTOPIA Transmit<br>Parity Input   | W11 | TTL  |                    | _   | The parity calculated over the UTxData bus. BusWidth (bit 0) in the IOMODE register (0x0202) determines whether parity is checked over UTxData[7:0] or UTxData[15:0]. OddEven (bit 2) in the UTOP1 register (0x0D) determines whether this pin represents even or odd parity. |

|                             | UTxSOC      | UTOPIA Transmit<br>Start of Cell  | W12 | TTL  | 1                  | I   | Indicates the first byte of valid cell data transmitted when asserted high.                                                                                                                                                                                                   |

|                             | UTxCIAv     | UTOPIA Transmit Cell<br>Available | Y12 | TTL  | 8 mA               | 0   | Indicates a FIFO full condition or Cell Available condition, depending upon UTOPIA HandShake (bit 1) in the MODE register (0x0202). An external pull-down resistor is required for this pin.                                                                                  |

|                             | URxClk      | UTOPIA Receive Clock              | V13 | TTL  |                    | 1   | A clock input used to synchronize received data.                                                                                                                                                                                                                              |

|                             | URxEnb~     | Receive Enable                    | Y14 | TTL  | _                  | -   | Enables data reception when asserted low.                                                                                                                                                                                                                                     |

| ceive                       | URxAddr[0]  | LSB                               | V20 | TTL  | _                  | 1   | The address of the PHY device being selected for reception.                                                                                                                                                                                                                   |

| UTOPIA Receive              | URxAddr[1]  |                                   | U20 | TTL  |                    | ı   | The address range is 0–30. Address 11111 (31 decimal) indicates a null PHY port.                                                                                                                                                                                              |

| ITOP                        | URxAddr[2]  | UTOPIA Receive                    | T18 | TTL  |                    | -   | ·                                                                                                                                                                                                                                                                             |

|                             | URxAddr[3]  | Address                           | T19 | TTL  |                    | -   |                                                                                                                                                                                                                                                                               |

|                             | URxAddr[4]  | MSB                               | T20 | TTL  |                    | I   |                                                                                                                                                                                                                                                                               |

**Table 1-1. RS8228 27 mm Pin Descriptions** (10 of 11)