- Fast Multiplication . . . 5-Bit Product in 26 ns Typ

- Power Dissipation . . . 110 mW Typical

- Latch Outputs for Synchronous Operation

- Expandable for m-Bit-by-n-Bit Applications

- Fully Compatible with Most TTL and Other Saturated Low-Level Logic Families

- Diode-Clamped Inputs Simplify System Design

## description

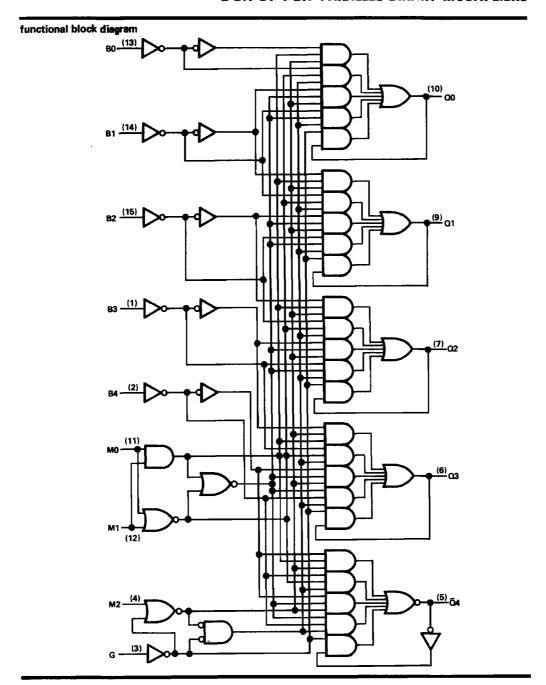

These low-power Schottky circuits are designed to be used in parallel multiplication applications. They perform binary multiplication in two's-complement form, two bits at a time.

The M inputs are for the multiplier bits and the B inputs are for the multiplicand. The Q outputs represent the partial product as a recoded base-4 number. This recoding effectively reduces the Wallace-tree hardware requirements by a factor of two.

The outputs represent partial products in one'scomplement form generated as a result of multiplication. A simple rounding scheme using two additional gates is needed for each partial product to generate two's complement.

The leading (most-significant) bit of the product is inverted for ease in extending the sign to square (left justify) the partial-product bits.

The SN54LS261 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to 125°C; the SN74LS261 for operation from 0°C to 70°C.

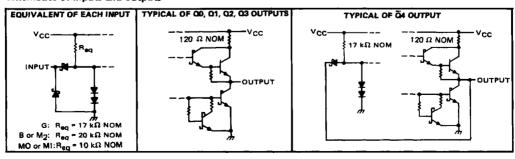

schematics of inputs and outputs

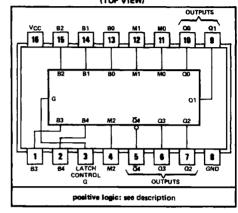

SN54LS261 ... J OR W PACKAGE SN74LS261 ... J OR N PACKAGE (TOP VIEW)

#### **FUNCTION TABLE**

|         | OUTPUTS    |    |    |     |            |                |            |     |

|---------|------------|----|----|-----|------------|----------------|------------|-----|

| LATCH   | MULTIPLIER |    |    | ō4  | 03         |                |            | 00  |

| CONTROL | M2         | M1 | MO | Q4  |            |                |            | CO  |

| L       | х          | ×  | X  | Q40 | 030        | 020            | Q10        | 000 |

| H       | Ł          | L  | Ł  | н   | L          | L              | L          | Ł.  |

| H       | L          | L  | н  | B̃4 | B4         | В3             | <b>B</b> 2 | 81  |

| н       | L          | н  | L  | B4  | B4         | вз             | <b>B2</b>  | В1  |

| н       | L          | н  | н  | B4  | В3         | B2             | <b>B</b> 1 | во  |

| н       | н          | L  | L  | B4  | БЗ         | B2             | <b>B</b> 1 | BO  |

| н       | н          | L  | н  | B4  | B4         | B <sub>3</sub> | Ē2         | B1  |

| н       | н          | н  | L  | B4  | <b>B</b> 4 | B <sub>3</sub> | <u>B</u> 2 | B1  |

| н       | н          | Н  | н  | н   | L          | L              | L          | L   |

H = high level, L = low level, X = irrelevant

Q40...Q00 = The logic level of the same output before the high-to-low transition of G.

B4 . . . B0 = The logic level of the indicated multiplicand (B) input.

# TYPES SN54LS261, SN74LS261 2-BIT-BY-4-BIT PARALLEL BINARY MULTIPLIERS

74

# TYPES SN54L8261 SN74LS261 2-BIT-BY-4-BIT PARALLEL BINARY MULTIPLIERS

REVISED OCTOBER 1976

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1) |             | <br>7V            |

|----------------------------------------------|-------------|-------------------|

| Input voltage                                |             | <br>7V            |

| Operating free-air temperature range         | : SN54LS261 | <br>55°C to 125°C |

|                                              | SN74LS261   | <br>0°C to 70°C   |

| Storage temperature range                    |             | <br>65°C to 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

## recommended operating conditions

|                                       |             | SN54LS261 |     |      | SN74LS261 |             |      | UNIT |

|---------------------------------------|-------------|-----------|-----|------|-----------|-------------|------|------|

|                                       |             | MIN       | NOM | MAX  | MIN       | NOM         | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>       |             | 4.5       | 5   | 5.5  | 4.75      | 5           | 5.25 | >    |

| High-level output current, IOH        |             | Г         |     | -400 |           |             | -400 | μΑ   |

| Low-level output current, IOL         |             |           |     | 4    |           |             | 8    | mA   |

| Width of enable pulse, t <sub>W</sub> |             | 25        |     |      | 25        |             |      | ns   |

| Catura sima a                         | Any M input | 174       |     |      | 17↓       |             |      | ns   |

| Setup time, t <sub>su</sub>           | Any B input |           | 15↓ |      | 151       | i <b>\$</b> |      | 118  |

| Hala e                                | Any M input |           |     |      | 01        |             |      |      |

| Hold time, th                         | Any 8 input | Ot        |     |      | O+        |             |      | ns   |

| Operating free-air temperature, TA    |             |           |     | 125  | 0         |             | 70   | °C   |

<sup>‡</sup>The arrow indicates that the falling edge of the enable pulse is used for reference. electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                |                              | 700                                                              |                                                   | .+         | L S | SN54L\$261 |      | S    |       |      |              |

|--------------------------|------------------------------|------------------------------------------------------------------|---------------------------------------------------|------------|-----|------------|------|------|-------|------|--------------|

|                          |                              | TEST CONDITIONS <sup>†</sup>                                     |                                                   |            | MIN | TYP*       | MAX  | MIN  | TYP‡  | MAX  | UNIT         |

| VIH                      | High-level input voltage     |                                                                  |                                                   |            | 2   |            |      | 2    |       |      | <b>v</b>     |

| VIL                      | Low-level input voltage      |                                                                  |                                                   |            | Ť – |            | 0.7  |      |       | 8.0  | V            |

| VIK                      | Input clamp voltage          | VCC = MIN,                                                       | I <sub>1</sub> = -18 mA                           |            | Ι   |            | -1.5 |      |       | -1.5 | V            |

| νон                      | High-level output voltage    | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = V <sub>IL</sub> max, | V <sub>1H</sub> = 2 V,<br>I <sub>OH</sub> =400 μ/ | <u> </u>   | 2.5 | 3,4        |      | 2.7  | 3.4   |      | v            |

|                          | I am total amanda salana     | V <sub>CC</sub> = MIN,                                           | V <sub>IH</sub> = 2 V,                            | IOL * 4 mA |     | 0.25       | 0.4  |      | 0.25  | 0.4  | V            |

| VOL                      | Low-level output voltage     | V <sub>I</sub> L = V <sub>I</sub> L max                          |                                                   | IOL = 8 mA |     |            |      |      | .0.35 | 0.5  | 1 °          |

|                          | Input current at             | 14 14AV                                                          | V1 ≈ 7 V                                          | MO or MI   |     |            | 0.2  |      |       | 0,2  |              |

| H                        | maximum input voltage        | V <sub>CC</sub> = MAX, V <sub>I</sub> = 7 V                      |                                                   | All others |     |            | 0.1  |      |       | 0,1  | mA           |

|                          |                              | MANY                                                             | V <sub>i</sub> = 2.7 V MO or MI<br>All others     | MO or MI   |     |            | 40   |      |       | 40   | μΑ           |

| 414                      | High-level input current     | evel input current V <sub>CC</sub> = MAX,                        |                                                   | All others | 1   | -          | 20   |      |       | 20   | 1 <i>"</i> ^ |

|                          | L'au lauri ianus aurumas     | level input current VCC = MAX,                                   | V <sub>1</sub> = 0.4 V M                          | MO or MI   | Ì   |            | -0.8 |      |       | -0,8 | mA           |

| IIL Low-level input curr | Cow-level impor current      |                                                                  | All others                                        |            | 0.4 |            |      | -0.4 |       |      |              |

| ios                      | Short-circuit output current | V <sub>CC</sub> = MAX                                            |                                                   |            | -20 |            | 100  | -20  |       | 100  | mA           |

| Icc                      | Supply current               | V <sub>CC</sub> = MAX,<br>Outputs open.                          | All inputs at 0                                   | V,         | 22  |            | 38   |      | 20    | 40   | mA           |

$\ddagger$ All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C. §Not more than one output should be shorted at a time and duration of the output short-circuit should not exceed one second.

## switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER¶  | FROM<br>(INPUT) | TO (OUTPUT) | TEST CONDITIONS     | MIN | ТҮР | MAX | UNIT |

|-------------|-----------------|-------------|---------------------|-----|-----|-----|------|

| tPLH .      | Enable G        | Any Q       |                     |     | 22  | 35  | ns   |

| *PHL        | Eliable G       | Any C       | CL = 15 pF,         |     | 20  | 30  | · ns |

| ФLН         | Any M input     | Any Q       | C[=18βr,<br>R[=2kΩ, |     | 25_ | 40  | ns   |

| tPHL        | Any or input    | Any C       | See Note 2          |     | 22  | 35  | ns   |

| ФГН         | Any B input     | Any Q       | 386 NOTE 2          |     | 27  | 42  | ns   |

| <b>tPHL</b> | Any B imput     | Anyu        |                     |     | 24  | 37  | ns   |

<sup>¶</sup> tp\_H ≡ propagation delay time, low-to-high-level output; tpHL = propagation delay time, high-to-low-level output.

NOTE 2: Load circuit and voltage waveforms are shown on page 3-11.

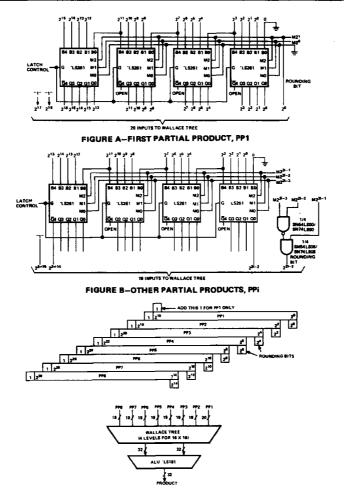

## TYPICAL APPLICATION DATA

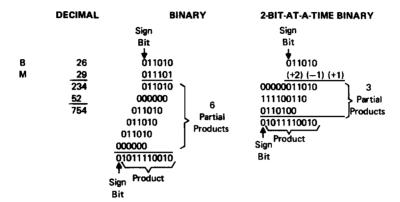

Multiplication of the numbers 26 (multiplicand) by 29 (multiplier) in decimal, binary, and 2-bit-at-a-time-binary is shown here:

Two points should be noted in the two-bit-at-a-time-binary example above. First, in positioning the partial products beneath each other for final addition, each partial product is shifted two places to the left of the partial products above it instead of one place as is done in regular multiplication. Second, the msb of the partial product (the sign bit) is extended to the sign-bit column of the final answer.

A substantial reduction of multiplication time, cost, and power is obtained by implementing a parallel partial-product-generation scheme using a 2-bit-at-a-time algorithm, followed by a Wallace Tree summation.

Partial-product-generation rules of the algorithm are:

Examine two bits of multiplier M plus the next lower bit. For the first partial product (PP1) the next lower bit is zero.

# TYPES SN54LS261, SN74LS261 2-BIT-BY-4-BIT PARALLEL BINARY MULTIPLIERS

### TYPICAL APPLICATION DATA

2. Generate partial product (PPi) as shown in the following table:

| MULTIPLIER BITS FROM<br>STEP 1 |       |       | OPERATOR<br>SYMBOL | TO OBTAIN PARTIAL PRODUCT                           |  |

|--------------------------------|-------|-------|--------------------|-----------------------------------------------------|--|

| 221-1                          | 221-2 | 221-3 | STMBUL             |                                                     |  |

| 0                              | 0     | 0     | 0                  | Replace multiplicand by zero                        |  |

| 0                              | 0     | 1     | +1 B               | Copy multiplicand                                   |  |

| 0                              | 1     | 0     | +1 B               | Copy multiplicand                                   |  |

| 0                              | 1     | 1     | +2 B               | Shift multiplicand left one bit                     |  |

| 1                              | 0     | 0     | -2 B               | Shift two's complement of multiplicand left one bit |  |

| 1                              | 0     | 1     | -1 B               | Replace multiplicand by two's complement            |  |

| 1                              | 1     | 0     | -1 B               | Replace multiplicand by two's complement            |  |

| 1                              | 1     | 1     | 0                  | Replace multiplicand by zero                        |  |

- 3. Weight the partial products by indexing each two places left relative to the next-less-significant product.

- 4. Extend the most-significant bit of the partial product to the sign-bit place value of the final product.

#### **EXAMPLE OF ALGORITHM**

| M = 29 = 011101 | Operator<br>Symbol | B = 26 = 011010 |

|-----------------|--------------------|-----------------|

| ابب<br>010 رب   | +1 B               | 00000011010     |

| ↓1i0            | -1B                | 111100110       |

| 0 <b>i</b> 1    | +2 B               | 0110100         |

The summation of these partial products was shown in the 2-bit-at-a-time binary multiplication example above.

The 'LS261 generates partial products according to this algorithm with two exceptions:

- The one's complement is generated for the cases requiring the two's complement. The two's complement can be

obtained by adding one to the one's complement; this rounding can be done by using one NAND gate and one AND

gate as shown in Figure B.

- The most-significant bit is complemented to reduce the hardware required to extend the sign bit. This extension can be accomplished by adding a hard-wired logic 1 in bit position 2<sup>2i+15</sup> of each partial product and also in bit position 2<sup>16</sup> of the first partial product (PP1).

# TYPES SN54LS261, SN74LS261 2-BIT-BY-4-BIT PARALLEL BINARY MULTIPLIERS

FIGURE C-MANIPULATION OF PARTIAL PRODUCTS FOR ENTRY INTO WALLACE TREE

In general, the 4 x 2 bit 'LS261 can be expanded for use in  $4m \times 2n$  bit multipliers. Partial-product generation uses  $m \times n$  'LS261s  $m \times n \div 16$  'LS00s, and  $m \times n \div 16$  'LS08s. The size of the Wallace tree and ALU requirements vary depending on the size of the problem. The count for the  $16 \times 16$  bit multiplier is:

- 32 SN54LS261/SN74LS261

- 2 SN54LS00/SN74LS00

- 2 SN54LS08/SN74LS08

- 56 SN54LS183/SN74LS183

- 7 SN54LS181/SN74LS181

- 2 SN54S182/SN74S182