Thick-film Hybrid Integrated Circuit (HIC)

No. 4375

7-band, 2-channel Electronic Graphic Equalizer

# Overview

The STK301-020 is a hybrid IC (HIC) for electronically controlled graphic equalizer applications and is equipped with on-chip electronic volume for 7-band, 2-channel graphic equalization thereby permiting one-touch up-down control of all band gains. The STK301-020 is a hybrid IC which combines SC system and photoresist techniques with folded board construction while incorporating Sanyo's unique insulated metal substrate technology (IMST) to the base.

# Applications

- Car stereos

- · Portable radio-cassette players

- · Home stereos

## **Features**

- All bands are set for L/R simultaneous 2 dB incremental operation (typ).

- All bands are equipped with 13 positions and range between +12 dB maximum boost to -12 dB maximum cut.

- Crossover frequencies include fo; 60 Hz, 150 Hz, 400 Hz, 1 kHz, 2.5 kHz, 6 kHz and 15 kHz.

- The following features can be made available with an electronic graphic equalizer system which incorporates the 3-IC construction consisting of the STK301-020, a controller (LC7060 or universal microcontroller such as LC6502) along with the display LSI (LC7560→LCD, LC7565→FLT, LED):

- 1) One-touch up-down control of all band gains.

- 2) Immediate recall of preferred frequency levels tailored to suit musical selections. This is possible using preset functions to retrieving items from one-touch memory.

- 3) Such functions as setting all bands to 0 dB (flat function), or switching frequency characteristics from 0 dB to center (reverse function) may be simply performed with supported software.

- 4) Dual control lines permit mutual use with display LSI and help to simplify wiring between microcontroller and LSI.

# Specifications

Absolute Maximum Ratings at  $T_2 = 25^{\circ}C$ ,  $V_{cc} = 0V$

| ings at ta = 25°C, v                 | SS = UV                                                                                                                                          |                                                                                                                                                                                 | unit                                                 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| V <sub>DD</sub> -V <sub>EE</sub> max |                                                                                                                                                  | 16                                                                                                                                                                              | V                                                    |

| V <sub>CC</sub> 1 max                |                                                                                                                                                  | 20                                                                                                                                                                              | V                                                    |

| V <sub>CC</sub> 2 max                |                                                                                                                                                  | 7                                                                                                                                                                               | ν                                                    |

| V <sub>1</sub> 1                     | CLK, DI, IN1, IN2                                                                                                                                | 0 to $V_{CC}^2 + 0.3$                                                                                                                                                           | V                                                    |

| V <sub>1</sub> 2                     | CLK, DI, IN1, IN2                                                                                                                                | $V_{EE} = -0.3 \text{ to } V_{DD} + 0.3$                                                                                                                                        | ٧                                                    |

| Pd max                               |                                                                                                                                                  | 1080                                                                                                                                                                            | mW                                                   |

| Topg                                 |                                                                                                                                                  | -20 to $+70$                                                                                                                                                                    | °C                                                   |

| Tstg                                 |                                                                                                                                                  | -40 to +100                                                                                                                                                                     | °C                                                   |

|                                      | V <sub>DD</sub> -V <sub>EE</sub> max<br>V <sub>CC</sub> 1 max<br>V <sub>CC</sub> 2 max<br>V <sub>1</sub> 1<br>V <sub>1</sub> 2<br>Pd max<br>Topg | V <sub>CC</sub> 1 max         V <sub>CC</sub> 2 max         V <sub>1</sub> 1       CLK, D1, IN1, IN2         V <sub>1</sub> 2       CLK, D1, IN1, IN2         Pd max       Topg | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

Specifications and information herein are subject to change without notice.

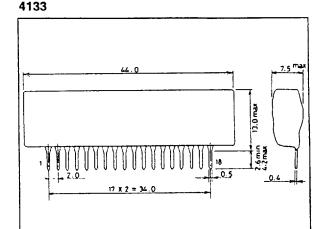

# **Package Dimensions**

unit: mm

SANYO Electric Co., Ltd. Semiconductor Business Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

| Recommended Operational Voltage at Ta = 25 °C, $ m V_{SS}$ = $ m 0~V$ |                                    |                                                                 |                                             |                        |                     | unit        |        |

|-----------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------|---------------------------------------------|------------------------|---------------------|-------------|--------|

| Supply voltage                                                        | V <sub>DD</sub> -V <sub>EE</sub> , | V <sub>CC</sub> I                                               | $V_{EE} = V_{SS} = 0V$                      | S = 0V 14              |                     | V           |        |

| orphis con-go                                                         | V <sub>CC</sub> 2                  | CC                                                              | $V_{EE} = V_{SS} = 0V$                      |                        |                     | V           |        |

| Allowable Operating C                                                 | onditions a                        | $t Ta = 25^{\circ}C, V$                                         | $_{SS} = 0V$                                |                        |                     | unit        |        |

| Supply voltage                                                        | V <sub>DD</sub> -V <sub>EE</sub> , |                                                                 |                                             | 7.5 to 15.0            |                     | V           |        |

|                                                                       | V <sub>CC</sub> 2                  |                                                                 |                                             | 4.                     | 5 to 5.5            | V           |        |

| "H" Level input voltage                                               | V <sub>IH</sub>                    |                                                                 | CLK, DI                                     | 0.8V <sub>CC</sub> 2 t | o V <sub>CC</sub> 2 | ٧           |        |

| "L" Level input voltage                                               | ν <sub>ιι.</sub>                   |                                                                 | CLK, DI                                     | 0                      | .2V <sub>CC</sub> 2 | ٧           |        |

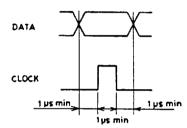

| Input pulse width                                                     | t <sub>et</sub> w                  |                                                                 | CLK                                         |                        | 1 to                | μs          |        |

| Sctup time                                                            | t <sub>setup</sub>                 |                                                                 | DI                                          | 1 to                   |                     | μs          |        |

| Hold time                                                             | thold                              |                                                                 | DI                                          |                        | 1 to                | μs          |        |

| Operational frequency                                                 | forz                               |                                                                 | CLK                                         |                        | to 330              | kHz         |        |

| perating Characteris                                                  |                                    |                                                                 |                                             |                        |                     |             |        |

| t Ta = $25^{\circ}$ C, $V_{SS} = V_{EE}$                              | $= 0V, V_{DD} =$                   | $V_{CC}1 = 14V, V$                                              | $V_{\rm CC}2 = 5V$ , $f = 1kHz$             |                        |                     |             |        |

| All bands flat, via specified Test Circuit                            |                                    |                                                                 |                                             |                        | typ                 | max         | បរា    |

| Current consumption                                                   | I <sub>DD</sub>                    | [v <sub>n</sub> = v <sub>m</sub> = 0                            | $V_1 V_{DD} = V_{CC} I = 14V_1$             |                        |                     | 1           | m      |

| ·                                                                     | I <sub>CC</sub> I                  | $V_{CC}2 = 5V$                                                  | $V, V_{DD} = V_{CC}I = 14V,$                |                        | 23                  | 32          | m      |

|                                                                       | I <sub>CC</sub> 2                  | _                                                               |                                             |                        |                     | 1           | m      |

| Current consumption 2                                                 | <sup>‡</sup> DD                    |                                                                 | $V_{DD}/V_{EE} = \pm 7V$                    |                        | 23                  | 1<br>32     | m      |

|                                                                       | I <sub>CC</sub> 1                  |                                                                 | $V_{DD}/V_{EE} = \pm 7V$                    | 4.0                    | -1.8                | +1.2        | ď      |

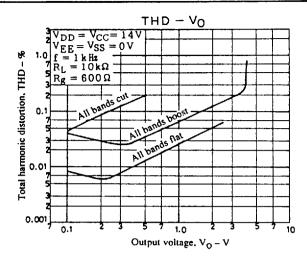

| Voltage gain                                                          | VG                                 | V <sub>IN</sub> = -10dB                                         |                                             | -4.8                   | 0.02                | +1.2<br>0.1 | 9      |

| Total harmonic distortion                                             | THD                                | $f = 1 \text{kHz}$ , $V_0 = 1 \text{V}$ , $30 \text{kHz L.P.F}$ |                                             | 45                     | 0.02<br>55          | 0.1         | d      |

| Crosstalk                                                             | C.T.                               | $f = 20kHz$ , $V_{IN} = 0dBm$                                   |                                             | 43                     | 33<br>7             | 40          | μ      |

| Output noise voltage                                                  | V <sub>NO</sub>                    | $Rg = 0\Omega, 101$                                             | Iz to 30kHz B.P.F                           | ,                      | ,                   | +1          | η<br>d |

| Setting error                                                         | ΔB                                 |                                                                 | 7                                           | -1                     |                     |             | ď      |

| Frequency response                                                    | (I)                                | f = 60Hz                                                        | •                                           | ±10<br>±10             | ±12<br>±12          | ±14<br>±14  | d      |

|                                                                       | ſ(2)                               | f = 150Hz                                                       | When operating at f = 1 kHz,                |                        | ±12                 | ±14         | ď      |

|                                                                       | f(3)                               | f = 400Hz<br>f = 1kHz                                           | all bands flat and                          | ±10                    | ±12                 | ±14         | ,      |

|                                                                       | f (4)<br>f (5)                     | f = 2.5k                                                        | $V_0 = -10 \text{ dB set at } 0 \text{ dB}$ | ±10                    | ±12                 | ±14         | d      |

|                                                                       | f (6)                              | f = 6kHz                                                        | 10 = -10 00 301 01 00                       | ±10                    | ±12                 | ±14         |        |

|                                                                       |                                    |                                                                 | •                                           |                        |                     |             |        |

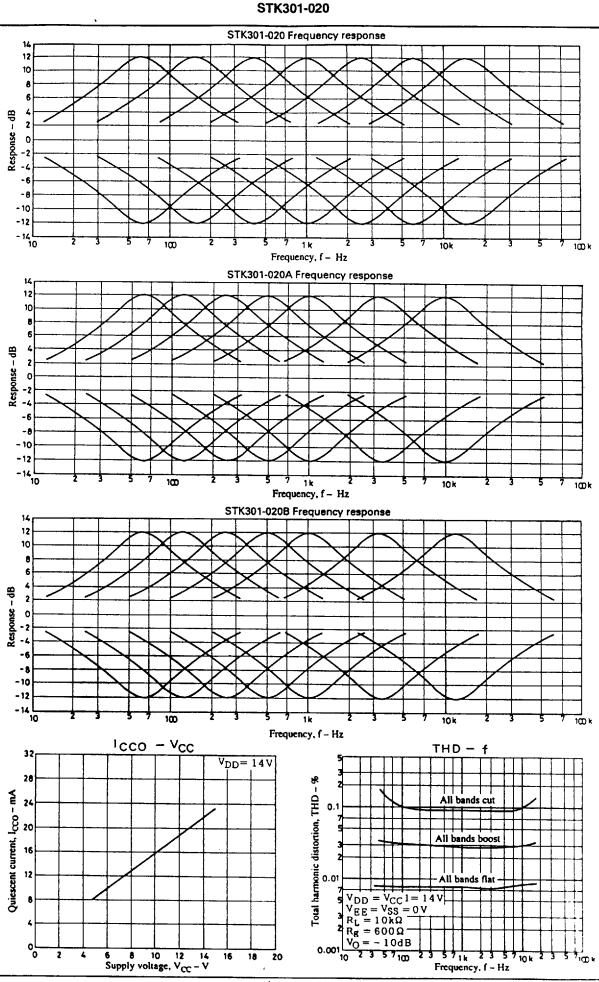

In addition to the above items, the STK301-020 is joined by STK301-020A and STK301-020B which differ in crossover frequency.

| IC name     | f (1) | f (2) | f (3) | f (4) | f (5)  | f (6)  | f (7) |

|-------------|-------|-------|-------|-------|--------|--------|-------|

| STK301-020  | 60Hz  | 150Hz | 400Hz | 1kHz  | 2.5kHz | 6kHz   | 15kHz |

| STK301-020A | 60Hz  | 125Hz | 250Hz | 500Hz | 1kHz   | 3.5kHz | 10kHz |

| STK301-020B | 60Hz  | 125Hz | 250Hz | 500Hz | 1kHz   | 3.5kHz | 12kHz |

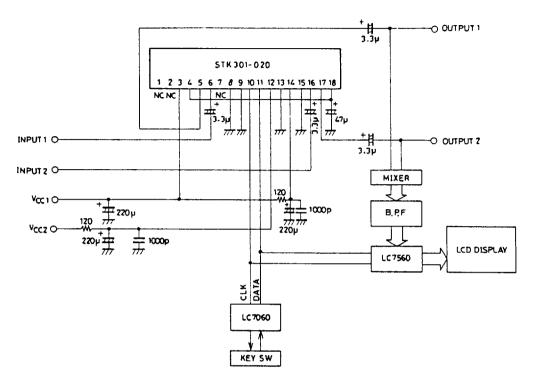

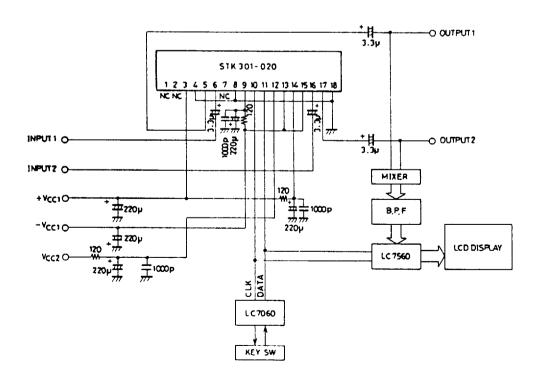

# **Application Circuit Example**

# ■ + Power Supply

## **■** ± Power Supply

# **Pin Descriptions**

| Pin No. | Pin name                 |                                                                                                                                                             | Functions                                                                                                                                                                  |  |  |  |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 3       | +V <sub>CC</sub> 1       | Power supply pin used for + power supply to IC2 and IC3 graphic equalizer.                                                                                  |                                                                                                                                                                            |  |  |  |

| 4, 18   | DC                       | Pin for 1/2 V <sub>CC</sub> 1 decoupling capacitor of graphic equalizer iC. When shortened, power supply becomes more effective and ripples are vulnerable. |                                                                                                                                                                            |  |  |  |

| 5       | OUTPUT 1                 | Output pin 1.                                                                                                                                               |                                                                                                                                                                            |  |  |  |

| 6       | INPUT 1                  | Input Impedance for input pln 1 rated at approximately 60Ω (1 kHz, flat).                                                                                   |                                                                                                                                                                            |  |  |  |

| 8       | V <sub>SS</sub>          | Power supply pin connected to ground (GND).                                                                                                                 |                                                                                                                                                                            |  |  |  |

| 9       | V <sub>EE</sub>          | Power supply pin used for audio signal power supply to electronic volume section. When single power supply is used, connect to V <sub>SS</sub> .            |                                                                                                                                                                            |  |  |  |

| 10      | CLK                      | _                                                                                                                                                           | Input pin for data from CPU according to Schmitt inverter format.                                                                                                          |  |  |  |

| 11      | DI                       |                                                                                                                                                             | Input pin for clock from the CPU according to Schmitt inverter format.                                                                                                     |  |  |  |

| 12      | +V <sub>CC</sub> 2       | Power supply pin rated at +5 V (typ). Make sure that V <sub>CC</sub> 2 does not onset before V <sub>DD</sub> .                                              |                                                                                                                                                                            |  |  |  |

| 13      | GND (-V <sub>CC</sub> 1) | Power supply pin for ground (- power supply) of IC2 and IC3 graphic equalizer.                                                                              |                                                                                                                                                                            |  |  |  |

| 14      | V <sub>DD</sub>          | Power supply pin used for audio signal power supply to electronic volume section.                                                                           |                                                                                                                                                                            |  |  |  |

| 15      | S                        |                                                                                                                                                             | Select pin for applications using two ICs. Input "1" to initiate key code 7C3 for connecting to $V_{DD}$ . Input "2" to initiate key code 7C2 for connecting to $V_{EE}$ . |  |  |  |

| 16      | INPUT 2                  | Input impedance for input pin 2 rated at approximately 60Ω (1 kHz, flat).                                                                                   |                                                                                                                                                                            |  |  |  |

| 17      | OUTPUT 2                 | Output pin 2.                                                                                                                                               |                                                                                                                                                                            |  |  |  |

Note:

- 1. Pins 1, 2, 7 are designated as NC pins (pins with no connections).

- 2. Refer to LC7522 or LC7523 specifications concerning pins which do not appear here and are hybrid IC (HIC) pins connected directly to a LC7522 or LC7523 pins.

# **Description of Operation**

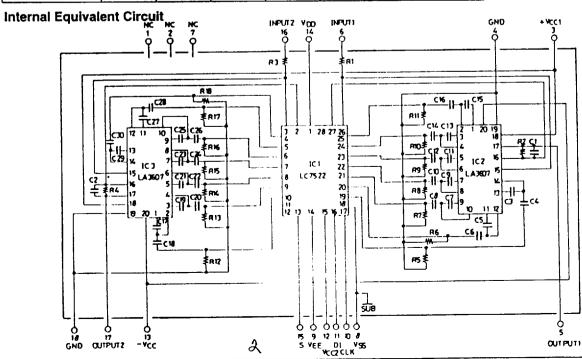

The STK301-020 is a hybrid IC (HIC) with a 7 – component 2-channel construction for electronically controlled graphic equalizer applications. It employees a LC7522 for graphic equalizer electronic volume and a LA3607 for 7 – component graphic equalizer functions.

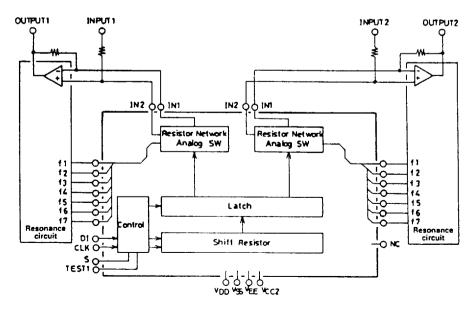

# **Equivalent Circuit Block Diagram**

Fig. 1 Equivalent Circuit Block Diagram

Pins f(1) through f(7) are used as pin connections for the LC7522 band filter. Supported frequencies and their pin assignments are listed in the following.

| Pin Name | Frequency |

|----------|-----------|

| f(1)     | 60Hz      |

| f (2)    | 150Hz     |

| f (3)    | 400Hz     |

| f (4)    | 1kHz      |

| f (5)    | 2.5kHz    |

| f (6)    | 6kHz      |

| f (7)    | 15kHz     |

In order to minimize the noise which occurs during changeover, connections are made using 1  $M\Omega$  resistors from pins f(1) through f(7) to 1/2  $V_{CC}$ 1.

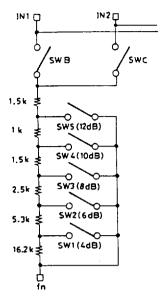

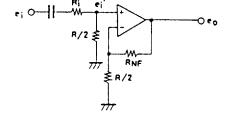

Resistor Equivalent Circuit (single band)

## **Principles of Operation**

The graphic equalizer section is constructed from 7 resonance circuits and output buffer amplifiers (every channel); variable resistors (LC7522) and resonance circuit capacitors C1 and C2 are built-in. Resonance circuits utilize semiconductor inductors and apply resonation to reduced impedance; all frequency gains are altered.

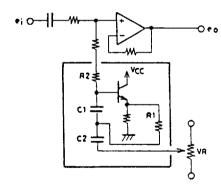

# (1) Resonance Circuit

Semiconductor inductors replace the L of the R, L, C series resonance circuit with a CR element passing through the buffer function of active elements such as the transistor and op-amp (operational amplifier) thereby effecting the equivalent operation of a R, L, C series resonance circuit. The STK301-020 resonance circuit buffer is constructed using transistors and arranged as illustrated in Figure 2.

Resonance frequency  $f_0$  is determined using the following formula:

$$f_0 = \frac{1}{2\pi \sqrt{C_1 \cdot C_2 \cdot R_1 \cdot R_2}}$$

Fig. 2 Resonance Circuit

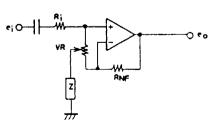

#### (2) Flat, Boost and Cut

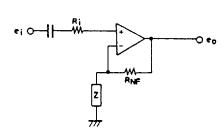

Gains matching resonance circuit frequency gains are altered by altering the built-in resonance circuits and electronic volume. Figure 3 is presented to describe the equivalent circuit. Z represents the impedance of the resonance circuit in Figure 2.

Z: Resonance circuit impedance VR: Equivalent to LC7522

Fig. 3 Equivalent Circuit

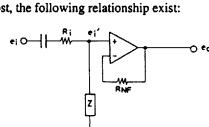

### (3) Flat

When the volume is set to the midrange position and  $Ri=R_{NF}$ , the following relationships are established:

$$ei' = \frac{R/2}{Ri = R/2} \cdot ei$$

$$A_V = \frac{R_{NF} + R/2}{R/2}$$

in which

with no relation to the resonance circuit and frequency characteristics become flat.

When VR is set to R, the resistance value using a VR sector position becomes R/2.

### (4) Boost

When the volume is set to the boost position, resonance circuit is linked to the NF loop of the output buffer amplifier. Under these circumstances and when R≥Ri and R<sub>NF</sub>, the following relationship exist:

$$A_V = \frac{R_{NF} + Z}{Z}$$

is established and output voltage eo is calculated as

$$eo = A_V \cdot ei = \frac{R_{NF} + Z}{Z} \cdot ei$$

The gain becomes a minimum when the resonance circuit has Z at a minimum so that the frequency option is boosted.

#### (5) Cut

When volume is set to the cut side, resonance circuit is linked to the input side of the output buffer amplifier. Under these circumstances and when ignoring R similarly to boost, the following relationship exist:

$$ei' = \frac{Z}{Ri+Z} \cdot ei, A_V = 1$$

is established and output voltageen is calculated as

$$eo = A_V \cdot ei' = \frac{Z}{Ri + Z} \cdot ei$$

The gain becomes a minimum when the resonance circuit has Z at a minimum so that the frequency option is cut.

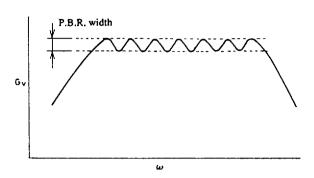

# (6) Resonance Circuit Crest Acuteness (Q)

Resonance circuit crest acuteness is determined by comparing frequency widths  $\varpi 2 - \varpi 1$  for  $G_V \max \sqrt{2}$ where G<sub>V</sub> max represents point w0 as the maximum value of the resonance circuit crest.

The following formula is used to calculate the value for Q:

$$Q = \sqrt{\frac{C1 \cdot R2}{C2 \cdot R1}}$$

As the value for Q becomes larger, the participating frequency bandwidth of the resonance circuit becomes narrower. Although neighboring bands distinction is precise, the swell of frequency characteristics under total boost is larger while the peak of the resultant frequency is lowered.

With the STK301-020, few crossover bands exist with an increase in swell during total boost. Pass-band-ripple (P.B.R.) width at this time is 4 dB with Q set at 3.5 fore and aft.

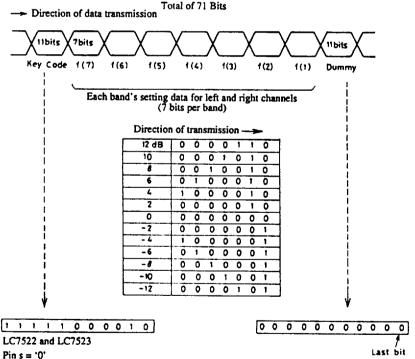

#### **Data Code**

- (1) Turning on the power initiates a process which transmits no data (0) for 60 clock cycles (initialization clock). When data is stopped in route, the remaining data is sent only after the clock has been initialized.

- (2) Using DI and CLK in conjunction with LC7560 (or equivalent) involves the transmission of the maximum initialization clock to those devices involved.

### Things to Note

- 1. A 1000pF rated capacitor (or higher) should be installed between the current pin and V<sub>SS</sub>.

- 2. When the control signal on the microcontroller side onsets faster than STK301-020's  $V_{DD}$ , a resistor rated at  $2k\Omega$  or more should be placed on the DI and CLK line.

- 3. Since the STK301-020 is equipped with a built-in CMOS LSI, sufficient caution should be extended to damage caused by static electricity.

- 4. Refer to the specification sheet for itemized details about the LC7522.

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.