August 1998

### 100328

## Low Power Octal ECL/TTL Bi-Directional Translator with Latch

### **General Description**

The 100328 is an octal latched bi-directional translator designed to convert TTL logic levels to 100K ECL logic levels and vice versa. The direction of this translation is determined by the DIR input. A LOW on the output enable input (OE) holds the ECL outputs in a cut-off state and the TTL outputs at a high impedance level. A HIGH on the latch enable input (LE) latches the data at both inputs even though only one output is enabled at the time. A LOW on LE makes the 100328 transparent.

The cut-off state is designed to be more negative than a normal ECL LOW level. This allows the output emitter-followers to turn off when the termination supply is -2.0V, presenting a high impedance to the data bus. This high impedance reduces termination power and prevents loss of low state noise margin when several loads share the bus.

The 100328 is designed with FAST® TTL output buffers, featuring optimal DC drive and capable of quickly charging and discharging highly capacitive loads. All inputs have 50 k $\Omega$ pull-down resistors.

#### **Features**

- Identical performance to the 100128 at 50% of the supply current

- Bi-directional translation

- 2000V ESD protection

- Latched outputs

- FAST TTL outputs

- TRI-STATE® outputs

- Voltage compensated operating range = -4.2V to -5.7V

- Available to MIL-STD-883

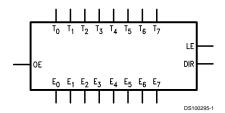

### **Logic Symbol**

| Pin Names                                                        | Description             |

|------------------------------------------------------------------|-------------------------|

| E <sub>0</sub> –E <sub>7</sub><br>T <sub>0</sub> –T <sub>7</sub> | ECL Data I/O            |

| T <sub>0</sub> -T <sub>7</sub>                                   | TTL Data I/O            |

| OE                                                               | Output Enable Input     |

| LE                                                               | Latch Enable Input      |

| DIR                                                              | Direction Control Input |

All pins function at 100K ECL levels except for T<sub>0</sub>-T<sub>7</sub>.

TRI-STATE® is a registered trademark of National Semiconductor Corporation. FAST® is a registered trademark of Fairchild Semiconductor.

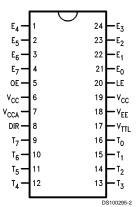

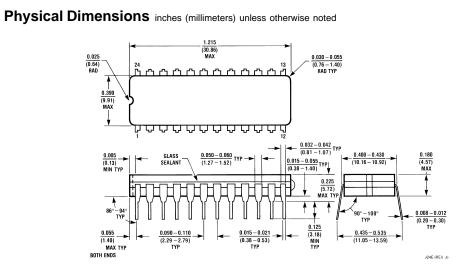

## **Connection Diagrams**

24-Pin DIP

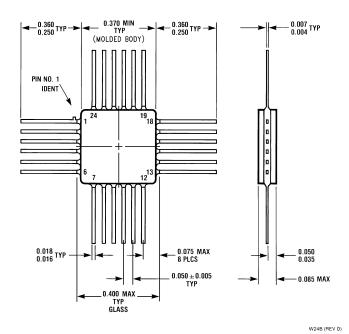

#### 24-Pin Quad Cerpak

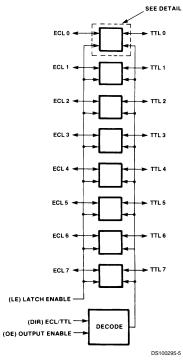

# **Functional Diagram**

Note: LE, DIR, and OE use ECL logic levels

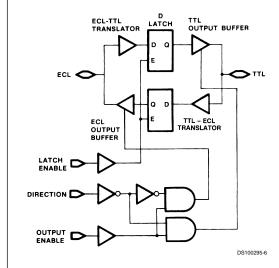

### Detail

## **Truth Table**

| OE | DIR | LE | ECL       | TTL     | Notes        |

|----|-----|----|-----------|---------|--------------|

|    |     |    | Port      | Port    |              |

| L  | Х   | L  | LOW       | Z       |              |

|    |     |    | (Cut-Off) |         |              |

| L  | L   | Н  | Input     | Z       | (Notes 1, 3) |

| L  | Н   | Н  | LOW       | Input   | (Notes 2, 3) |

|    |     |    | (Cut-Off) |         |              |

| Н  | L   | L  | L         | L       | (Notes 1, 4) |

| Н  | L   | L  | Н         | Н       | (Notes 1, 4) |

| Н  | L   | Н  | Х         | Latched | (Notes 1, 3) |

| Н  | Н   | L  | L         | L       | (Notes 2, 4) |

| Н  | Н   | L  | Н         | Н       | (Notes 2, 4) |

| Н  | Н   | Н  | Latched   | Х       | (Notes 2, 4) |

H = HIGH Voltage Level L = LOW Voltage Level X = Don't Care

Z = High Impedance

Note 1: ECL input to TTL output mode. Note 2: TTL input to ECL output mode.

Note 3: Retains data present before LE set HIGH.

Note 4: Latch is transparent.

#### **Absolute Maximum Ratings** (Note 5)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature ( $T_{STG}$ )  $-65^{\circ}C$  to +150 $^{\circ}C$

Maximum Junction Temperature (T<sub>J</sub>)

Ceramic +175°C

$V_{\text{EE}}$  Pin Potential to

Ground Pin -7.0V to +0.5V

$V_{\mathsf{TTL}}$  Pin Potential to

Ground Pin -0.5V to +6.0V

ECL Input Voltage (DC) V<sub>EE</sub> to +0.5V

ECL Output Current

(DC Output HIGH) -50 mA

TTL Input Voltage (Note 7) -0.5V to +6.0V

TTL Input Current (Note 7) —30 mA to +5.0 mA

Voltage Applied to Output in HIGH State

TRI-STATE Output -0.5V to +5.5V

Current Applied to TTL

ESD (Note 6) ≥2000V

# Recommended Operating Conditions

Case Temperature (T<sub>C</sub>)

Military -55°C to +125°C

ECL Supply Voltage (V<sub>EE</sub>) -5.7 V to -4.2 V TTL Supply Voltage (V<sub>TTL</sub>) +4.5 V to +5.5 V

**Note 5:** Absolute maximum ratings are those values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 6: ESD testing conforms to MIL-STD-883, Method 3015.

Note 7: Either voltage limit or current limit is sufficient to protect inputs.

# Military Version TTL-to-ECL DC Electrical Characteristics

$V_{EE}$  = -4.2V to -5.7V,  $V_{CC}$  =  $V_{CCA}$  = GND,  $T_{C}$  = -55°C to +125°C,  $V_{TTL}$  = +4.5V to +5.5V

| Symbol           | Parameter                      | Min   | Max   | Units | T <sub>C</sub> | Conditions                                               |               | Notes       |

|------------------|--------------------------------|-------|-------|-------|----------------|----------------------------------------------------------|---------------|-------------|

| V <sub>OH</sub>  | Output HIGH Voltage            | -1025 | -870  | mV    | 0°C to         |                                                          | Loading with  | (Notes 8, 9 |

|                  |                                |       |       |       | +125°C         |                                                          | 50Ω to -2.0V  | 10)         |

|                  |                                | -1085 | -870  | mV    | −55°C          | V <sub>IN</sub> = V <sub>IH</sub> (Max)                  |               |             |

| V <sub>OL</sub>  | Output LOW Voltage             | -1830 | -1620 | mV    | 0°C to         | or V <sub>IL</sub> (Min)                                 |               |             |

|                  |                                |       |       |       | +125°C         |                                                          |               |             |

|                  |                                | -1830 | -1555 | mV    | −55°C          |                                                          |               |             |

|                  | Cutoff Voltage                 |       | -1950 | mV    | 0°C to         |                                                          |               |             |

|                  |                                |       |       |       | +125°C         | OE or DIR Low                                            |               |             |

|                  |                                |       | -1850 | mV    | −55°C          |                                                          |               |             |

| V <sub>OHC</sub> | Output HIGH Voltage            | -1035 |       | mV    | 0°C to         |                                                          |               | (Notes 8, 9 |

|                  |                                |       |       |       | +125°C         |                                                          |               | 10)         |

|                  |                                | -1085 |       | mV    | −55°C          | V <sub>IN</sub> = V <sub>IH</sub> (Min)                  | Loading with  |             |

| V <sub>OLC</sub> | Output LOW Voltage             |       | -1610 | mV    | 0°C to         | or V <sub>IL</sub> (Max)                                 | 50Ω0 to -2.0V |             |

|                  |                                |       |       |       | +125°C         |                                                          |               |             |

|                  |                                |       | -1555 | mV    | −55°C          |                                                          |               |             |

| V <sub>IH</sub>  | Input HIGH Voltage             | 2.0   |       | V     | −55°C to       | Over V <sub>TTL</sub> , V <sub>EE</sub> , T <sub>0</sub> | Range         | (Notes 8, 9 |

|                  |                                |       |       |       | +125°C         |                                                          |               | 10, 11)     |

| V <sub>IL</sub>  | Input LOW Voltage              |       | 0.8   | V     | −55°C to       | Over V <sub>TTL</sub> , V <sub>EE</sub> , T <sub>0</sub> | Range         | (Notes 8, 9 |

|                  |                                |       |       |       | +125°C         |                                                          |               | 10, 11)     |

| I <sub>IH</sub>  | Input HIGH Current             |       | 70    | μA    | −55°C to       | V <sub>IN</sub> = +2.7V                                  |               | (Notes 8, 9 |

|                  |                                |       |       |       | 125°C          |                                                          |               | 10)         |

|                  | Breakdown Test                 |       | 1.0   | mA    | −55°C to       | V <sub>IN</sub> = +5.5V                                  |               |             |

|                  |                                |       |       |       | +125°C         |                                                          |               |             |

| I <sub>IL</sub>  | Input LOW Current              | -1.0  |       | mA    | −55°C to       | V <sub>IN</sub> = +0.5V                                  |               | (Notes 8, 9 |

|                  |                                |       |       |       | +125°C         |                                                          |               | 10)         |

| $V_{FCD}$        | Input Clamp                    | -1.2  |       | V     | −55°C to       | I <sub>IN</sub> = -18 mA                                 |               | (Notes 8, 9 |

|                  | Diode Voltage                  |       |       |       | +125° C        |                                                          |               | 10)         |

| I <sub>EE</sub>  | V <sub>EE</sub> Supply Current |       |       |       |                | LE Low, OE and D                                         | IR High       | (Notes 8, 9 |

|                  |                                |       |       |       | −55°C to       | Inputs Open                                              |               | 10)         |

|                  |                                | -165  | -73   | mA    | +125°C         | $V_{EE} = -4.2V \text{ to } -4$                          | .8V           |             |

|                  |                                | -175  | -73   |       |                | $V_{EE} = -4.2V \text{ to } -5$                          | .7V           |             |

# Military Version ECL-to-TTL DC Electrical Characteristics

$V_{EE} = -4.2V \text{ to } -5.7V, V_{CC} = V_{CCA} = \text{GND}, T_{C} = -55^{\circ}\text{C to } +125^{\circ}\text{C}, C_{L} = 50 \text{ pF}, V_{TTL} = +4.5V \text{ to } +5.5V$

| Symbol            | Parameter                       | Min   | Max   | Units | T <sub>C</sub> | Conditions                                | Notes                |

|-------------------|---------------------------------|-------|-------|-------|----------------|-------------------------------------------|----------------------|

| V <sub>OH</sub>   | Output HIGH Voltage             | 2.5   |       | mV    | 0°C to +125°C  | $I_{OH} = -1 \text{ mA}, V_{TTL} = 4.50V$ | (Notes 8, 9, 10)     |

|                   |                                 | 2.4   |       |       | −55°C          |                                           |                      |

| V <sub>OL</sub>   | Output LOW Voltage              |       | 0.5   | mV    | −55°C          | $I_{OL}$ = 24 mA, $V_{TTL}$ = 4.50V       |                      |

|                   |                                 |       |       |       | +125°C         |                                           |                      |

| V <sub>IH</sub>   | Input HIGH Voltage              | -1165 | -870  | mV    | −55°C          | Guaranteed HIGH Signal                    | (Notes 8, 9, 10, 11) |

|                   |                                 |       |       |       | +125°C         | for All Inputs                            |                      |

| V <sub>IL</sub>   | Input LOW Voltage               | -1830 | -1475 | mV    | −55°C to       | Guaranteed LOW Signal                     | (Notes 8, 9, 10, 11) |

|                   |                                 |       |       |       | +125°C         | for All Inputs                            |                      |

| I <sub>IH</sub>   | Input HIGH Current              |       | 350   | μA    | 0°C to         | V <sub>EE</sub> = -5.7V                   | (Notes 8, 9, 10)     |

|                   |                                 |       | 500   |       | +125°C         | $V_{IN} = V_{IH} (Max)$                   |                      |

| I <sub>IL</sub>   | Input LOW Current               | 0.50  |       | μA    | −55°C to       | V <sub>EE</sub> = -4.2V                   | (Notes 8, 9, 10)     |

|                   |                                 |       |       |       | +125°C         | $V_{IN} = V_{IL} (Min)$                   |                      |

| I <sub>OZHT</sub> | TRI-STATE Current               |       | 70    | μA    | −55°C to       | V <sub>OUT</sub> = +2.7V                  | (Notes 8, 9, 10)     |

|                   | Output High                     |       |       |       | +125°C         |                                           |                      |

| I <sub>OZLT</sub> | TRI-STATE Current               | -1.0  |       | mA    | −55°C to       | V <sub>OUT</sub> = +0.5V                  | (Notes 8, 9, 10)     |

|                   | Output Low                      |       |       |       | +125°C         |                                           |                      |

| Ios               | Output Short-Circuit            | -150  | -60   | mA    | −55°C to       | $V_{OUT} = 0.0V, V_{TTL} = +5.5V$         | (Notes 8, 9, 10)     |

|                   | CURRENT                         |       |       |       | +125°C         |                                           |                      |

| I <sub>TTL</sub>  | V <sub>TTL</sub> Supply Current |       | 75    | mA    | −55°C to       | TTL Outputs Low                           | (Notes 8, 9, 10)     |

|                   |                                 |       | 50    | mA    | +125°C         | TTL Output High                           |                      |

|                   |                                 |       | 70    | mA    |                | TTL Output in TRI-STATE                   |                      |

Note 8: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55°C), then testing immediately without allowing for the junction temperature to stabilize due to heat dissipation after power-up. This provides "cold start" specs which can be considered a worst case condition at cold temperatures.

Note 9: Screen tested 100% on each device at -55°C, +25°C, and +125°C, Subgroups, 1, 2 3, 7, and 8.

Note 10: Sample tested (Method 5005, Table I) on each manufactured lot at -55°C, +25°C, and +125°C, Subgroups A1, 2, 3, 7, and 8.

Note 11: Guaranteed by applying specified input condition and testing V<sub>OH</sub>/V<sub>OL</sub>.

#### Military Version TTL-to-ECL AC Electrical Characteristics

$V_{\rm EE}$  = -4.2V to -5.7V,  $V_{\rm TTL}$  = +4.5V to +5.5V,  $V_{\rm CC}$  =  $V_{\rm CCA}$  = GND

| Symbol              | Parameter                        |     | T <sub>C</sub> = -55°C |     | T <sub>C</sub> = 25°C |     | T <sub>C</sub> =<br>+125°C |    | Conditions   | Notes      |

|---------------------|----------------------------------|-----|------------------------|-----|-----------------------|-----|----------------------------|----|--------------|------------|

|                     |                                  | Min | Max                    | Min | Max                   | Min | Max                        |    |              |            |

| t <sub>PLH</sub>    | T <sub>N</sub> to E <sub>n</sub> | 0.8 | 3.4                    | 1.1 | 3.6                   | 0.8 | 3.7                        | ns | Figures 1, 2 | (Notes 12, |

| $t_{PHL}$           | (Transparent)                    |     |                        |     |                       |     |                            | ns |              | 13, 14)    |

| t <sub>PLH</sub>    | LE to E <sub>n</sub>             | 1.2 | 3.8                    | 1.4 | 3.7                   | 1.1 | 3.8                        | ns | Figures 1, 2 |            |

| $t_{PHL}$           |                                  |     |                        |     |                       |     |                            | ns |              |            |

| t <sub>PZH</sub>    | OE to E <sub>n</sub>             | 0.8 | 3.6                    | 1.5 | 4.0                   | 2.0 | 5.2                        | ns | Figures 1, 2 | (Notes 12, |

|                     | (Cutoff to HIGH)                 |     |                        |     |                       |     |                            |    |              | 13, 14)    |

| t <sub>PHZ</sub>    | OE to E <sub>n</sub>             | 1.5 | 4.6                    | 1.6 | 4.2                   | 1.6 | 4.3                        | ns | Figures 1, 2 |            |

|                     | (HIGH to Cutoff)                 |     |                        |     |                       |     |                            |    |              |            |

| t <sub>PHZ</sub>    | DIR to E <sub>n</sub>            | 1.6 | 4.7                    | 1.6 | 4.3                   | 1.7 | 4.3                        | ns | Figures 1, 2 |            |

|                     | (HIGH to Cutoff)                 |     |                        |     |                       |     |                            |    |              |            |

| t <sub>set</sub>    | T <sub>n</sub> to LE             | 2.5 |                        | 2.0 |                       | 2.5 |                            | ns | Figures 1, 2 | (Note 15)  |

| t <sub>hold</sub>   | T <sub>n</sub> to LE             | 2.5 |                        | 2.0 |                       | 2.5 |                            | ns | Figures 1, 2 |            |

| t <sub>pw</sub> (H) | Pulse Width LE                   | 2.5 |                        | 2.0 |                       | 2.5 |                            | ns | Figures 1, 2 | (Note 15)  |

| t <sub>TLH</sub>    | Transition Time                  | 0.4 | 2.3                    | 0.5 | 2.1                   | 0.4 | 2.4                        | ns | Figures 1, 2 | (Note 15)  |

| t <sub>THL</sub>    | 20% to 80%, 80% to 20%           |     |                        |     |                       |     |                            |    |              |            |

# Military Version ECL-to-TTL AC Electrical Characteristics

$\rm V_{EE}$  = -4.2V to -5.7V,  $\rm V_{TTL}$  = +4.5V to +5.5V,  $\rm V_{CC}$  =  $\rm V_{CCA}$  = GND,  $\rm C_L$  = 50 pF

| Symbol              | Parameter                        | T <sub>C</sub> = | -55°C | T <sub>c</sub> = | 25°C | T <sub>C</sub> = | T <sub>C</sub> = +125°C |    | Conditions   | Notes          |

|---------------------|----------------------------------|------------------|-------|------------------|------|------------------|-------------------------|----|--------------|----------------|

|                     |                                  | Min              | Max   | Min              | Max  | Min              | Max                     | 1  |              |                |

| t <sub>PLH</sub>    | E <sub>n</sub> to T <sub>n</sub> | 2.1              | 6.0   | 2.0              | 5.6  | 2.2              | 6.3                     | ns | Figures 1, 2 | (Notes 12, 13, |

| t <sub>PHL</sub>    | (Transparent)                    |                  |       |                  |      |                  |                         |    |              | 14)            |

| t <sub>PLH</sub>    | LE to T <sub>n</sub>             | 3.1              | 7.0   | 3.1              | 6.5  | 3.3              | 7.5                     | ns | Figures 3, 4 |                |

| t <sub>PHL</sub>    |                                  |                  |       |                  |      |                  |                         |    |              |                |

| t <sub>PZH</sub>    | OE to T <sub>n</sub>             | 3.2              | 8.0   | 3.7              | 8.0  | 4.0              | 9.2                     | ns | Figures 3, 4 | (Notes 12, 13, |

| t <sub>PZL</sub>    | (Enable Time)                    | 3.6              | 8.0   | 4.0              | 8.5  | 4.3              | 9.6                     |    |              | 14)            |

| t <sub>PHZ</sub>    | OE to T <sub>n</sub>             | 3.2              | 8.5   | 3.3              | 8.0  | 3.5              | 8.4                     | ns | Figures 3, 5 |                |

| t <sub>PLZ</sub>    | (Disable Time)                   | 3.0              | 8.0   | 3.4              | 7.5  | 4.1              | 10.0                    |    |              |                |

| t <sub>PHZ</sub>    | DIR to T <sub>n</sub>            | 2.6              | 7.0   | 2.6              | 7.0  | 2.9              | 8.0                     | ns | Figures 3, 6 |                |

| t <sub>PLZ</sub>    | (Disable Time)                   | 2.7              | 7.0   | 3.1              | 7.0  | 4.0              | 10.0                    |    |              |                |

| t <sub>set</sub>    | E <sub>n</sub> to LE             | 2.5              |       | 2.0              |      | 2.5              |                         | ns | Figures 3, 4 | (Note 15)      |

| t <sub>hold</sub>   | E <sub>n</sub> to LE             | 3.0              |       | 2.5              |      | 3.0              |                         | ns | Figures 3, 4 |                |

| t <sub>pw</sub> (H) | Pulse Width LE                   | 2.5              |       | 2.0              |      | 5.0              |                         | ns | Figures 3, 4 | (Note 15)      |

Note 12: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55°C), then testing immediately after power-up. This provides "cold start" specs which can be considered a worst case condition at cold temperatures.

Note 13: Screen tested 100% on each device at +25°C, temperature only, Subgroup A9.

Note 14: Sample tested (Method 5005, Table I) on each mfg. lot at +25°C, Subgroup A9, and at +125°C and -55°C temperatures, Subgroups A10 and A11.

Note 15: Not tested at +25°C, +125°C and -55°C temperature (design characterization data).

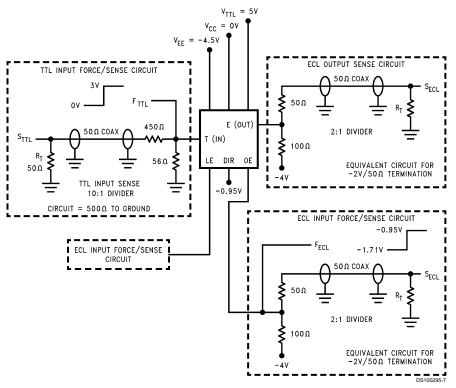

## **Test Circuitry (TTL-to-ECL)**

Note 16:  $R_t = 50\Omega$  termination. When an input or output is being monitored by a scope,  $R_t$  is supplied by the scope's  $50\Omega$  resistance. When an input or output is not being monitored, an external  $50\Omega$  resistance must be applied to serve as  $R_t$ .

Note 17: TTL and ECL force signals are brought to the DUT via  $50\Omega$  coax lines.

Note 18:  $V_{TTL}$  is decoupled to ground with 0.1  $\mu$ F to ground,  $V_{EE}$  is decoupled to ground with 0.01  $\mu$ F and  $V_{CC}$  is connected to ground.

Note 19: For ECL input pins, the equivelent force/sense circuitry is optional.

#### FIGURE 1. TTL-to-ECL AC Test Circuit

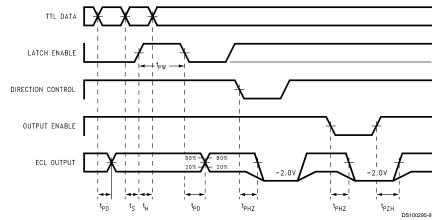

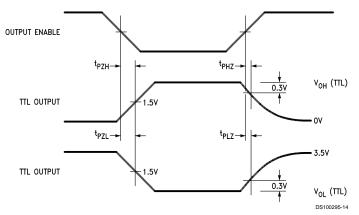

### **Switching Waveforms (TTL-to-ECL)**

FIGURE 2. TTL to ECL Transition — Propagation Delay and Transition Times

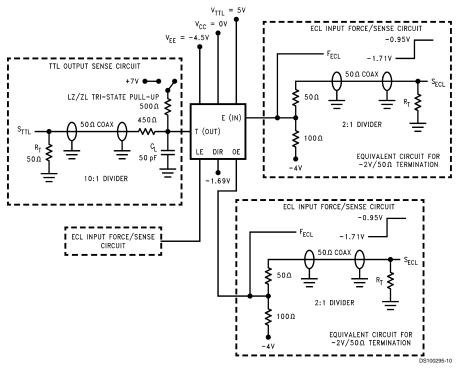

## **Test Circuitry (ECL-to-TTL)**

Note 20:  $R_t = 50\Omega$  termination. When an input or output is being monitored by a scope,  $R_t$  is supplied by the scope's  $50\Omega$  resistance. When an input or output is not being monitored, an external  $50\Omega$  resistance must be applied to serve as  $R_t$ .

Note 21: The TTL TRI-STATE pull up switch is connected to +7V only for ZL and LZ tests.

Note 22: TTL and ECL force signals are brought to the DUT via  $50\Omega$  coax lines.

Note 23:  $V_{TTL}$  is decoupled to ground with 0.1  $\mu$ F,  $V_{EE}$  is decoupled to ground with 0.01  $\mu$ F and  $V_{CC}$  is connected to ground.

#### FIGURE 3. ECL-to-TTL AC Test Circuit

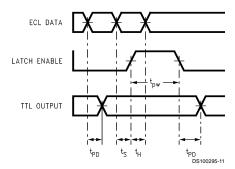

### Switching Waveforms (ECL-to-TTL)

Note 24: DIR is LOW, and OE is HIGH

FIGURE 4. ECL-to-TTL Transition — Propagation Delay and Transition Times

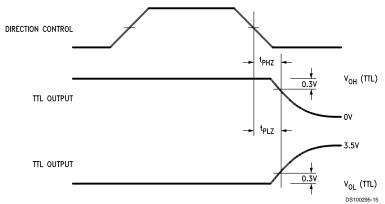

# Switching Waveforms (ECL-to-TTL) (Continued)

Note 25: DIR is LOW, LE is HIGH

FIGURE 5. ECL-to-TTL Transition, OE to TTL Output, Enable and Disable Times

Note 26: OE is HIGH, LE is HIGH

FIGURE 6. ECL-to-TTL Transition, DIR to TTL Output, Disable Time

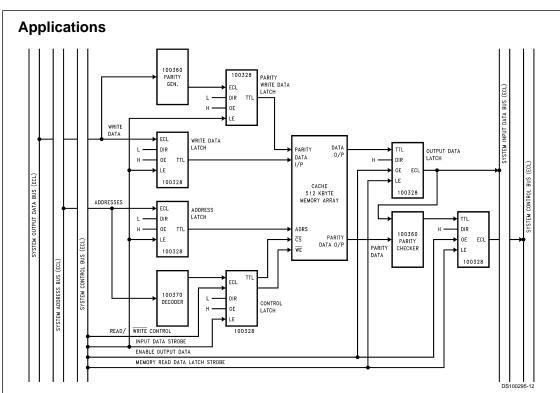

FIGURE 7. Applications Diagram — MOS/TTL SRAM Interface Using 100328 ECL-TTL Latched Translator

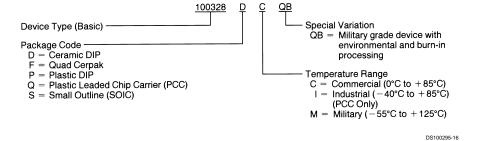

## **Ordering Information**

The device number is used to form part of a simplified purchasing code where A package type and temperature range are defined as follows:

24-Lead Ceramic Dual-In-Line Package (0.400" Wide) (D)

NS Package Number J24E

24-Lead Quad Cerpak (F) NS Package Number W24B

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation Americas Tel: 1-800-272-9959

Americas

Tel: 1-800-272-9959

Fax: 1-800-737-7018

Email: support@nsc.com

www.national.com

National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tei: +49 (0) 1 80-530 85 85

English Tei: +49 (0) 1 80-532 78 32

Français Tei: +49 (0) 1 80-532 35

Italiano Tei: +49 (0) 1 80-534 16 80

Tel: 65-2544466 Fax: 65-2504466 Email: sea.support@nsc.com

National Semiconductor

Asia Pacific Customer

Response Group

National Semiconductor Japan Ltd. Tel: 81-3-5620-6175 Fax: 81-3-5620-6179

# 100328 Low Power ECL/TTL Bi-Directional Translator with Latch

## **Contents**

- General Description

- Features

- Datasheet

- Package Availability, Models, Samples & Pricing

- Application Notes

# **General Description**

The 100328 is an octal latched bi-directional translator designed to convert TTL logic levels to 100K ECL logic levels and vice versa. The direction of this translation is determined by the DIR input. A LOW on the output enable input (OE) holds the ECL outputs in a cut-off state and the TTL outputs at a high impedance level. A HIGH on the latch enable input (LE) latches the data at both inputs even though only one output is enabled at the time. A LOW on LE makes the 100328 transparent.

The cut-off state is designed to be more negative than a normal ECL LOW level. This allows the output emitter-followers to turn off when the termination supply is -2.0V, presenting a high impedance to the data bus. This high impedance reduces termination power and prevents loss of low state noise margin when several loads share the bus.

The 100328 is designed with FAST TTL output buffers, featuring optimal DC drive and capable of quickly charging and discharging highly capacitive loads. All inputs have 50 k Ohm pull-down resistors.

## **Features**

- Identical performance to the 100128 at 50% of the supply current

- Bi-directional translation

- 2000V ESD protection

- Latched outputs

- FAST TTL outputs

- TRI-STATE outputs

- Voltage compensated operating range = -4.2V to -5.7V

- Available to MIL-STD-883

# **Datasheet**

| Title                                | Size<br>(in<br>Kbytes) | Date         | View<br>Online | Download | Receive via<br>Email |

|--------------------------------------|------------------------|--------------|----------------|----------|----------------------|

| II .                                 |                        | 2-Sep-<br>98 | View<br>Online | Download | Receive via<br>Email |

| 100328 Mil-Aero Datasheet MN100328-X | 62 Kbytes              |              | View<br>Online | Download | Receive via<br>Email |

Please use <u>Adobe Acrobat</u> to view PDF file(s). If you have trouble printing, see <u>Printing Problems</u>.

# Package Availability, Models, Samples & Pricing

|             | Packa   | ge        |                 | Mod   | els  | Samples             | Budgetar | y Pricing    | Std               |      |

|-------------|---------|-----------|-----------------|-------|------|---------------------|----------|--------------|-------------------|------|

| Part Number | Туре    | #<br>pins | Status          | SPICE | IBIS | & Electronic Orders | Quantity | \$US<br>each | Pack<br>Size      |      |

| 100328DMQB  | Cerdip  | 24        | Full production | N/A   | N/A  | X                   | 50+      | \$34.6000    | tube<br>of<br>15  | [lo  |

| 100328FMQB  | Cerquad | 24        | Full production | N/A   | N/A  | X                   | 50+      | \$39.0000    | tube<br>of<br>14  | [log |

| 100328FC    | Cerquad | 24        | Full production | N/A   | N/A  |                     |          |              | tube<br>of<br>N/A | [](  |

| 100328 MW8  | wafe    | r         | Full production | N/A   | N/A  |                     |          |              | N/A               |      |

# **Application Notes**

| Title | Size<br>(in<br>Kbytes) | Date         | View<br>Online | Download | Receive via<br>Email |

|-------|------------------------|--------------|----------------|----------|----------------------|

|       |                        | 6-Apr-<br>99 | View<br>Online | Download | Receive via<br>Email |

Please use <u>Adobe Acrobat</u> to view PDF file(s). If you have trouble printing, see <u>Printing Problems</u>.

[Information as of 28-Jul-2000]

| Quick Search | Parametric | System   | Product |             |

|--------------|------------|----------|---------|-------------|

|              | Search     | Diagrams | Tree    | <u>Home</u> |

About Languages . About the Site . About "Cookies"

National is QS 9000 Certified . Privacy/Security

Copyright © National Semiconductor Corporation

Preferences . Feedback