# Low Start-up Current PFC/PWM Controller Combo

#### **GENERAL DESCRIPTION**

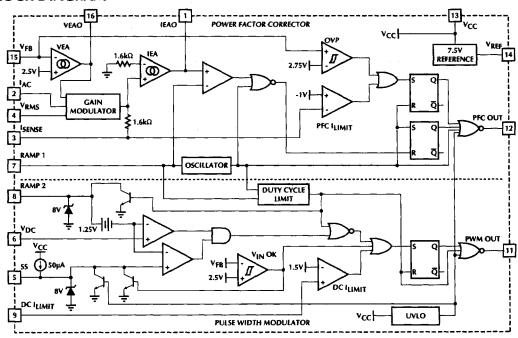

The ML4800 is a controller for power factor corrected, switched mode power supplies. Key features of this combined PFC and PWM controller are low start-up and operating currents. Power Factor Correction (PFC) allows the use of smaller, lower cost bulk capacitors, reduces power line loading and stress on the switching FETs, and results in a power supply that fully complies with IEC1000-3-2 specifications. The ML4800 includes circuits for the implementation of a leading edge, average current, "boost" type power factor correction and a trailing edge, pulse width modulator (PWM).

The PWM section of the ML800 operates at the same frequency as the PFC section. An over-voltage comparator shuts down the PFC section in the event of a sudden decrease in load. The PFC section also includes peak current limiting and input voltage brown-out protection. The ML4800 can be operated in current or voltage mode at up to 250kHz and includes a duty cycle limit to prevent transformer saturation.

#### **FEATURES**

- Internally synchronized PFC and PWM in one IC

- Low start-up current (300µA typ.)

- Low operating current (4mA typ.)

- Low total harmonic distortion

- Reduces ripple current in the storage capacitor between the PFC and PWM sections

- Average current, continuous boost leading edge PFC

- High efficiency trailing edge PWM can be configured for current mode or voltage mode operation

- Current fed gain modulator for improved noise immunity

- Brown-out control, overvoltage protection, UVLO, and soft start

#### **BLOCK DIAGRAM**

## **PIN CONFIGURATION**

ML4800 16-Pin PDIP (P16) 16-Pin Wide SOIC (S16W)

### PIN DESCRIPTION

| PIN | NAME             | FUNCTION                                                                                                                                               | PIN  | NAME                  | FUNCTION                                                   |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|------------------------------------------------------------|

| 1   | IEAO             | PFC transconductance current error amplifier output                                                                                                    | 9    | DC I <sub>LIMIT</sub> | PWM current limit comparator input                         |

| _   |                  | ·                                                                                                                                                      | 10   | GND                   | Ground                                                     |

| 2   | AC               | PFC gain control reference input                                                                                                                       | - 11 | PWM OUT               | PWM-driver-output                                          |

| 3   | ISENSE           | Current sense input to the PFC current                                                                                                                 |      |                       |                                                            |

|     |                  | limit comparator                                                                                                                                       | 12   | PFC OUT               | PFC driver output                                          |

| 4   | V <sub>RMS</sub> | Input for PFC RMS line voltage compensation                                                                                                            | 13   | V <sub>CC</sub>       | Positive supply (connected to an internal shunt regulator) |

| 5   | SS               | Connection point for the PWM soft start capacitor                                                                                                      | 14   | VREF                  | Buffered output for the internal 7.5V reference            |

| 6   | $V_{DC}$         | PWM voltage feedback input                                                                                                                             | 15   | V <sub>FB</sub>       | PFC transconductance voltage error amplifier input         |

| 7   | RAMP 1           | Oscillator timing node; timing set by $R_TC_T$                                                                                                         | 16   | VEAO                  | PFC transconductance voltage error amplifier output        |

| 8   | RAMP 2           | When in current mode, this pin functions as as the current sense input; when in voltage mode, it is the PWM input from PFC output (feed forward ramp). |      |                       | ampiner output                                             |