# 900 MHz Analog Cordless Phone Baseband with Compander

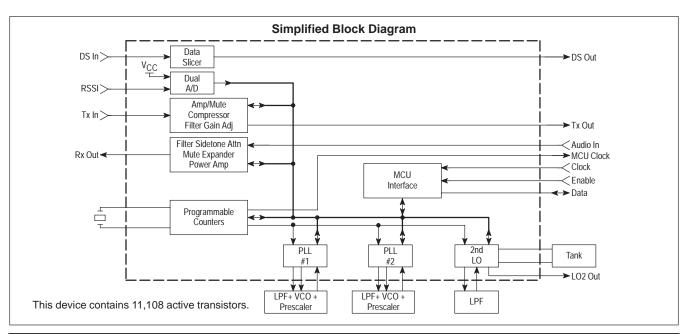

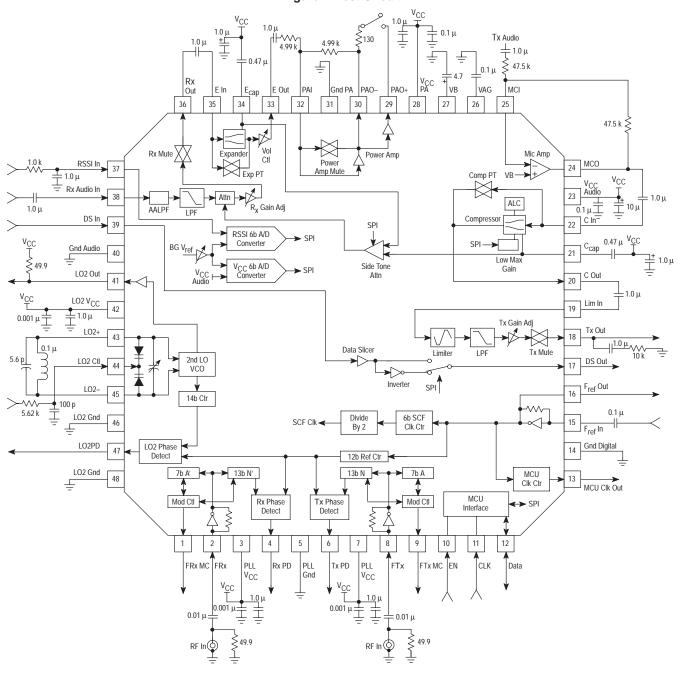

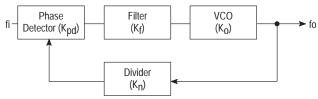

The MC33411 900 MHz Analog Cordless Phone Baseband system is designed to fit the requirements of a 900 MHz analog cordless telephone system. Included are three PLLs (Phase–Locked Loops). Two are intended for use with external VCOs and 64/65 or 128/129 dual modulus prescalers, and can control the transmit and receive (LO1) frequencies for 900 MHz communication. The third PLL is configured as the 2nd local oscillator (LO2), and is functional to 80 MHz. Also included are muting, audio gain adjust (internal and external), low battery/carrier detect, and a wide range for the PLL reference frequency. The power supply range is 2.7 to 5.5 V. "A" version devices have programmable MCU clock out and reference oscillator disable functions, whereas these functions are always enabled for "B" version devices.

- Complete Expander/Compressor for Superior Noise Rejection

- Two PLLs and a LO Suitable for a 900 MHz System

- Minimal External Components

- Transmit Path Includes Adjustable Gain Amplifier, Filters, Mute, Compressor with Bypass and Limiter

- Receive Path Contains Data Slicer, Adjustable Gain Amplifier, Sidetone Attenuator, Filters, Expander with Bypass, Mute, Volume Control and Power Amplifier

- Dual A/Ds are Provided to Monitor RSSI and V<sub>CC</sub>

- Independent Power Amplifier with Differential Outputs and Mute

- Selectable Frequency for Switched Capacitor Filters, PLLs and the LO

- Reference Frequency Source can be a Crystal or System Clock

- Serial μP Port to Control Gain, Mute, Frequency Selection, Phase Detector Gain, Power Down Modes, Low Battery Detect and Others

- Power Supply Range: 2.7 to 5.5 V

- Power Down Modes for Power Conservation

# MC33411A/B

# 900 MHz ANALOG CORDLESS PHONE BASEBAND WITH COMPANDER

SEMICONDUCTOR TECHNICAL DATA

FTA SUFFIX

PLASTIC PACKAGE

CASE 932

(LQFP-48)

#### **ORDERING INFORMATION**

| Device      | Operating<br>Temperature     | Package |

|-------------|------------------------------|---------|

| MC33411AFTA | T <sub>Δ</sub> = -20 to 70°C | LQFP-48 |

| MC33411BFTA | 1A = -20 to 70 C             | LQFF-40 |

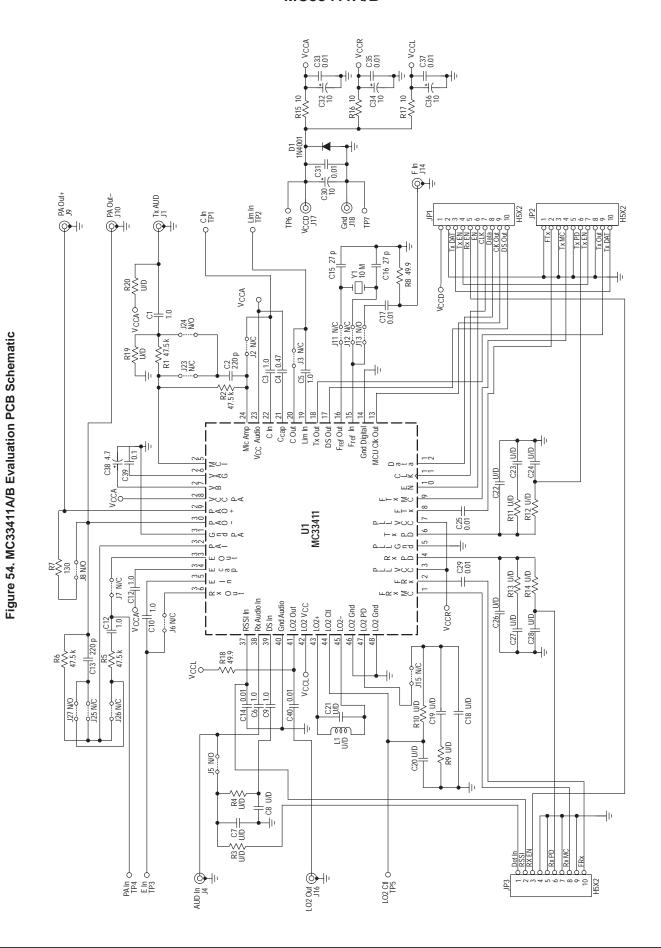

Figure 1. Test Circuit

#### **MAXIMUM RATINGS**

| Rating                    | Symbol | Value       | Unit |

|---------------------------|--------|-------------|------|

| Power Supply Voltage      | Vcc    | -0.5 to 6.0 | V    |

| Junction Temperature      | TJ     | -6.5 to 150 | °C   |

| Maximum Power Dissipation | PD     | 150         | mW   |

NOTES: 1. Maximum Ratings are those values beyond which damage to the device may occur.

Functional operation should be restricted to the limits in the Recommended Operating

Conditions, Electrical Characteristics tables or Pin Descriptions section.

# RECOMMENDED OPERATING CONDITIONS

| Characteristic                         | Symbol             | Min                             | Тур | Max   | Unit |

|----------------------------------------|--------------------|---------------------------------|-----|-------|------|

| Supply Voltage                         | Vcc                | 2.7                             | 3.6 | 5.5   | Vdc  |

| Operating Ambient Temperature          | TA                 | -20                             | _   | 70    | °C   |

| Input Voltage Low (Data, CLK, EN)      | Vil                | _                               | _   | 0.3   | V    |

| Input Voltage High (Data, CLK, EN)     | Vih                | Tx PLL<br>V <sub>CC</sub> – 0.3 | -   | _     | V    |

| Frequency Range (F <sub>ref in</sub> ) | F <sub>range</sub> | 4.0                             | _   | 18.25 | MHz  |

| Bandgap Reference Voltage              | VB                 | -                               | 1.5 | -     | V    |

# **DC ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.6 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.)

| Characteristic                                                | Symbol               | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------|----------------------|------|-----|------|------|

| Static Current                                                |                      |      |     |      |      |

| Active Mode (R5/8 to $0 = 0$ ; R6/7 = 0)                      | ACT ICC              | _    | 15  | 20   | mA   |

| Receive Mode (R5/8, 7, 3, 2, 0 = 0; R6/7 = 0; R5/6,5,4,1 = 1) | Rx I <sub>CC</sub>   | _    | 10  | 13   | mA   |

| Standby Mode (R5/0 = 0; R6/7 = 0; R5/8 to 1 = 1)              | STD ICC              | _    | 500 | 1500 | μΑ   |

| Inactive Mode, A only (R5/8 to 0 =1; R6/7 = 1)                | INA ICC              | _    | 10  | 15   | μΑ   |

| Data Slicer Only                                              | DS ICC               | _    | 100 | -    | μΑ   |

| RSSI/Batt A/D Only                                            | AD ICC               | _    | 70  | -    | μΑ   |

| Tx Audio Only                                                 | TxA ICC              | _    | 1.4 | _    | mA   |

| Rx Audio Only                                                 | RxA I <sub>CC</sub>  | _    | 1.4 | _    | mA   |

| PA Only                                                       | PA ICC               | _    | 1.0 | -    | mA   |

| 2nd LO/F <sub>ref</sub> Only                                  | 2LO ICC              | _    | 6.0 | _    | mA   |

| Rx PLL/F <sub>ref</sub> Only                                  | RxPLL ICC            | _    | 1.0 | _    | mA   |

| Tx PLL/F <sub>ref</sub> Only                                  | TxPLL ICC            | _    | 1.0 | _    | mA   |

| Ref Osc Only, "A" version only                                | ROSC I <sub>CC</sub> | _    | 500 | _    | μΑ   |

| Reference Voltage, Unadjusted                                 | V <sub>B</sub>       | 1.38 | 1.5 | 1.62 | V    |

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 3.6 \text{ V}$ , $V_{B} = 1.5 \text{ V}$ , $T_{A} = 25^{\circ}\text{C}$ , Active Mode, Rx Gain = 01111, Vol Adi = 0111, fig. = 1.0 kHz, unless otherwise noted.)

| Vol Adj = 0111, $f_{in}$ = 1.0 kHz, unless otherwise noted.)                                                                  |              |                |                   |            |            |            |      |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|-------------------|------------|------------|------------|------|

| Characteristics                                                                                                               | Input<br>Pin | Measure<br>Pin | Symbol            | Min        | Тур        | Max        | Unit |

| Rx AUDIO PATH                                                                                                                 |              |                | •                 |            |            |            |      |

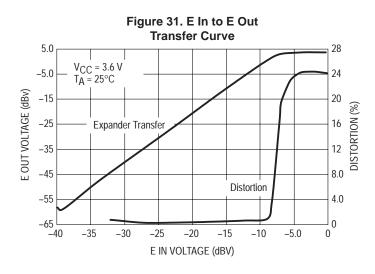

| Absolute Gain (V <sub>in</sub> = -20 dBV)                                                                                     | Rx Audio In  | E Out          | G                 | -4.0       | 0          | 4.0        | dB   |

| Gain Tracking (Referenced to $E_{out}$ for $V_{in} = -20 \text{ dBV}$ ) $V_{in} = -30 \text{ dBV}$ $V_{in} = -40 \text{ dBV}$ | E In         | E Out          | Gt                | -21<br>-42 | -20<br>-40 | –19<br>–38 | dB   |

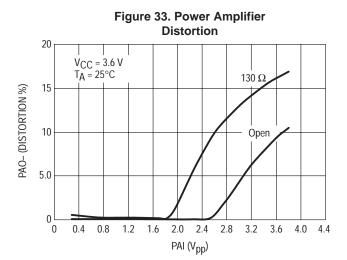

| Total Harmonic Distortion (V <sub>in</sub> = -20 dBV)                                                                         | Rx Audio In  | PAO-           | THD               | _          | 0.7        | 1.0        | %    |

| Maximum Input Voltage (V <sub>CC</sub> = 2.7 V)                                                                               | Rx Audio In  |                |                   | _          | -11.5      | -          | dBV  |

| Maximum Output Voltage (Increase input voltage until output voltage THD = 5%, then measure output voltage)                    | E In         | E Out          | V <sub>Omax</sub> | -2.0       | 0          | -          | dBV  |

NOTES: 1. Values specified are pure numbers to the base 10.

<sup>2.</sup> Meets Human Body Model (HBM) ≤2000 V and Machine Model (MM) ≤200 V. ESD data available upon request.

<sup>2.</sup> Typical performance parameters indicate the potential of the device under ideal operating conditions.

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (\text{V}_{CC} = 3.6 \ \text{V}, \ \text{V}_{B} = 1.5 \ \text{V}, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{Active Mode, Rx Gain} = 01111, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{C}_{A} = 25$ Vol Adj = 0111,  $f_{in}$  = 1.0 kHz, unless otherwise noted.)

| Characteristics                                                                                          | Input<br>Pin   | Measure<br>Pin              | Symbol               | Min              | Тур                      | Max         | Unit            |

|----------------------------------------------------------------------------------------------------------|----------------|-----------------------------|----------------------|------------------|--------------------------|-------------|-----------------|

| Rx AUDIO PATH (continued)                                                                                | •              | •                           |                      |                  |                          |             |                 |

| Input Impedance                                                                                          |                | RxAudio In<br>E In          | Z <sub>in</sub>      | _<br>_           | 600<br>7.5               | -<br>-      | kΩ              |

| Attack Time E <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k                                          | E In           | E Out                       | ta                   | _                | 3.0                      | _           | mS              |

| Release Time $E_{\text{cap}} = 0.5  \mu\text{F},  R_{\text{filt}} = 40  \text{k}$                        | E In           | E Out                       | t <sub>r</sub>       | _                | 13.5                     | _           | mS              |

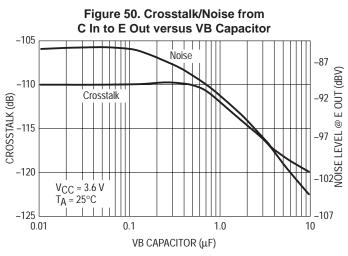

| Compressor to Expander Crosstalk ( $V_{in} = -10 \text{ dBV}$ , $V_{E \mid In} = AC \text{ Gnd}$ )       | MCI            | E Out                       | CT                   | _                | -90                      | -60         | dB              |

| Rx Muting (V <sub>in</sub> = -20 dBV, Rx Gain Adj = 01111)                                               | Rx Audio In    | E Out                       | Me                   | _                | -84                      | -60         | dB              |

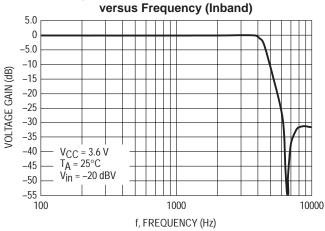

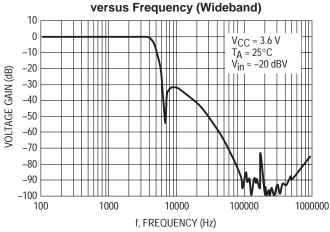

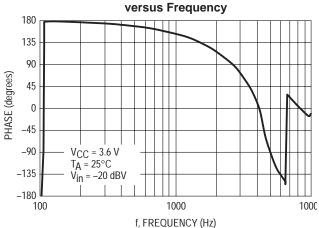

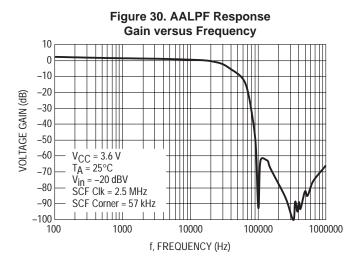

| Rx High Frequency Corner (V <sub>in</sub> = -20 dBV) SCF<br>Counter = 31 <sub>d</sub>                    | Rx Audio In    | Rx Out                      | Rx f <sub>ch</sub>   | 3.6              | 3.8                      | 4.0         | kHz             |

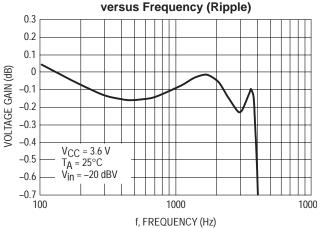

| Low Pass Filter Passband Ripple (V <sub>in</sub> = -20 dBV)                                              | Rx Audio In    | Rx Out                      | Ripple               | _                | 0.4                      | 0.6         | dB              |

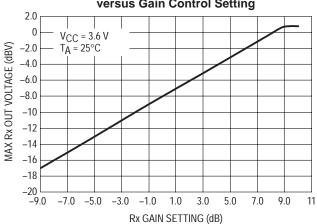

| Rx Gain Adjust Range                                                                                     | Rx Audio In    | Rx Out                      | Rx Range             | _                | -9.0 to 10               | -           | dB              |

| Rx Gain Adjust Steps                                                                                     | Rx Audio In    | Rx Out                      | Rx n                 | _                | 20                       | -           |                 |

| Audio Path Noise, C–Message Weighting (V <sub>in</sub> = AC Gnd)                                         | Rx Audio In    |                             | EN                   |                  |                          |             | dBV             |

|                                                                                                          |                | Rx Out                      |                      | _                | -85                      | _           |                 |

|                                                                                                          |                | E Out<br>PA Out             |                      | _                | <-95<br><-95             | _<br>_      |                 |

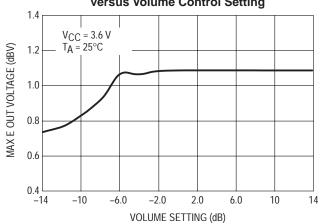

| Volume Control Adjust Range                                                                              | Rx Audio In    | E Out                       | <sup>V</sup> CtRange | _                | -14 to 16                | _           | dB              |

| Volume Control Levels                                                                                    | E In           | E Out                       | V <sub>cn</sub>      | _                | 16                       | _           |                 |

| Side Tone Attenuate Selections                                                                           | Rx Audio In    | Rx Out                      | STAn                 | _                | 4                        | _           |                 |

| Side Tone Attenuate (Referenced to E In)  Selection = 00  Selection = 01  Selection = 10  Selection = 11 |                | E Out                       | STA                  | -<br>-<br>-<br>- | 0.0<br>1.5<br>3.0<br>5.2 | -<br>-<br>- | dB              |

| Side Tone Attenuate Threshold (C Out/E In)                                                               |                |                             | STA <sub>thr</sub>   | _                | -3.0                     | _           | dB              |

| POWER AMP/MUTE ( $V_{CC} = 3.6 \text{ V}, V_B = 1.5 \text{ V}, T_A = 1.5 \text{ V}$                      | 25°C, Active N | lode, f <sub>in</sub> = 1.0 | kHz)                 |                  |                          |             |                 |

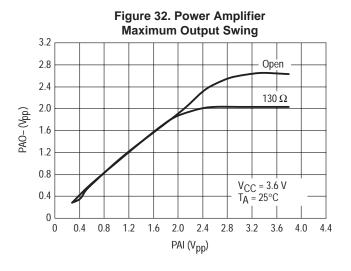

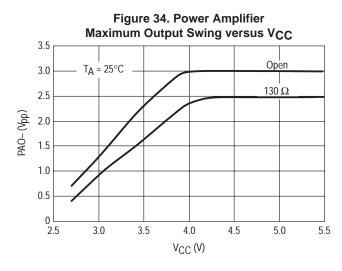

| Output Swing, ±5.0 mA load<br>(V <sub>PAO+</sub> @ -5.0 mA - V <sub>PAO+</sub> @ 5.0 mA)                 | PAI            | PAO+                        | V <sub>Omax</sub>    | 1.3              | 2.4                      | -           | V <sub>pp</sub> |

| Output Swing, ±5.0 mA load<br>(VPAO- @ -5.0 mA - VPAO-@ 5.0 mA)                                          | PAI            | PAO-                        | VOmax                | 1.3              | 2.4                      | ı           | V <sub>pp</sub> |

| Output Swing, No Load                                                                                    | PAI            | PAO+                        | V <sub>Omax</sub>    | -                | 2.7                      | 1           | V <sub>pp</sub> |

| Output Swing, No Load                                                                                    | PAI            | PAO-                        | V <sub>Omax</sub>    | -                | 2.7                      | 1           | V <sub>pp</sub> |

| Maximum Output Current                                                                                   |                | PAO-,<br>PAO+               | I <sub>Omax</sub>    | -                | ±5.0                     | -           | mA              |

| Power Amp Mute ( $V_{in} = -20 \text{ dBV}$ , RL = 130 $\Omega$ )                                        | PAI            | PAO-                        | M <sub>sp</sub>      | -                | -92                      | -60         | dB              |

| MIC AMP ( $V_{CC} = 3.6 \text{ V}, T_A = 25^{\circ}\text{C}, \text{ Active Mode, } f_{in}$               | = 1.0 kHz)     |                             |                      |                  |                          |             |                 |

| Open Loop Gain                                                                                           | MCI            | MCO                         | AVOL                 | _                | 100.000                  | _           | V/V             |

| Gain Bandwidth                                                                                           | MCI            | MCO                         | GBW                  | _                | 100                      | _           | kHz             |

| Maximum Output Swing (RL = 10 $k\Omega$ )                                                                | MCI            | MCO                         | V <sub>Omax</sub>    | -                | 3.2                      | _           | V <sub>pp</sub> |

NOTES: 1. Values specified are pure numbers to the base 10.

2. Typical performance parameters indicate the potential of the device under ideal operating conditions.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active Mode, Rx Gain = 01111, Vol Adj = 0111,  $f_{\text{in}} = 1.0 \text{ kHz}$ , unless otherwise noted.)

| Characteristics                                                                                                                  | Input<br>Pin              | Measure<br>Pin | Symbol             | Min                               | Тур                      | Max         | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------|--------------------|-----------------------------------|--------------------------|-------------|-------|

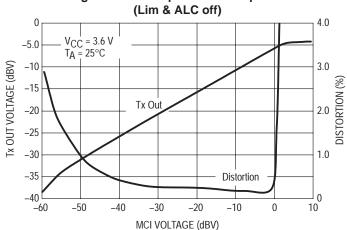

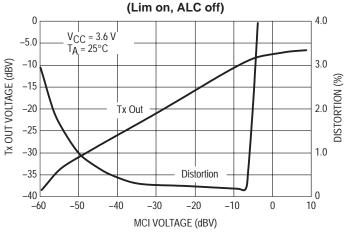

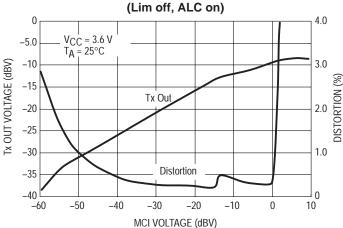

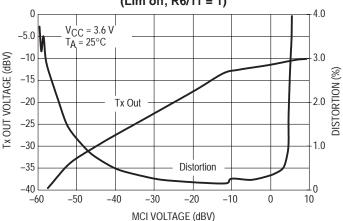

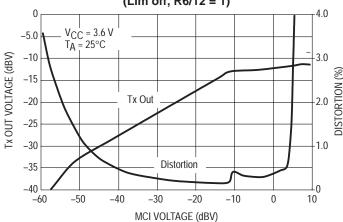

| Tx AUDIO PATH (V <sub>CC</sub> = 3.6 V, Limiter, Mutes, ALC d                                                                    | isabled, T <sub>A</sub> = | 25°C, Gain =   | 1, Active Mod      | e, f <sub>in</sub> = 1.0          | kHz)                     |             |       |

| Absolute Gain (V <sub>in</sub> = −10 dBV)                                                                                        | MCI                       | TX Out         | G                  | -4.0                              | 0                        | 4.0         | dB    |

| Gain Tracking (Referenced to Tx Out for<br>V <sub>in</sub> = −10 dBV)                                                            | MCI                       | Tx Out         | Gt                 |                                   |                          |             | dB    |

| $V_{in} = -30 \text{ dBV}$<br>$V_{in} = -40 \text{ dBV}$                                                                         |                           |                |                    | –11<br>–17                        | -10<br>-15               | -9.0<br>-13 |       |

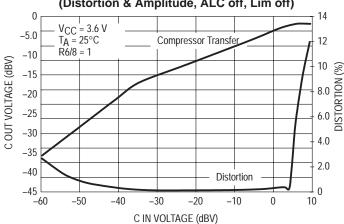

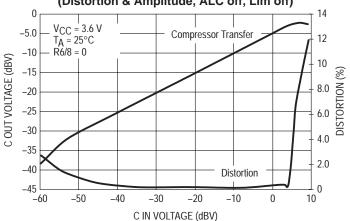

| Total Harmonic Distortion (V <sub>in</sub> = −10 dBV)                                                                            | MCI                       | Tx Out         | THD                | _                                 | 0.5                      | 1.2         | %     |

| Maximum Output Voltage (Increase input voltage until output voltage THD = 5%, then measure output voltage. Tx Gain Adj = 8.0 dB) | MCI                       | Tx Out         | V <sub>Omax</sub>  | -8.0                              | -5.0                     | -           | dBV   |

| Input Impedance                                                                                                                  |                           | C In           | Z <sub>in</sub>    | -                                 | 10                       | _           | kΩ    |

| Attack Time C <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k                                                                  | C In                      | Tx Out         | ta                 | _                                 | 3.0                      | _           | mS    |

| Release Time C <sub>cap</sub> = 0.5 μF, R <sub>filt</sub> = 40 k                                                                 | C In                      | Tx Out         | t <sub>r</sub>     | -                                 | 13.5                     | _           | mS    |

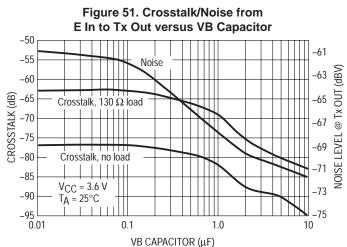

| Expander to Compressor Crosstalk ( $V_{in} = -20 \text{ dBV}$ , PA no load, $VC_{in} = AC \text{ Gnd}$ )                         | E In                      | Tx Out         | СТ                 | -                                 | -60                      | -40         | dB    |

| Tx Muting ( $V_{in} = -10 \text{ dBV}$ )                                                                                         | MCI                       | Tx Out         | M <sub>C</sub>     | -                                 | -88                      | -60         | dB    |

| ALC Output Level (When Enabled)                                                                                                  | MCI                       | Tx Out         | ALCout             |                                   |                          |             | dBV   |

| $V_{in} = -10 \text{ dBV}$                                                                                                       |                           |                |                    | -15                               | -13                      | -8.0        |       |

| V <sub>in</sub> = −2.5 dBV<br>ALC Slope (When Enabled)                                                                           | MCI                       | Tx Out         | Slope              | -13<br>0.1                        | -11<br>0.25              | -6.0<br>0.4 | dB/dB |

| $V_{in} = -10 \text{ dBV}$<br>$V_{in} = -2.5 \text{ dBV}$                                                                        | IVICI                     | 1x Out         | Slope              | 0.1                               | 0.23                     | 0.4         | ub/ub |

| ALC Input Dynamic Range                                                                                                          | C In                      | Tx Out         | DR                 | _                                 | -16 to<br>-2.5           | -           | dBV   |

| Limiter Output Level (When Enabled, $V_{in} = -2.5$ dBV)                                                                         | Lim In                    | Tx Out         | V <sub>lim</sub>   | -10                               | -7.0                     | _           | dBV   |

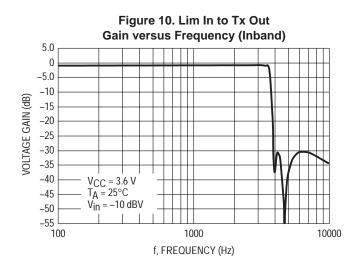

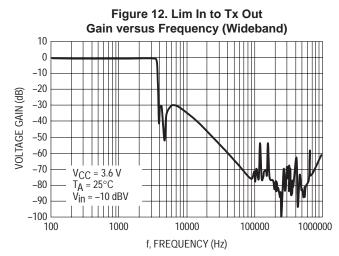

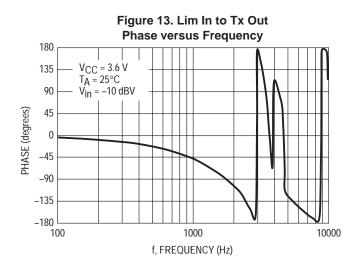

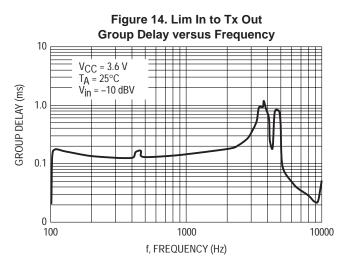

| Tx High Frequency Corner (V <sub>in</sub> = -10 dBV, Unity Gain) SCF Counter = 31 <sub>d</sub>                                   | Lim In                    | Tx Out         | Tx f <sub>ch</sub> | 3.45                              | 3.65                     | 3.85        | kHz   |

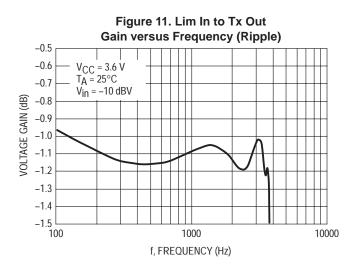

| Low Pass Filter Passband Ripple (V <sub>in</sub> = −10 dBV)                                                                      | Lim In                    | Tx Out         | Ripple             | _                                 | 0.4                      | 1.0         | dB    |

| MCU Clock or SCF Spurs ( $V_{in} = -10$ dBv, relative to SCF or MCU Fundamental)                                                 | Lim In                    | Tx Out         | -                  | -                                 | -25                      | _           | dBc   |

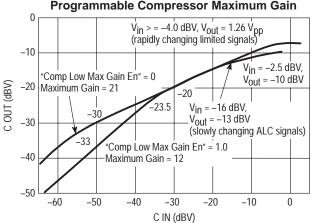

| Maximum Compressor Gain (V <sub>in</sub> = -70 dBV)<br>R6/8 = 0                                                                  | MCI                       | Tx Out         | AV <sub>max</sub>  | _                                 | 21                       | _           | dB    |

| R6/8 = 1                                                                                                                         |                           |                |                    | _                                 | 12                       | _           |       |

| Tx Gain Adjust Range                                                                                                             | Lim In                    | Tx Out         | Tx Range           | _                                 | -9.0 to 10               | _           | dB    |

| Tx Gain Adjust Steps                                                                                                             | Lim In                    | Tx Out         | Tx N               | -                                 | 20                       | -           |       |

| <b>DATA AMP COMPARATOR</b> ( $V_{CC} = 3.6 \text{ V}, V_B = 1.5 \text{ V}$                                                       | , T <sub>A</sub> = 25°C,  | Active or Rece | eive Mode)         |                                   |                          |             |       |

| Hysteresis                                                                                                                       | DS In                     | DS Out         | Hys                | 20                                | 42                       | 60          | mV    |

| Threshold Voltage                                                                                                                | DS In                     | DS Out         | VT                 | _                                 | V <sub>CC</sub> -0.7     | _           | V     |

| Input Impedance                                                                                                                  |                           | DS In          | Z <sub>in</sub>    | 200                               | 250                      | 280         | kΩ    |

| Output Impedance                                                                                                                 |                           | DS Out         | Z <sub>out</sub>   | _                                 | 100                      | _           | kΩ    |

| Output High Voltage ( $V_{in} = V_{CC} - 1.0 \text{ V}, I_{oh} = 0 \text{ mA}$ )                                                 | DS In                     | DS Out         | V <sub>oh</sub>    | V <sub>CC</sub><br>Audio<br>– 0.1 | V <sub>CC</sub><br>Audio | -           | V     |

| Output Low Voltage ( $V_{in} = V_{CC} - 0.4 \text{ V}, I_{Ol} = 0 \text{ mA}$ )                                                  | DS In                     | DS Out         | Vol                | _                                 | 0.1                      | 0.4         | V     |

| Maximum Frequency                                                                                                                | DS In                     | DS Out         | F <sub>max</sub>   | _                                 | 10                       | _           | kHz   |

**NOTES:** 1. Values specified are pure numbers to the base 10.

<sup>2.</sup> Typical performance parameters indicate the potential of the device under ideal operating conditions.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{CC} = 3.6 \text{ V}$ ,  $V_B = 1.5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , Active Mode, Rx Gain = 01111, Vol Adj = 0111,  $f_{\text{in}} = 1.0 \text{ kHz}$ , unless otherwise noted.)

| Characteristics                                                          | Input<br>Pin                           | Measure<br>Pin       | Symbol             | Min                                | Тур                | Max    | Unit |

|--------------------------------------------------------------------------|----------------------------------------|----------------------|--------------------|------------------------------------|--------------------|--------|------|

| RSSI/LOW BATTERY A/D ( $V_{CC} = 3.6 \text{ V}, V_{B} = 1.5 \text{ V}$   | /, T <sub>A</sub> = 25°C, Ac           | tive or Receiv       | re Mode)           |                                    |                    |        |      |

| RSSI Voltage Range                                                       | RSSI In                                | SPI                  | RSSI               |                                    |                    |        | V    |

| Minimum (PE/17, 12 – 0)                                                  |                                        |                      | Range              |                                    |                    |        |      |

| Minimum (R5/17–12 = 0)<br>Interim (R5/17–12 = 100000)                    |                                        |                      |                    | .744                               | 0 –                |        |      |

| Maximum (R5/17–12 = 1)                                                   |                                        |                      |                    | _                                  | 1.6                | _      |      |

| Low Battery Detect Operating Range                                       | V <sub>CC</sub> Audio                  | SPI                  | LOWB<br>Range      |                                    |                    |        | V    |

| Minimum                                                                  |                                        |                      |                    | _                                  | 2.7                | -      |      |

| Interim (R5/23–18 = 101111)<br>Maximum (R5/23–18 = 1)                    |                                        |                      |                    | 2.7                                | -<br>3.75          | 3.1    |      |

| Differential Non–linearity                                               | RSSI In/                               | SPI                  | A/D DNL            | -1.0                               | ±0.5               | 1.0    | LSB  |

| <u>,                                      </u>                           | V <sub>CC</sub> Audio                  |                      |                    |                                    |                    | 1.0    |      |

| Resolution                                                               | RSSI In/<br>VCC Audio                  | SPI                  | Resolution         | -                                  | 6                  | _      | Bits |

| Input Current                                                            |                                        | RSSI In              | l <sub>in</sub>    | -80                                | 20                 | 80     | nA   |

| REFERENCE FREQUENCY ( $V_{CC} = 3.6 \text{ V}, V_{B} = 1.5 \text{ C}$    | 5 V, T <sub>A</sub> = 25°C,            | Active Mode)         |                    |                                    |                    |        |      |

| Input Current High (V <sub>in</sub> = V <sub>CC</sub> )                  |                                        | Fref in              | lih                | 2.0                                | 5.0                | 15     | μА   |

| Input Current Low (V <sub>in</sub> = 0 V)                                |                                        | F <sub>ref in</sub>  | lil                | -15                                | -5.0               | -2.0   | μΑ   |

| Minimum Input Voltage F <sub>ref</sub> In                                | F <sub>ref in</sub>                    | Fref out             | Vin                | 300                                | _                  | _      | mVpp |

| Input Impedance                                                          |                                        | F <sub>ref in</sub>  | z <sub>in</sub>    | -                                  | 2.9 pF  11.6<br>kΩ | _      |      |

| Output Impedance                                                         |                                        | F <sub>ref out</sub> | Z <sub>out</sub>   | -                                  | 2.5 pF  4.5<br>kΩ  | -      |      |

| MICROPROCESSOR INTERFACE ( $V_{CC}$ = 3.6 V, V                           | <sub>B</sub> = 1.5 V, T <sub>A</sub> = | 25°C, Active of      | or Receive Mo      | ode)                               |                    |        |      |

| Input Low Voltage                                                        | Data/EN<br>/CLK                        |                      | V <sub>il</sub>    | 0                                  | _                  | 0.3    | V    |

| Input High Voltage                                                       | Data/EN                                |                      | Vih                | Tx PLL                             | _                  | Tx PLL | V    |

|                                                                          | /CLK                                   |                      |                    | V <sub>CC</sub> -                  |                    | Vcc    |      |

| Input Current Low (V <sub>in</sub> = 0.3 V, Standby Mode) Data, EN, CLK  |                                        | Data, EN,<br>CLK     | I <sub>il</sub>    | -5.0                               | 0.4                | -      | μА   |

| Input Current High (V <sub>in</sub> = 3.3 V, Standby Mode) Data, EN, CLK |                                        | Data, EN,<br>CLK     | l <sub>ih</sub>    | _                                  | 1.6                | 5.0    | μА   |

| Hysteresis Voltage Data, EN, CLK                                         |                                        | Data, EN,<br>CLK     | V <sub>hys</sub>   | _                                  | 1.0                | _      | V    |

| Maximum Clock Frequency                                                  | CLK                                    |                      | F <sub>max</sub>   | 2.0                                | _                  | _      | MHz  |

| Input Capacitance Data, EN, CLK                                          |                                        | Data, CLK,<br>EN     | C <sub>in</sub>    | -                                  | 8.0                | -      | pF   |

| EN to CLK Setup Time                                                     |                                        | EN, CLK              | t <sub>suEC</sub>  | _                                  | 200                | _      | nS   |

| Data to CLK Setup Time                                                   |                                        | Data, CLK            | t <sub>suDC</sub>  | -                                  | 100                | _      | nS   |

| Hold Time                                                                |                                        | Data, CLK            | th                 | _                                  | 90                 | _      | nS   |

| Recovery Time                                                            |                                        | EN, CLK              | t <sub>rec</sub>   | _                                  | 90                 | _      | nS   |

| Input Pulse Width                                                        |                                        | EN, CLK              | t <sub>W</sub>     | _                                  | 100                | _      | nS   |

| <u> </u>                                                                 |                                        | LIV, OLIX            |                    |                                    |                    |        |      |

| MCU Interface Power–Up Delay                                             |                                        | MOLLO                | t <sub>puMCU</sub> |                                    | 100                | _      | μS   |

| Output High Voltage (I <sub>Oh</sub> = 0 mA)                             |                                        | MCU Clk<br>Out       | V <sub>oh</sub>    | Tx PLL<br>V <sub>CC</sub> –<br>0.3 | 3.5                | _      | V    |

**NOTES:** 1. Values specified are pure numbers to the base 10.

<sup>2.</sup> Typical performance parameters indicate the potential of the device under ideal operating conditions.

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (\text{V}_{CC} = 3.6 \ \text{V}, \ \text{V}_{B} = 1.5 \ \text{V}, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{Active Mode, Rx Gain} = 01111, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{C}_{A} = 25$ Vol Adj = 0111, f<sub>in</sub> = 1.0 kHz, unless otherwise noted.)

| Characteristics                                                                                                                                    | Input<br>Pin              | Measure<br>Pin   | Symbol            | Min                    | Тур                             | Max         | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|-------------------|------------------------|---------------------------------|-------------|------|

| MICROPROCESSOR INTERFACE (V <sub>CC</sub> = 3.6 V, V <sub>B</sub>                                                                                  | = 1.5 V, T <sub>A</sub> = | 25°C, Active     | or Receive Mo     | ode)                   |                                 |             | •    |

| Output Low Voltage (I <sub>OI</sub> = 0 mA)                                                                                                        |                           | MCU Clk<br>Out   | Vol               | _                      | 0.1                             | 0.3         | V    |

| Output High Voltage (I <sub>Oh</sub> = 0 mA)                                                                                                       |                           | Data             | Voh               | Tx PLL<br>VCC -<br>0.3 | 3.5                             | _           | V    |

| Output Low Voltage (I <sub>OI</sub> = 0 mA)                                                                                                        |                           | Data             | V <sub>ol</sub>   | -                      | 0.1                             | 0.3         | V    |

| Rx/Tx PLL CHARACTERISTICS ( $V_{CC} = 3.6 \text{ V}, V_{B} =$                                                                                      | 1.5 V, T <sub>A</sub> = 2 | 5°C, Active or   | Receive Mod       | e)                     |                                 |             |      |

| Output Source Current (VpD = 0.5 V or VCC $-$ 0.5 V) $\pm$ 100 $\mu$ A mode                                                                        |                           | Rx PD &          | l <sub>oh</sub>   | -130                   | -100                            | -70         | μА   |

| ±400 μA mode                                                                                                                                       |                           | Tx PD            |                   | -520                   | -400                            | -280        |      |

| Output Sink Current (VpD = 0.5 V or V <sub>CC</sub> $-$ 0.5 V) $\pm 100~\mu A$ mode $\pm 400~\mu A$ mode                                           |                           | Rx PD &<br>Tx PD | l <sub>ol</sub>   | 70<br>280              | 100<br>400                      | 130<br>520  | μА   |

| Current Match, $\pm 100~\mu A$ mode or $\pm 400~\mu A$ mode,<br>VPD = V <sub>CC</sub> / 2 (i.e., 100 x (ABS (I <sub>Oh</sub> / I <sub>Ol</sub> ))) |                           | Rx PD<br>Tx PD   | Match             | 80                     | 100                             | 125         | %    |

| Output Off Current (V <sub>PD</sub> = V <sub>CC</sub> /2), $\pm$ 100 $\mu$ A mode or $\pm$ 400 $\mu$ A mode                                        |                           | Rx PD<br>Tx PD   | l <sub>oz</sub>   | -80                    | 5.0                             | 80          | nA   |

| Input Current Low (V <sub>in</sub> = 0 V)                                                                                                          |                           | FRx FTx          | I <sub>il</sub>   | -10                    | -7.5                            | _           | μА   |

| Input Current High (Vin = VCC)                                                                                                                     |                           | FRx FTx          | lih               | _                      | 10                              | 14          | μА   |

| Input Bias Voltage                                                                                                                                 |                           | FRx FTx          | V <sub>bias</sub> | -                      | 1.5                             | -           | V    |

| Output Voltage High (I <sub>Oh</sub> = 0 mA, Voltage Mode)                                                                                         |                           | FRxMC            | V <sub>oh</sub>   | _                      | Rx PLL<br>V <sub>CC</sub> = 0.1 | _           | V    |

| Output Voltage High (I <sub>Oh</sub> = 0 mA, Voltage Mode)                                                                                         |                           | FTxMC            | Voh               | _                      | Tx PLL<br>VCC = 0.1             | _           | V    |

| Output Voltage Low (I <sub>OI</sub> = 0 mA, Voltage Mode)                                                                                          |                           | FRxMC<br>FTxMC   | V <sub>ol</sub>   | _                      | 0.1                             | _           | V    |

| Output Current High (V <sub>Oh</sub> = 0.8 V, Current Mode)                                                                                        |                           | FRxMC<br>FTxMC   | loh               | -130                   | -100                            | -70         | μА   |

| Output Current Low (V <sub>Ol</sub> = 0.8 V, Current Mode)                                                                                         |                           | FRxMC<br>FTxMC   | l <sub>Ol</sub>   | 70                     | 100                             | 130         | μА   |

| Maximum Input Frequency                                                                                                                            |                           | FRx<br>FTx       | F <sub>max</sub>  | 20                     | _                               | _           | MHz  |

| Input Voltage Swing                                                                                                                                |                           | FRx<br>FTx       | Vin               | 200                    | -                               | 1200        | mVpp |

| Modulus Control Prop Delay                                                                                                                         | FRx<br>FTx                | FRxMC<br>FTxMC   | -                 |                        | 20                              | -           | nS   |

| LO2 PLL CHARACTERISTICS (V <sub>CC</sub> = 3.6 V, V <sub>B</sub> = 1.                                                                              | 5 V, T <sub>Δ</sub> = 25° | C, Active Mod    | e)                |                        |                                 |             |      |

| Output Source Current ( $V_{PD} = 0.5 \text{ V}$ or $V_{CC} - 0.5 \text{ V}$ )                                                                     |                           | LO2PD            | l <sub>oh</sub>   |                        |                                 |             | μΑ   |

| ±100 µA mode                                                                                                                                       |                           |                  |                   | -130<br>530            | -100<br>400                     | -70         |      |

| ±400 μA mode  Output Sink Current (VpD = 0.5 V or V <sub>CC</sub> – 0.5 V)  ±100 μA mode                                                           |                           | LO2PD            | l <sub>ol</sub>   | -520<br>70             | -400<br>100                     | -280<br>130 | μА   |

| ±400 μA mode  Current Match, ±100 μA mode or ±400 μA mode,  VPD = VCC / 2 (i.e., 100 x (ABS (I <sub>Oh</sub> / I <sub>Ol</sub> )))                 |                           | LO2PD            | Match             | 80                     | 100                             | 520<br>125  | %    |

NOTES: 1. Values specified are pure numbers to the base 10.

2. Typical performance parameters indicate the potential of the device under ideal operating conditions.

$\textbf{ELECTRICAL CHARACTERISTICS (continued)} \ (\text{V}_{CC} = 3.6 \ \text{V}, \ \text{V}_{B} = 1.5 \ \text{V}, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{Active Mode, Rx Gain} = 01111, \ \text{T}_{A} = 25^{\circ}\text{C}, \ \text{C}_{A} = 25$ Vol Adj = 0111, f<sub>in</sub> = 1.0 kHz, unless otherwise noted.)

| Characteristics                                                                                               | Input<br>Pin   | Measure<br>Pin | Symbol             | Min    | Тур                 | Max    | Unit |  |

|---------------------------------------------------------------------------------------------------------------|----------------|----------------|--------------------|--------|---------------------|--------|------|--|

| LO2 PLL CHARACTERISTICS (V <sub>CC</sub> = 3.6 V, V <sub>B</sub> = 1.5 V, T <sub>A</sub> = 25°C, Active Mode) |                |                |                    |        |                     |        |      |  |

| Output Off Current (V <sub>PD</sub> = V <sub>CC</sub> /2)                                                     |                | LO2PD          | l <sub>oz</sub>    | -80    | 5.0                 | 80     | nA   |  |

| Input Current Low (V <sub>in</sub> = 0.5 V)                                                                   |                | LO2Ctl         | lil                | -1.0   | -0.02               | -      | μА   |  |

| Input Current High (V <sub>in</sub> = V <sub>CC</sub> - 0.5 V)                                                |                | LO2Ctl         | l <sub>ih</sub>    | _      | 0.02                | 1.0    | μΑ   |  |

| Input Voltage Range                                                                                           |                | LO2Ctl         | V <sub>range</sub> | 0.4    | _                   | Vcc    | V    |  |

| Maximum 2nd LO Frequency                                                                                      |                |                |                    | 65     | 80                  | _      | MHz  |  |

| LO2 Out Drive (25 Ω load)                                                                                     |                |                | V <sub>out</sub>   | 112    | 180                 | 245    | mVpp |  |

| <b>COUNTERS</b> (V <sub>CC</sub> = 3.6 V, V <sub>B</sub> = 1.5 V, T <sub>A</sub> = 25°C                       | , Active Mode) | •              | •                  | •      | •                   |        | •    |  |

| 12-Bit Reference Counter Range [Note 1]                                                                       |                |                |                    | _      | 3 to 4095           | -      |      |  |

| 13–Bit N Counter Range [Note 1]                                                                               |                |                |                    | _      | 3 to 8191           | _      |      |  |

| 7–Bit A Counter Range [Note 1]<br>64/65 Modulus Prescaler<br>128/129 Modulus Prescaler                        |                |                |                    | _<br>_ | 0 to 63<br>0 to 127 | -<br>- |      |  |

| 14-Bit LO2 Counter Range [Note 1]                                                                             |                |                |                    | -      | 12 to<br>16383      | -      |      |  |

| 6-Bit Counters (for SCF) [Note 1]                                                                             |                |                |                    | _      | 3 to 63             | -      |      |  |

NOTES: 1. Values specified are pure numbers to the base 10.

2. Typical performance parameters indicate the potential of the device under ideal operating conditions.

# PIN FUNCTION DESCRIPTION

| Pin | Symbol/Type        | Description                              | Description                                                                                                                    |

|-----|--------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1   | FRx MC<br>(Output) | Rx PLL V <sub>CC</sub> 100 µA FRx MC     | Modulus Control Output for the Rx PLL section. Can be set to output in current mode or voltage mode, selectable with bit 3/16. |

| 2   | FRx<br>(Input)     | PLL<br>VCC<br>2<br>PRX Bias<br>FRX 80 μA | Receives the signal from the external 64/65 or 128/129 prescaler. DC bias is at 1.3 V.                                         |

NOTE: 1. All  $V_{CC}$  pins must be within  $\pm 0.5~V$  of each other.

| Pin | Symbol/Type                       | Description Description                                                                  | Description                                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

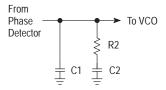

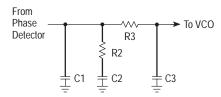

| 3   | Rx PLL V <sub>CC</sub> (Input)    | Rx PLL Section 3 10 0.01 10 VCC                                                          | Supply pin for the Rx PLL section. Allowable range is 2.7 to 5.5 V and must be within 0.5 V of all other V <sub>CC</sub> pins. Good bypassing is required and isolation with a 10 $\Omega$ resistor is recommended.                                                                                                                                             |

| 4   | Rx PD<br>(Output)                 | Rx PLL VCC 125                                                                           | Rx Phase Detector Output. The output either sources or sinks current, or neither, depending on the phase difference of the phase detector input signals. During lock, very narrow pulses with a frequency equal to the PLL reference frequency are present. Output current is either $\pm 100~\mu\text{A}$ or $\pm 400~\mu\text{A}$ , selectable with bit 2/20. |

| 5   | PLL Gnd                           |                                                                                          | Ground pin for the PLL section. A direct connection to a ground plane is strongly recommended.                                                                                                                                                                                                                                                                  |

| 6   | Tx PD<br>(Output)                 | Same as Pin 4, except powered from Tx PLL $V_{\hbox{\footnotesize CC}}$ .                | Tx Phase Detector Output. Description same as for Pin 4, except bit 1/20 controls the current level.                                                                                                                                                                                                                                                            |

| 7   | Tx PLL V <sub>CC</sub><br>(Input) | Tx PLL Section, MCU Serial Interface, Reference Oscillator                               | Supply pin for the Tx PLL section, MCU Serial Interface, MCU Clock Counter, and the Reference Oscillator. Allowable range is 2.7 to 5.5 V and must be within 0.5 V of all other V $_{CC}$ pins. Good bypassing is required and isolation with a 10 $\Omega$ resistor is recommended.                                                                            |

| 8   | FTx<br>(Input)                    | Same as Pin 2.                                                                           | Receives the signal from the external 64/65 or 128/129 prescaler. DC bias is at 1.5 V.                                                                                                                                                                                                                                                                          |

| 9   | FTx MC<br>(Output)                | Tx PLL V <sub>CC</sub> 100 µA  Current Mode  Tx PLL V <sub>CC</sub> 100 µA  Voltage Mode | Modulus Control Output for the Tx PLL section. Can be set to output in a current mode or a voltage mode, selectable with bit 3/16.                                                                                                                                                                                                                              |

NOTE: 1. All  $V_{\mbox{CC}}$  pins must be within  $\pm 0.5$  V of each other.

| Pin | Symbol/Type             | Description                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|-------------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

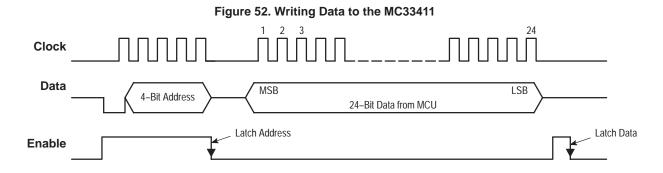

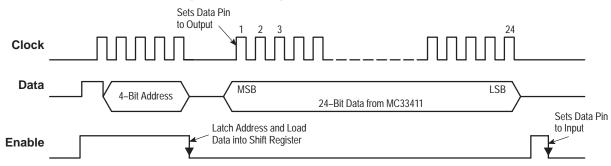

| 10  | EN<br>(Input)           | Tx PLL<br>Vcc<br>Enable ≈1.0 µA = =                    | Enable Input for the MCU Interface section. Hysteresis threshold is within 0.5 V of ground and V <sub>CC</sub> . See text for proper waveform required at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11  | CLK<br>(Input)          | Same as Pin 10.                                        | Clock Input for the MCU Interface section. Hysteresis threshold is within 0.5 V of ground and V <sub>CC</sub> . Data is written or read out on clock's rising edge. Maximum clock rate is 2.0 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12  | Data<br>(I/O)           | Tx PLL VCC  12 Data  1.0 µA  Tx PLL VCC  Disable  Data | Data I/O line for the MCU Interface section. Both address and data are provided to/from this pin. Input threshold is within 0.5 V of ground and V <sub>CC</sub> . Data is written or read out on clock's rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13  | MCU Clk Out<br>(Output) | Tx PLL VCC VCC VCC Clk Out                             | The microprocessor clock output is derived from the reference oscillator and a programmable divider with divide ratios of 2 to 312.5. It can be used to drive a microprocessor and thereby reduce the number of crystals required in the system design. The driver has an internal resistor in series with the output which can be combined with an external capacitor to form a low–pass filter to reduce radiated noise on the PCB. This output also functions as the output for the counter test modes.  1) For the MC33411A the Clk Out can be disabled via the MCU interface.  2) For the MC33411B this output is always active (on). |

| 14  | Gnd Digital             |                                                        | Ground for the Data, MCU Clk Out, and F <sub>ref</sub> Out digital Outputs. A direct connection to the ground plane is strongly recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

**NOTE:** 1. All  $V_{CC}$  pins must be within  $\pm 0.5$  V of each other.

| Pin    | Symbol/Type                      | Description Description                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|----------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

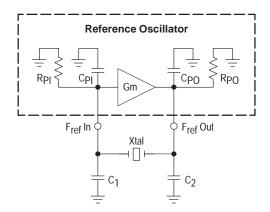

| 15, 16 | F <sub>ref</sub> In,<br>Fref Out | Tx PLL VCC  100 Fref Out Tx PLL VCC  Tx PLL VCC  Tx PLL Fref In | Reference Frequency Input for various portions of the circuit, including the PLLs, SCF clock, etc. A crystal (4 to 18.25 MHz) may be connected as shown, or an external frequency source may be capacitor coupled to Pin 15. See text for crystal requirements.  1) For the MC33411A the F <sub>ref</sub> Out can be disabled via the MCU interface. 2) For the MC33411B this output is always active (on). |

| 17     | DS Out<br>(Output)               | VCC Audio Audio 100 k                                           | Data Slicer Output (open collector with internal 100 kΩ pull–up resistor).                                                                                                                                                                                                                                                                                                                                  |

| 18     | Tx Out<br>(Output)               | VCC Audio 18, 20 C Tx Out,                                      | Tx Out is the Tx path audio output. Internally this pin has a low–pass filter circuitry with –3.0 dB bandwidth of 4.0 kHz. Tx gain and mute are programmable through the MCU interface. This pin is sensitive to load capacitance.                                                                                                                                                                          |

| 20     | C Out<br>(Output)                | V <sub>B</sub>                                                  | C Out is the compressor output.                                                                                                                                                                                                                                                                                                                                                                             |

| 19     | Lim In<br>(Input)                | VCC Audio  19 400 k  VB                                         | Lim In is the limiter input. This pin is internally biased and has an input impedance of 400 kΩ. Lim In must be ac–coupled.                                                                                                                                                                                                                                                                                 |

| 21     | Ссар                             | VCC Audio Audio  21  Ccap                                       | $C_{\mbox{cap}}$ is the compressor rectifier filter capacitor pin. It is recommended that an external filter capacitor to VCC audio be used. A practical capacitor range is 0.1 to 1.0 $\mu F$ . The recommended value is 0.47 $\mu F$ .                                                                                                                                                                    |

**NOTE:** 1. All  $V_{CC}$  pins must be within  $\pm 0.5 \ V$  of each other.

| Pin | Symbol/Type                      | PIN FUNCTION DESCRIPTION (con                       | Description                                                                                                                                                                                    |

|-----|----------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22  | C In<br>(Input)                  | VCC<br>Audio<br>22<br>O<br>C In                     | C In is the compressor input. This pin is internally biased and has an input impedance of 12.5 k $\Omega$ . C In must be ac–coupled.                                                           |

| 23  | V <sub>CC</sub> Audio<br>(Input) | Audio Section, Filters, A/D Converters, Data Slicer | Supply input for the audio section, filters, A/D Converters, and Data Slicer. Allowable range is 2.7 to 5.5 V. Good bypassing is required.                                                     |

| 24  | MCO<br>(Output)                  | Audio VCC 24 MCO                                    | Output of the Microphone amplifier. Maximum output swing is $\approx 3.0 \text{ V}_{pp}$ for $\text{V}_{CC} \ge 3.0 \text{ V}$ . Maximum output current is >1.0 mA peak.                       |

| 25  | MCI<br>(Input)                   | VCC Audio  Audio  VB  VB  VB  VB  VB                | Inverting input of the microphone amplifier. Gain and frequency response are set with external resistors and capacitors from this pin to the audio source and to MCO.                          |

| 26  | VAG<br>(Output)                  | Audio VCC 26 OAG ± μF                               | Analog ground for the audio section filters. VAG is equal to VB and is buffered from VB. Maximum current which can be sourced from this pin is 500 $\mu$ A.                                    |

| 27  | V <sub>B</sub><br>(Output)       | Audio VCC 240 27 27 4.7 μF                          | An internal 1.5 V reference for several sections. This voltage is adjustable with bits 3/20–17. Maximum source current is 100 µA. PSRR, noise and crosstalk depends on the external capacitor. |

| 28  | V <sub>CC</sub> PA<br>(Input)    | 28 10 0.01 Vcc  Audio Power                         | Supply pin for the power amplifier outputs. Allowable range is 2.7 to 5.5 V. Good bypassing is required.                                                                                       |

**NOTE:** 1. All  $V_{CC}$  pins must be within  $\pm 0.5$  V of each other.

| Pin | Symbol/Type        | PIN FUNCTION DESCRIPTION (co  Description | Description                                                                                                                                                                                                                      |

|-----|--------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29  | PAO+<br>(Output)   | Audio VCC 29 O PAO+                       | Output of the second power amplifier. This amplifier is set for unity inverting gain and is driven by PAO–. Maximum swing is 2.9 V <sub>pp</sub> and maximum output current is >5.0 mA peak. DC level is ≈1.5 V.                 |

| 30  | PAO-<br>(Output)   | Same as Pin 29.                           | Output of the first power amplifier. Its gain is set with external resistors and capacitors from this pin to PAI. Output capability is the same as Pin 28.                                                                       |

| 31  | Gnd PA             |                                           | Ground pin for the power amplifier outputs. A direct connection to a ground plane is strongly recommended.                                                                                                                       |

| 32  | PAI<br>(Input)     | VCC<br>Audio<br>PAI = VB<br>PAI = 2.5 μA  | Inverting input of the power amplifier. Gain and frequency response are set with external resistors and capacitors from this pin to the audio source and to PAO—.                                                                |

| 33  | E Out<br>(Output)  | Audio VCC 333 Rx Audio Output             | Expander output. This output is sensitive to load capacitance. Maximum output signal level is ≈2.5 V <sub>pp</sub> . Maximum output current is >1.0 mA.                                                                          |

| 34  | E <sub>cap</sub>   | VCC Audio Audio Audio Ecap                | $E_{cap}$ is the expander rectifier filter capacitor pin. Connect an external filter capacitor between V <sub>CC</sub> audio and $E_{cap}$ . The recommended capacitance range is 0.1 to 1.0 μF. The suggested value is 0.47 μF. |

| 35  | E In<br>(Input)    | VCC<br>Audio<br>35 30 k<br>E In           | The expander input pin is internally biased and has input impedance of 30 k $\Omega$ .                                                                                                                                           |

| 36  | Rx Out<br>(Output) | V <sub>CC</sub> Audio                     | Rx Out is the Rx audio output. An internal low–pass filter has a –3.0 dB bandwidth of 4.0 kHz.                                                                                                                                   |

NOTE: 1. All  $V_{\mbox{CC}}$  pins must be within  $\pm 0.5$  V of each other.

| Pin | Symbol/Type                    | Description                                            | Description                                                                                                                                                                                                      |

|-----|--------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37  | RSSI In<br>(Input)             | VCC Audio  RSSI In                                     | Voltage input to RSSI A/D converter. Full scale is 0 to 1.6 V.                                                                                                                                                   |

| 38  | Rx Audio In<br>(Input)         | VCC<br>Audio<br>RX Audio<br>In                         | Input to the Rx Audio Path. Input impedance is 600 kΩ. Input signal must be capacitor coupled                                                                                                                    |

| 39  | DS In<br>(Input)               | VCC<br>Audio<br>DS In                                  | Input for the digital data from the RF Receiver section. Input impedance is 250 kΩ. Hysteresis is internally provided. Input signal level must be between 50 and 700 mVpp.                                       |

| 40  | Gnd Audio                      |                                                        | Ground pin for the audio section. A direct connection to a ground plan is strongly recommended.                                                                                                                  |

| 41  | LO2 Out<br>(Output)            | LO2<br>VCC<br>VCC<br>VCC<br>50<br>VCC<br>50<br>LO2 Out | Buffered output of the 2nd LO. This high frequency output is a current, requiring an external pullup resistor.                                                                                                   |

| 42  | LO2 V <sub>CC</sub><br>(Input) | 42 10 0.01 10 V <sub>CC</sub>                          | Supply pin for the LO2 section. Allowable range is 2.7 to 5.5 V and must be within 0.5 V of all other V <sub>CC</sub> pins. Good bypassing is required and isolation with a 10 $\Omega$ resistor is recommended. |

NOTE: 1. All  $V_{\mbox{CC}}$  pins must be within  $\pm 0.5$  V of each other.

| Pin    | Symbol/Type       | Description                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43, 45 | LO2+, LO2-        | 102<br>VCC<br>VCC<br>VCC<br>VCC                                                                     | The 2nd LO. External tank components are required. The internal capacitance across the pins is adjustable from 0 to 7.6 pF for fine tuning performance with bits 7/20–18.  LO2 Control is the dc control input for this VCO.                                                                                                                                     |

| 44     | (Input)           | 45 LO2- LO2 VCC 44 LO2 Ctl 555 k                                                                    | Typically it is the output of the low–pass filter fed from the phase detector output.                                                                                                                                                                                                                                                                            |

| 46     | LO2 Gnd           |                                                                                                     | Ground pin for the LO2 section. A direct connection to a ground plane is strongly recommended.                                                                                                                                                                                                                                                                   |

| 47     | LO2PD<br>(Output) | LO2 PLL V <sub>CC</sub> 100/ 400 μA  125  LO2 PLL V <sub>CC</sub> 100/ 47 to Filter  LO2 PD  LO2 PD | LO2 Phase Detector Output. The output either sources or sinks current, or neither, depending on the phase difference of the phase detector input signals. During lock, very narrow pulses with a frequency equal to the PLL reference frequency are present. Output current is either $\pm 100~\mu\text{A}$ or $\pm 400~\mu\text{A}$ , selectable with bit 3/14. |

| 48     | LO2 Gnd           |                                                                                                     | Ground pin for the LO2 section. A direct connection to a ground plane is strongly recommended.                                                                                                                                                                                                                                                                   |

**NOTE:** 1. All  $V_{CC}$  pins must be within  $\pm 0.5$  V of each other.

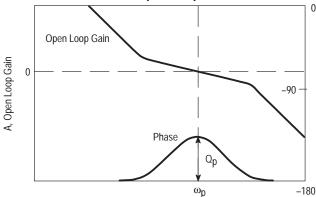

#### **FUNCTIONAL DESCRIPTION**

The following text, graphics, tables and schematics are provided to the user as a source of valuable technical information about the MC33411. This information originates from thorough evaluation of the device performance. This data was obtained by using units from typical wafer lots. It is important to note that the forgoing data and information was from a limited number of units. By no means is the user to assume that the data following is a guaranteed parametric. Only the minimum and maximum limits identified in the electrical characteristics tables found earlier in the spec are guaranteed.

Note: In the following descriptions, control bits in the MCU Serial Interface for the various functions will be identified by register number and bit number. For example, bit 3/19 indicates bit 19 of register 3. Bits 5/14–11 indicates register 5, bits 14 through 11. Please refer to Figure 1.

#### **General Circuit Description**

The MC33411A/B is a low power baseband IC designed to interface with the MC13145 UHF Wideband Receiver and MC13146 Transmitter for applications up to 2.0 GHz. The devices are primarily designated to be used for 900 MHz ISM band in a CT-900, low power, dual conversion cordless phone, but other applications such as data links with analog processing could be developed. This device contains complete baseband transmit and receive processing sections, a transmit and receive PLL section, a programmable PLL second local oscillator usable to 80 MHz,

RSSI and low battery detect circuitry and serial interface for a microprocessor.

"A" versions of the device have the ability to disable either the reference oscillator or MCU clock outputs. This feature is useful for systems where the MCU has an internal clock, allowing the user to place the MC33411 into Inactive (lowest power consumption) mode. The "A" version is also useful for systems where the MCU has a dedicated clock source, allowing for lower power consumption from the MC33411 by disabling the MCU clock output.

"B" versions of the device are intended for systems where the MCU clock will always be driven from the MC33411. These bits are purposefully "hard—wired" to the enable state to ensure proper operation of the reference oscillator and MCU clock output even during battery discharge/recharge cycles

All internal registers are completely static – no refreshing is required under normal operation conditions.

#### **DC Current**

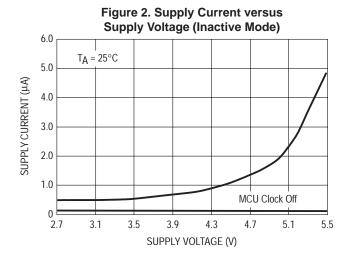

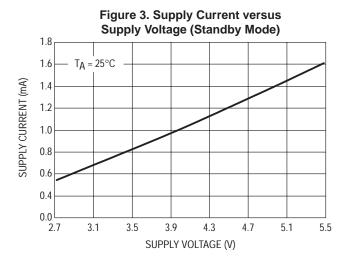

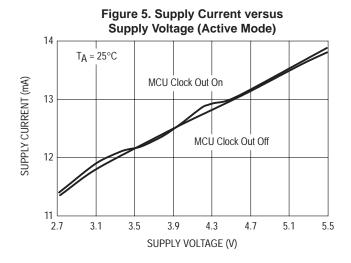

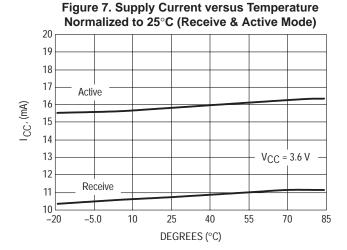

Figures 2 through 5 are the current consumption for Inactive (MC33411 "A" version only), Standby, Receive, and Active modes versus supply voltages. Figures 6 and 7 show the typical behavior of current consumption in relation to temperature.

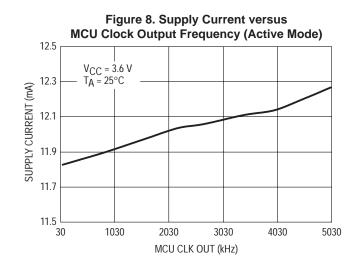

Figure 8 illustrates the effect of the MCU clock output frequency to supply current during Active mode.

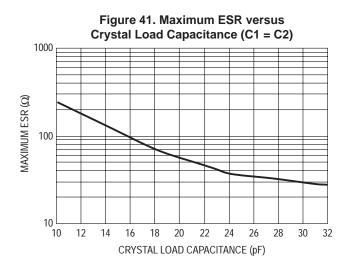

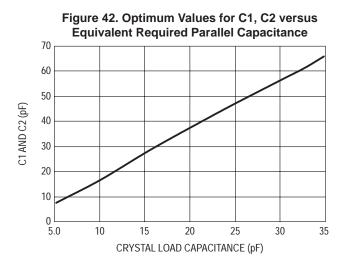

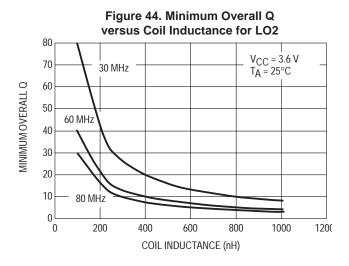

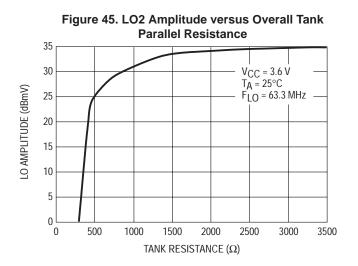

Figure 4. Supply Current versus **Supply Voltage (Receive Mode)** 10  $T_A = 25^{\circ}C$ 9.5 SUPPLY CURRENT (mA) MCU Clock Out On 9.0 MCU Clock Out Off 8.0 7.5 <u></u> 2.7 3.5 3.1 4.7 5.1 5.5 3.9 4.3 SUPPLY VOLTAGE (V)