DATA SHEET MAY 1998

## SXT6051

Revision 1.1

## STM-1/0 SDH Overhead Terminator

### **General Description**

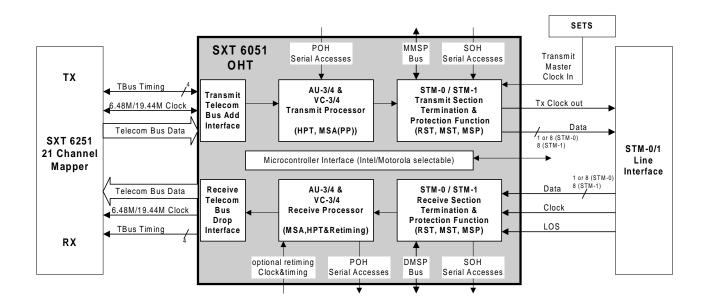

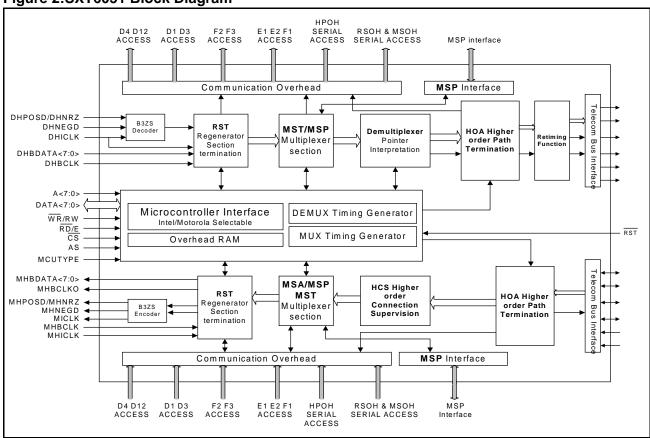

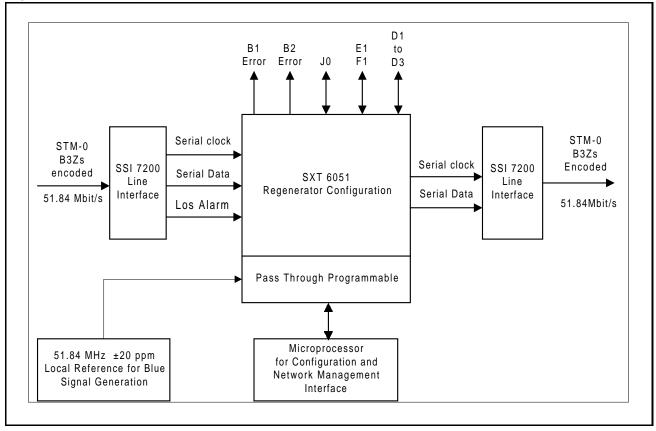

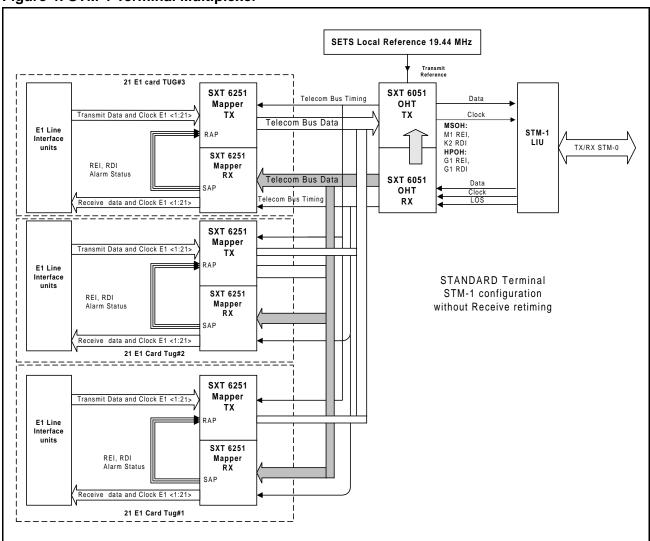

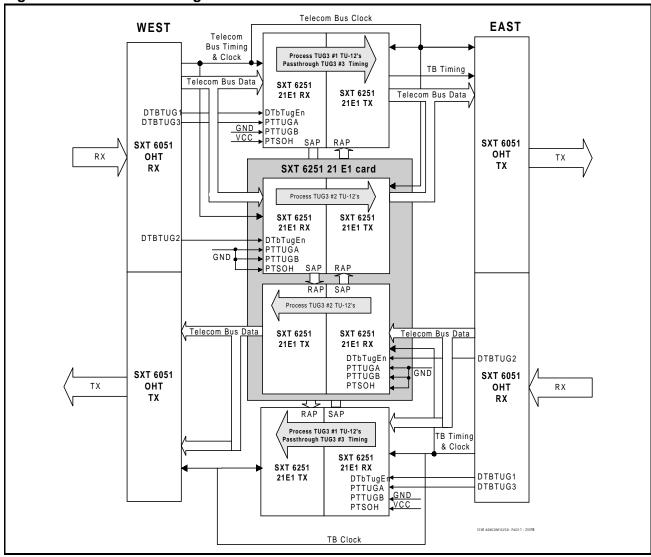

The SXT6051 Overhead Terminator implements the Regenerator Section Termination, Multiplexer Section Termination and Higher Order Path Termination in STM-0 (51Mb/s) and STM-1 (155mB/s) multiplexers. It provides micro-controller access for performance monitoring, alarm detection and configuration for transmit and receive paths. When used with the SXT6251 (21E1 Mapper), a complete solution for a 21 E1 or a 63 E1 Multiplexer is created.

The SXT6051 is compliant with the latest releases of ITU-T G.703 and G.707. It provides all the alarm and control features to easily implement the multiplexer described in ITU-T G.783.

## **Applications**

- SDH Terminal Mux/ADM for microwave radio

- ADM fiber ring Mux

- Digital Loop Carrier (NGDLC) Systems

- Digital Cross-Connect System

#### **Features**

- Performs Regenerator Section, Multiplexer Section, and Higher Order Path Overhead Processing for STM-1 and STM-0 signals.

- Byte parallel interface for STM-1 or STM-0, with byte alignment performed internally. Serial NRZ or B3ZS interface option for STM-0.

- Demultiplexes STM-0/STM-1 signals to Telecom Bus output with optional pointer processor re-timing.

- Multiplexes Telecom Bus data into STM-0 or STM-1 signals with pointer processing.

- Compatible with 1+1 protected ITU architecture.

- Records all RSOH, MSOH, and HPOH alarms. One second counters for B1, B2, B3, M1 REI and G1 REI.

- Full J0/J1 trace identifier processing

- Serial access to STM-1 user-defined, media-dependent and national bytes.

- Dedicated pins for serial access or pass-through feature for E1, E2, F1, F2, F3, D1-D3 & D4-D12 bytes.

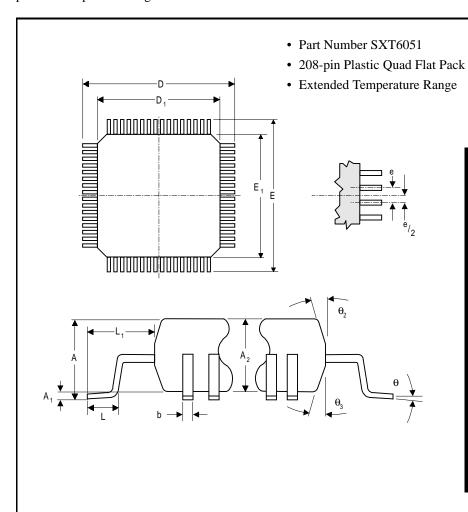

- Low power CMOS technology with 3.3V core and 5V I/O in PQFP-208 package.

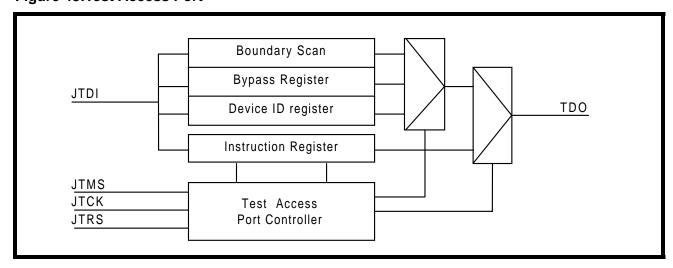

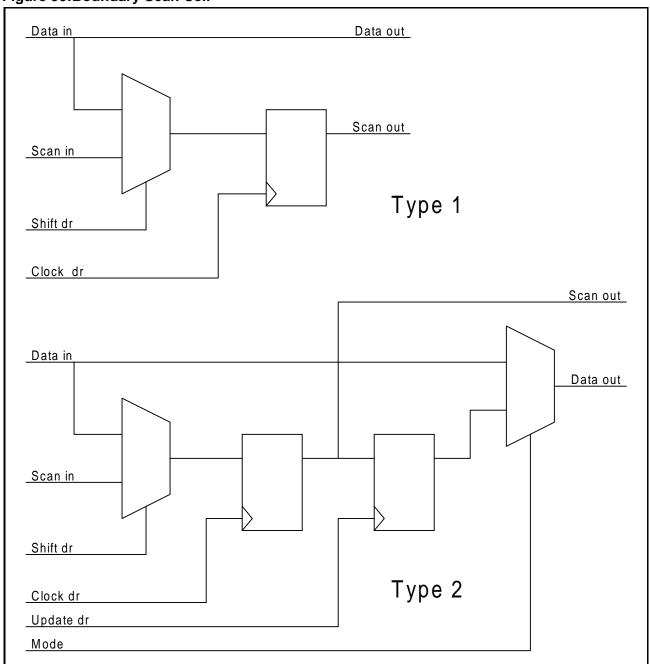

- IEEE 1149.1 Boundary Scan (JTAG) support.

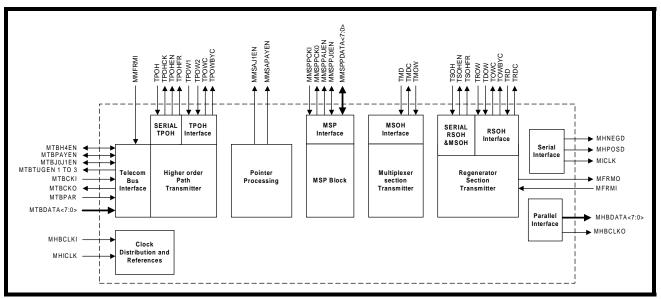

## SXT6051 System Block Diagram

## **Table Of Contents**

| In Assignments And Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

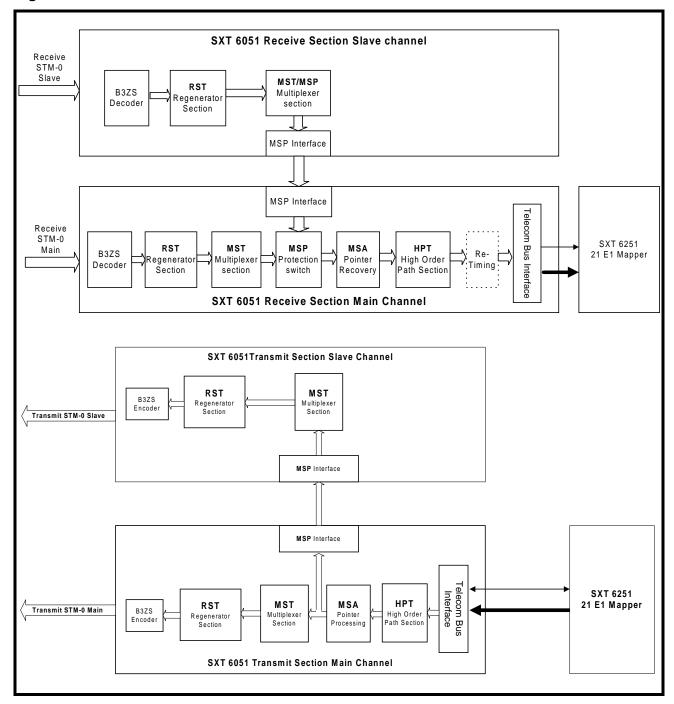

| Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                                                                                                         |

| Transmit Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18                                                                                                                         |

| Receive Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

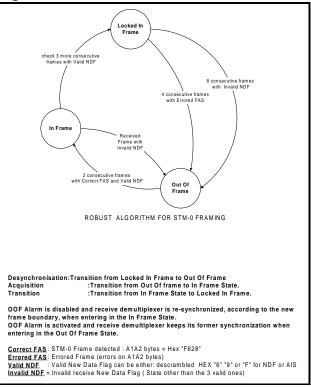

| Modes of Operation. Chip Configuration Repeater Mode Configuration (No Protection) Receive Side Telecom Bus Timing Source Transmit Side Telecom Bus Timing Source Add and Drop Configuration. Receive Side Telecom Bus Timing Source Add and Drop Configuration. Receive Side Telecom Bus Timing Source Transmit Side Telecom Bus Timing Source Updating the Transmit AU Pointer Justification Event Counters Terminal Protection Mode Receive Side Telecom Bus Timing Source Transmit Side Telecom Bus Timing Source Transmit Side Telecom Bus Timing Source Receiver Default Operation Serial Interface Parallel Interface Clock Distribution and Reference Framer Regenerator Section Receiver Multiplexer Section Receiver Multiplexer Section Protection (MSP) Block Pointer Recovery Higher Order Path Receiver Re-Timing Function. Transmitter Default Operation Higher Order Path Transmitter Transmit Pointer Processing Function Transmit Pointer Processing Function Transmit Multiplex Section Protection (MSP Block) Multiplexer Section Transmitter | 21<br>22<br>22<br>22<br>22<br>22<br>23<br>24<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25 |

| Regenerator Section Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 38                                                                                                                         |

| Serial Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 38                                                                                                                         |

| Functional Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 42                                                                                                                         |

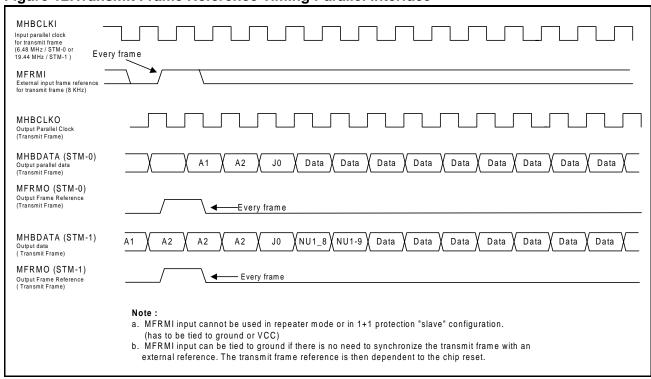

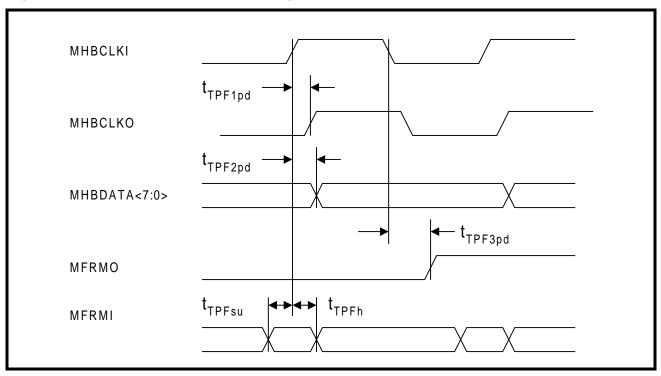

| Transmit Frame Parallel Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                         |

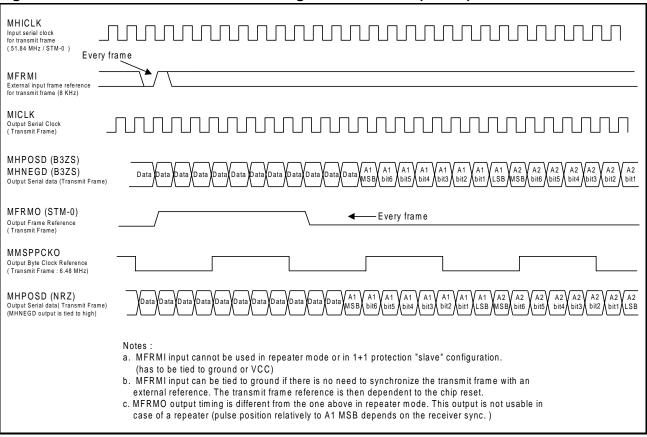

| ransmit Frame Serial Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Re-timing Functional Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

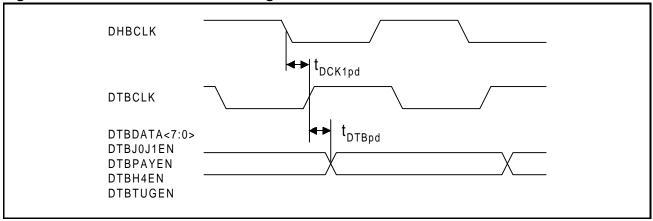

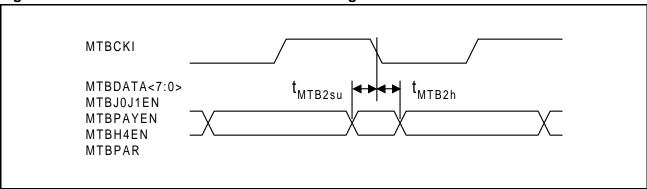

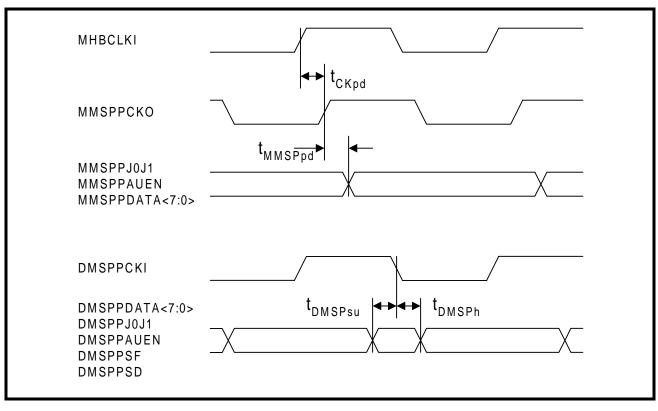

| Telecom Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

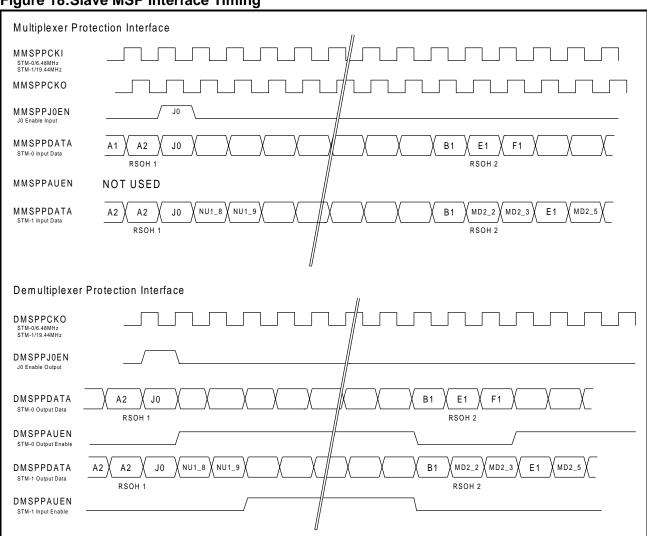

| Protection Bus Interface Timing.  Transmitter "Master" in 1+1 Protection Configuration  Transmitter "Slave" in 1+1 Protection Configuration  Receive"Master" in 1+1 Protection Configuration  Receive "Slave" Configuration (1+1 Protection).                                                                                                                                                                                                                                                                                                                                                                                      | 51<br>51<br>52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

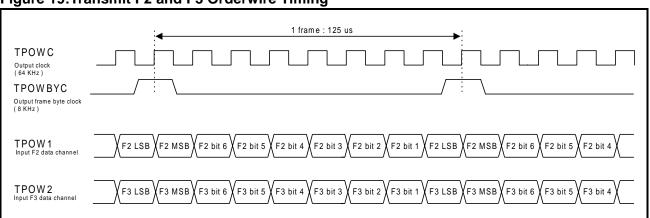

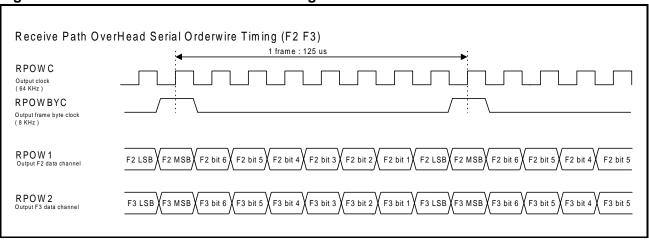

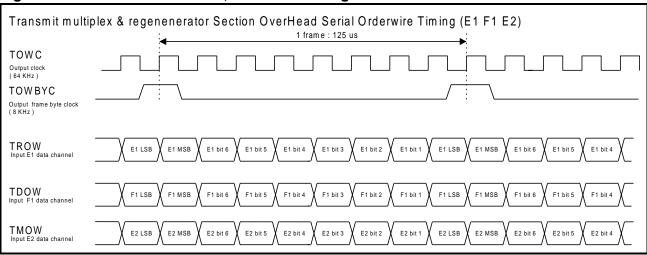

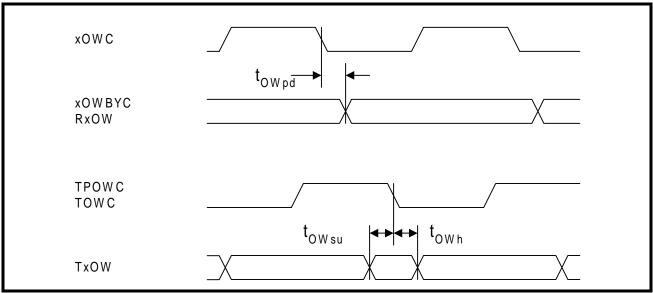

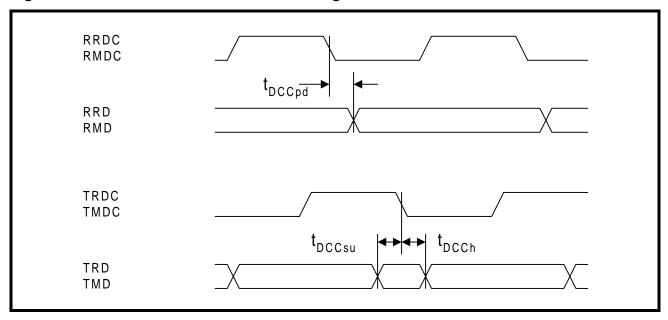

| DverHead Byte Access Timing F2 and F3 Digital Channel Functional Timing Transmit side access Receive side access E1, E2 and F1 Orderwire Channel Functional Timing Transmit Timing. Receive timing. HPOH Bytes Serial Access Functional Timing. Transmit serial HPOH Timing Receive Serial HPOH Timing SOH Overhead Access Functional Timing. Transmit Side SOH Serial Timing Receive Side SOH Serial Timing D1 to D3 Data Communication Channel Functional Timing. Transmit Side Access Receive Side Access D4 to D12 Data Communication Channel Transmit Side Access Receive Side Access Receive Side Access Receive Side Access | 555<br>565<br>565<br>575<br>575<br>575<br>575<br>575<br>575<br>575                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| processor Interface & Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

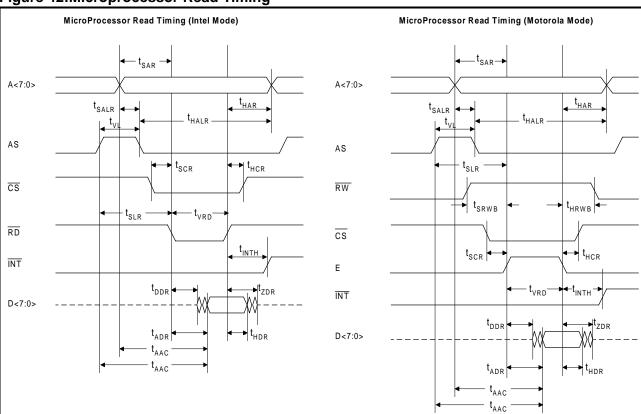

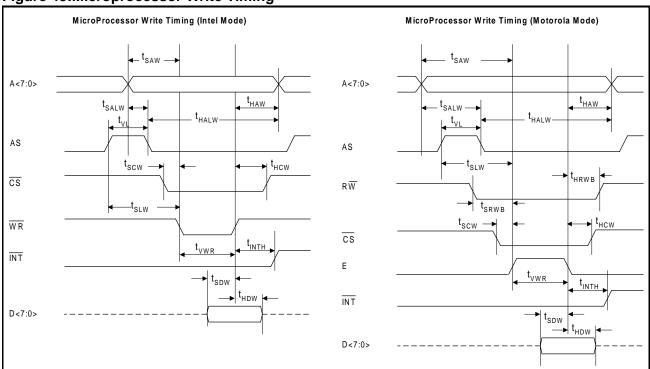

| Alicrocontroller Interface Intel interface Motorola interface Interrupt Handling. Interrupt Sources. Interrupt Enables Interrupt Clearing. Status Registers Access C2, K3, K2, K1 and S1 Receive Byte Registers Access                                                                                                                                                                                                                                                                                                                                                                                                             | 82<br>82<br>82<br>82<br>83<br>83<br>83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | elecom Bus Interface.  Multiplexer Telecom Bus Terminal Mode. Multiplexer Telecom Bus ADM Mode. Demultiplexer Telecom Bus (Terminal or ADM) Mode. Trotection Bus Interface Timing. Transmitter "Master" in 1+1 Protection Configuration Transmitter "Slave" in 1+1 Protection Configuration Receive "Master" in 1+1 Protection Configuration Receive "Slave" Configuration (1+1 Protection)  AverHead Byte Access Timing F2 and F3 Digital Channel Functional Timing Transmit side access. Receive iside access. E1, E2 and F1 Orderwire Channel Functional Timing Transmit Timing. Receive timing. HPOH Bytes Serial Access Functional Timing. Transmit serial HPOH Timing SOH Overhead Access Functional Timing. Transmit Side SOH Serial Timing Receive Side SOH Serial Timing D1 to D3 Data Communication Channel Functional Timing. Transmit Side Access. D4 to D12 Data Communication Channel Transmit Side Access Receive Side Access Receive Functional Timing  Processor Interface & Register Description  Interrupt Clearing Interrupt Enables Interrupt Clearing Status Registers Access. |

## SXT6051 STM-1/0 SDH Overhead Terminator

| Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 84                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Global Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 89<br>. 90                                                                           |

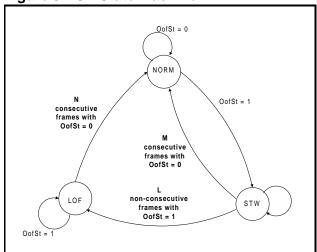

| Receive Regenerator Section Termination Registers  R_RSTC1—Receive RST Configuration 1 (40H).  R_RSTC2—Receive RST Configuration 2 (47H).  LOF_LMN—Loss of Frame L, M, & N Configuration (41–42H)  OOF_ECNT—Out Of Frame Event Counter (44–43H)  B1_ERRCNT—B1 Error Counter (46–45H).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 92<br>. 93<br>. 93<br>. 94                                                           |

| Receive Regenerator and Multiplexer Section Termination Registers  J0_RSTR_C—J0 Expected String Control (0EH)  J0_RSTR_D—J0 Expected String Data (0FH)  WINSZ_SB2—Window Size for Setting ExcB2ErrSt (1C–1BH)  CWIN_SB2—Consecutive Windows for Setting ExcB2ErrSt (1DH)  E#_EXCWIN—Number of Errs/Win for Excessively Errored Window (1EH)  WINSZ_C2—Window Size for Clearing ExcB2ErrSt (16–15H)  CWIN_CB2—Consecutive Windows for Clearing ExcB2ErrSt (17H)  E#_NEXCWIN—Number of Errs/Win for Non-Excessively Errored Window (18H)  B2_BLKCNT—B2 Block Error Counter (11–10H)  B2_BIPCNT—B2 BIP Error Counter (14–12H)  MR_BLKCNT—MST REI Block Error Counter (0A–09H)  MR_BIPCNT—MST REI BIP Error Counter (0D–0BH)  R_K1—Received K1 byte (00H)  R_K2—Received K2 Byte (01H)  R_S1—Received S1 byte (02H)  R_NU1_8—Received Nu1_8 byte (03H)  R_NU1_9—Received Nu2_8 byte (05H)  R_NU2_8—Received Nu2_9 byte (06H)  R_NU9_8—Received Nu9_9 byte (06H)  R_NU9_9—Received Nu9_9 byte (08H) | 95<br>96<br>96<br>96<br>97<br>97<br>97<br>97<br>97<br>98<br>98<br>98<br>98<br>98<br>99 |

| Receive Multiplexer Section Protection Registers  R_MSP_C—Receive MSP Configuration (20H)  R_MSP_OP—Receive MSP Operational (21H).  R_PROTK1—Received K1 byte on Protection Bus from Slave (22H).  R_PROTK2—Received K2 byte on Protection Bus from Slave (23H).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 100<br>100<br>101                                                                      |

| Receive Multiplexer Section Adaptation Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101<br>102                                                                             |

| Receive HighOrder Path Termination Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 103                                                                                    |

| R_HPT_C1—Receive HPT Configuration 1 Register (80H) R_HPT_C2—Receive HPT Configuration 2 Register (81H)  J1_RSTR_C—J1 Expected String Control Register (8AH)  J1_RSTR_D—J1 Expected String Data Register (8BH)  EXP_C2—Expected C2 byte Register (82H)  R_C2—Received C2 byte Register (83H)  R_K3—Received K3 byte Register (84H)  R_HPT_RDI—Received HPT RDI Bits Register (85H)  B3_ECNT—B3 Error Event Counter (87–86H)  HPTREI_CNT—HPT REI Counter (89–88H) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transmit Regenerator and Multiplexer Section Termination Registers. 10 T_RMST_OP1—Transmit RMST Operational 1 Register (30H)                                                                                                                                                                                                                                                                                                                                     |

| Transmit Multiplexer Section Adaptation Registers                                                                                                                                                                                                                                                                                                                                                                                                                |

| Transmit HighOrder Path Termination Registers. 17  T_SC_HPOH—Transmit Source Configuration for HPOH bytes (70H) 11  T_HPT_C—Transmit HPT Configuration (71H) 12  MP_TC2—Microprocessor Provided Transmit C2 Byte (72H) 12  MP_TK3—Microprocessor Provided Transmit K3 Byte (73H) 12  J1_TSTR_C—J1 Transmit String Control (75H) 12  J1_TSTR_D—J1 Transmit String Data (76H) 12                                                                                   |

| Interrupt Source Registers                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## SXT6051 STM-1/0 SDH Overhead Terminator

| IS_RETIME—Receive Retiming Interrupt Source (A6H)                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 124                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Interrupt Enable Registers  IE_RG—Receive Regenerator Section Interrupt Enable (B0H)  IE_RGMUX—Receive Regenerator and Multiplexer Section Interrupt Enable (B1H)  IE_MUX—Receive Multiplexor Section Interrupt Enable (B2H)  IE_PROT—Receive Protection Section Interrupt Enable (B3H)  IE_A_HPT—Receive Adaptation and HPT Interrupt Enable (B4H)  IE_HPT—Receive HPT Interrupt Enable (B5H)  IE_RETIME—Receive Retiming Interrupt Enable (B6H)  IE_XMT—Transmit Interrupt Enable (E1H) | 126<br>126<br>126<br>126<br>126<br>126    |

| Status Registers  S_RG—Receive Regenerator Section Status (C0H).  S_RGMUX—Receive Regenerator and Multiplexer Section Status (C1H).  S_PROT—Receive Protection Section Status (C3H).  S_A_HPT—Receive Adaptation and HPT Status (C4H).  S_HPT—Receive HPT Status (C5H).  S_AIS_PROT—Receive AIS & Protection Switch Status (D0H).                                                                                                                                                         | . 127<br>. 127<br>. 128<br>. 128<br>. 129 |

| Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 131                                       |

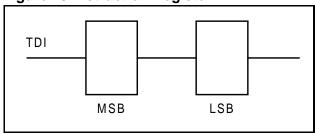

| IEEE 1149.1 Boundary Scan Instruction Register and Definitions Boundary Scan Register Summary Information                                                                                                                                                                                                                                                                                                                                                                                 | . 132<br>. 132                            |

| Package Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140                                       |

| Glossary of terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 141                                       |

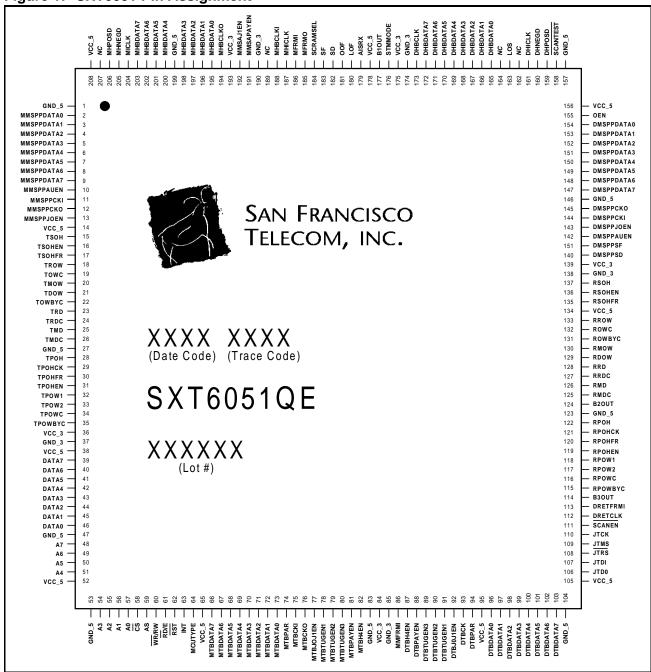

## PIN ASSIGNMENTS AND SIGNAL DESCRIPTION

Figure 1: SXT6051 Pin Assignment

**Table 1: Signal Description Nomenclature**

| Туре               | Description               |  |  |  |

|--------------------|---------------------------|--|--|--|

| I                  | Standard input signal     |  |  |  |

| 0                  | Standard output signal    |  |  |  |

| I/O                | Input and output signal   |  |  |  |

| TTLin <sup>1</sup> | Supports TTL input levels |  |  |  |

| HiZ <sup>1</sup>   | High Impedance            |  |  |  |

$<sup>1. \ \</sup> Out \ and \ I/O \ signals \ indicate \ buffer \ strength. \ For example, HiZ-4ma \ indicates \ a \ high-impedance \ buffer \ capable \ of sourcing 4 ma.$

Table 2: Signal Description (Sheet 1 of 11)

|                                                 | able 2: Signal Description (Sheet 1 of 11) |                |                                                                                                                                                             |  |  |  |

|-------------------------------------------------|--------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin#                                            | Name                                       | Туре           | Description                                                                                                                                                 |  |  |  |

|                                                 | STM-0 Transmit/ Receive Serial Format      |                |                                                                                                                                                             |  |  |  |

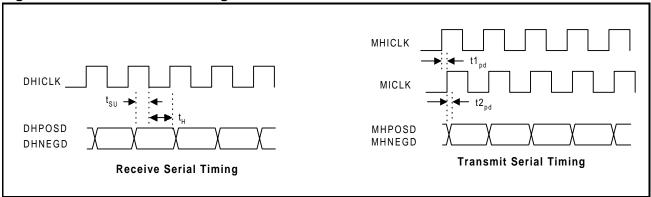

| 159                                             | DHPOSD                                     | I<br>TTLin     | <b>Positive B3ZS or NRZ Data Receive</b> . Input for STM-0 data at 51.84 Mbit/s supplied by the STM-0 line interface unit.                                  |  |  |  |

| 160                                             | DHNEGD                                     | I<br>TTLin     | Negative B3ZS Data Receive. Input for STM-0 data at 51.84 Mbit/s when B3ZS coding is used.                                                                  |  |  |  |

| 161                                             | DHICLK                                     | I<br>TTLin     | <b>Serial Data Clock Input</b> . Receive STM-0 clock at 51.84 MHz provided by the external STM-0 line interface unit.                                       |  |  |  |

| 206                                             | MHPOSD                                     | O<br>HiZ-8ma   | <b>Positive B3ZS or NRZ Data Transmit</b> . Output of STM-0 data at 51.84 Mbit/s; either NRZ or B3ZS                                                        |  |  |  |

| 205                                             | MHNEGD                                     | O<br>HiZ-8ma   | Negative B3ZS Data Transmit. Output of STM-0 data at 51.84 Mbit/s when B3ZS coding is used.                                                                 |  |  |  |

| 204                                             | MICLK                                      | O<br>HiZ-8ma   | <b>Serial Data Clock Output</b> . The serial output clock of the multiplexer. This signal is to be used with the serial data MHPOSD and MHNEGD when needed. |  |  |  |

|                                                 | ST                                         | M1/STM-0 Trans | mit Receive Parallel Format                                                                                                                                 |  |  |  |

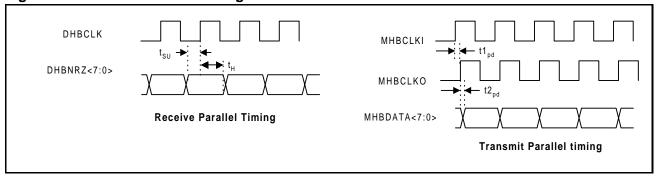

| 172, 171,<br>170, 169,<br>168, 167,<br>166, 165 | DHBDATA<7:0>                               | I<br>TTLin     | Parallel NRZ Data Receive. Parallel input data in STM-1 or STM-0 mode.                                                                                      |  |  |  |

| 173                                             | DHBCLK                                     | I<br>TTLin     | <b>Parallel Data Clock Input</b> . Parallel input data clock at either 19.44 MHz for STM-1 or 6.48 MHz for STM-0                                            |  |  |  |

| 203, 202,<br>201, 200,<br>198, 197,<br>196, 195 | MHBDATA<7:0>                               | O<br>HiZ-4ma   | Parallel NRZ Data Transmit. Parallel output data in STM-1 or STM-0 mode.                                                                                    |  |  |  |

| 194                                             | MHBCLKO                                    | O<br>HiZ-8ma   | <b>Parallel Data Clock Output.</b> Parallel output data clock at either 19.44 MHz for STM-1 or 6.48 MHz for STM-0.                                          |  |  |  |

Table 2: Signal Description (Sheet 2 of 11)

| Pin# | Name                        | Туре         | Description                                                                                                                                                                                                                                              |  |  |  |

|------|-----------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|      | External References         |              |                                                                                                                                                                                                                                                          |  |  |  |

| 185  | MFRMO                       | O<br>HiZ-4ma | <b>Internal TX Frame Alignment Output</b> . This signal is synchronous with the multiplexer frame and is used to synchronize other transmitters. See Figures 12 and 13.                                                                                  |  |  |  |

| 186  | MFRMI                       | I<br>TTLin   | <b>External TX Frame Alignment Input.</b> An 8 KHz signal used to align the start of a transmit multiplexer frame. If not needed, this input is grounded.                                                                                                |  |  |  |

| 163  | LOS                         | I<br>TTLin   | Loss of Signal Input. Input from the Line Interface circuit that can be used either with a parallel interface or with a serial interface. Active High.                                                                                                   |  |  |  |

| 187  | MHICLK                      | I<br>TTLin   | Multiplexer System Serial Clock. An external STM-0 (51.84 MHz) reference frequency input for the multiplexer and can be used by the demultiplexer section during Blue Signal /AIS Signal generation.                                                     |  |  |  |

| 188  | MHBCLKI                     | I<br>TTLin   | Multiplexer System Parallel Clock. An external STM-0 (6.48 MHz) or STM-1 (19.44 MHz) reference frequency input for the multiplexer and can be used by the demultiplexer section during Blue Signal /AIS Signal generation.                               |  |  |  |

| 86   | MMFRMI                      | I<br>TTLin   | <b>External Multiframe Alignment</b> . A 2 KHz input signal (25% duty cycle) that can be used, in terminal mode only, to reset the internal H4 byte counter.                                                                                             |  |  |  |

| 192  | MMSAJ1EN                    | O<br>HiZ-2ma | <b>Test Point For J1 Position</b> on TX framed signal. Provided for testing purposes.                                                                                                                                                                    |  |  |  |

| 191  | MMSAPAYEN                   | O<br>HiZ-2mA | <b>Test point for Payload Enable</b> on TX framed signal. Provided for testing purposes.                                                                                                                                                                 |  |  |  |

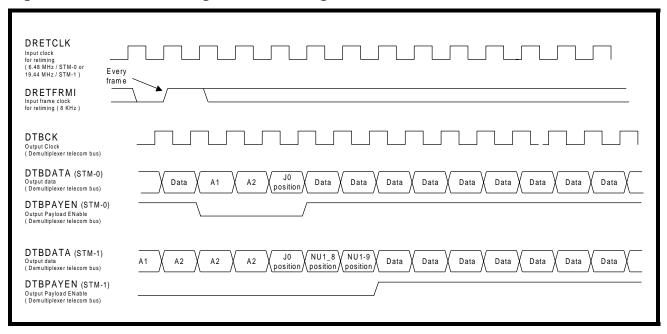

| 113  | DRETFRMI                    | I<br>TTLin   | <b>Demultiplexer Receive Re-timing Frame</b> . An 8 KHz pulse synchronous with DRETCLK, used by the receive re-timing function to synchronize the position of the VC3 or VC4 payload. It is always needed.                                               |  |  |  |

| 112  | DRETCLK                     | I<br>TTLin   | Demultiplexer Receive Re-timing Clock Synchronization. A parallel clock input at either 6.48 MHz (STM-0) or 19.44 MHz (STM-1). It is used to generate the clocking for the VC-3 or VC-4 container on DTBDATA<7:0> when the retiming function is enabled. |  |  |  |

|      | Serial Overhead Byte Access |              |                                                                                                                                                                                                                                                          |  |  |  |

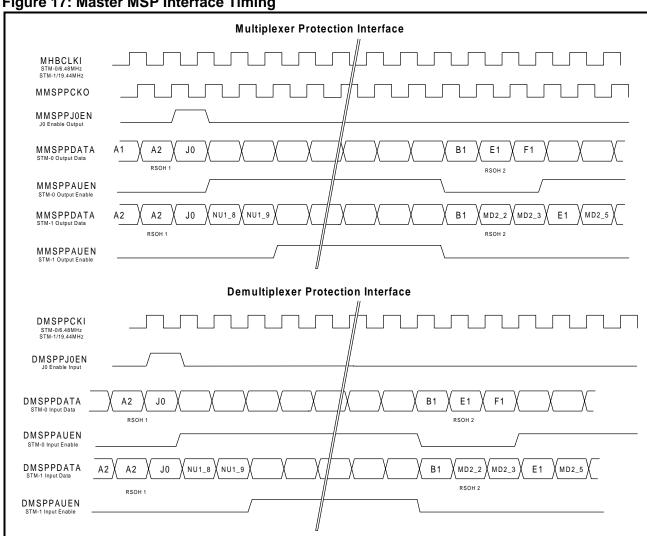

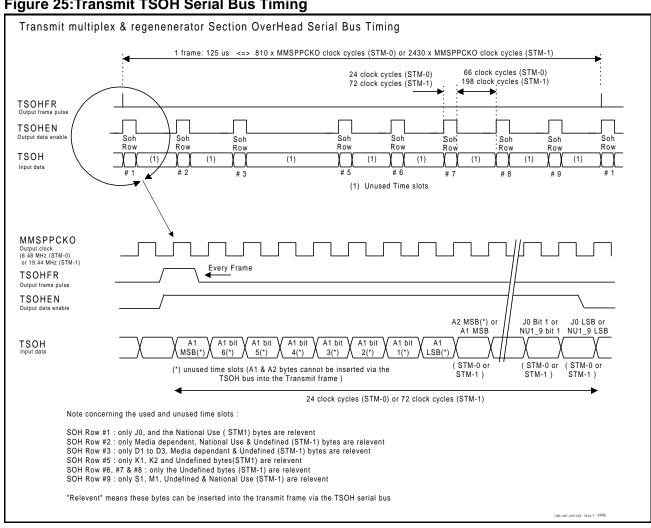

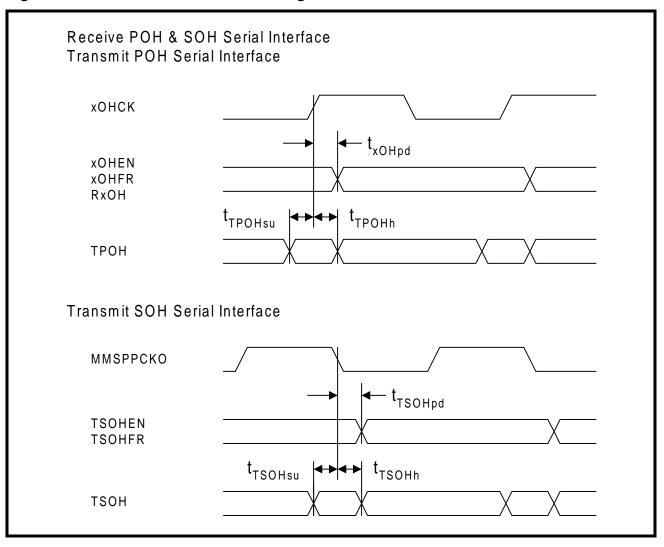

| 15   | ТЅОН                        | I<br>TTLin   | <b>Transmit RSOH and MSOH Serial Access.</b> Input for serially sourced RSOH and MSOH transmit data. The data is clocked in synchronous to MMSPPCKO at 19.44 MHz for STM-1 and 6.48 MHz for STM-0.                                                       |  |  |  |

| 16   | TSOHEN                      | O<br>HiZ-4ma | Transmit RSOH and MSOH Serial Access Clock Enable. Used to enable clocking of RSOH and MSOH data at the TSOH input using MMSPPCKO.                                                                                                                       |  |  |  |

Table 2: Signal Description (Sheet 3 of 11)

| Pin # | Name   | Туре         | Description                                                                                                                                                                                                                                    |

|-------|--------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17    | TSOHFR | O<br>HiZ-4ma | Transmit RSOH and MSOH Serial Access Frame Position. This is an 8 KHz synchronization pulse indicating the start (MSB of A1) of the 72 bytes of STM-1 RSOH/MSOH or 24 bytes of STM-0 RSOH/MSOH input at TSOH. It is synchronous with MMSPPCKO. |

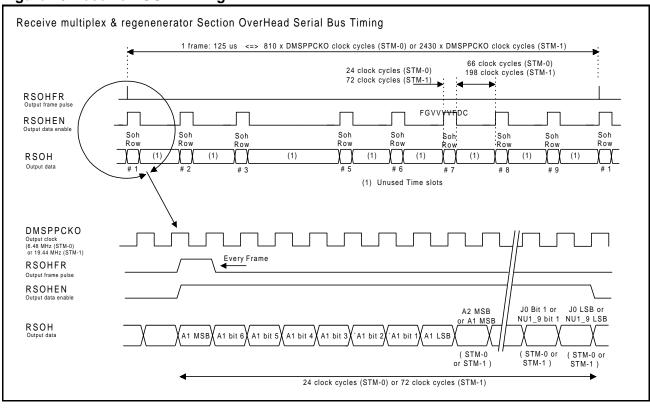

| 137   | RSOH   | O<br>HiZ-4ma | Receive RSOH and MSOH Serial Access. Serial output of received RSOH and MSOH data. The data is clocked out synchronous to DMSPPCKO at 19.44 MHz for STM-1 and 6.48 MHz for STM-0.                                                              |

| 136   | RSOHEN | O<br>HiZ-4ma | Receive RSOH and MSOH Serial Access Clock Enable. Used to enable clocking of RSOH and MSOH data at the RSOH output using DMSPPCKO.                                                                                                             |

| 135   | RSOHFR | O<br>HiZ-4ma | Receive RSOH and MSOH Serial Access Frame Position. This is an 8 KHz synchronization pulse indicating the start (MSB of A1) of the 72 bytes of STM-1 RSOH/MSOH or 24 bytes of STM-0 RSOH/MSOH output at RSOH. It is synchronous with DMSPPCKO. |

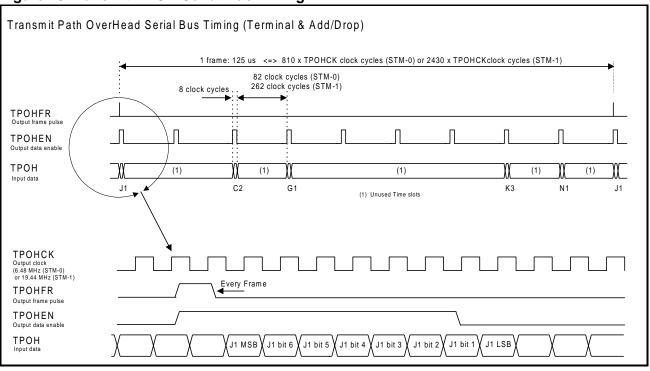

| 28    | ТРОН   | I<br>TTLin   | <b>Transmit HPOH Serial Access.</b> Input for serially sourced HPOH transmit data.                                                                                                                                                             |

| 29    | ТРОНСК | O<br>HiZ-4ma | <b>Transmit HPOH Serial Access Clock.</b> Used to clock in the TPOH data at 19.44 clock for STM-1 or 6.48 MHz for STM-0.                                                                                                                       |

| 31    | TPOHEN | O<br>HiZ-4ma | <b>Transmit HPOH Serial Access Clock Enable</b> . Used to enable TPOHCK clocking of TPOH input data.                                                                                                                                           |

| 30    | TPOHFR | O<br>HiZ-4ma | <b>Transmit HPOH Serial Access Frame Position.</b> This is an 8 KHz synchronization pulse indicating the start (MSB of J1) of the 9 bytes of HPOH input at TPOH. It is synchronous with TPOHCK.                                                |

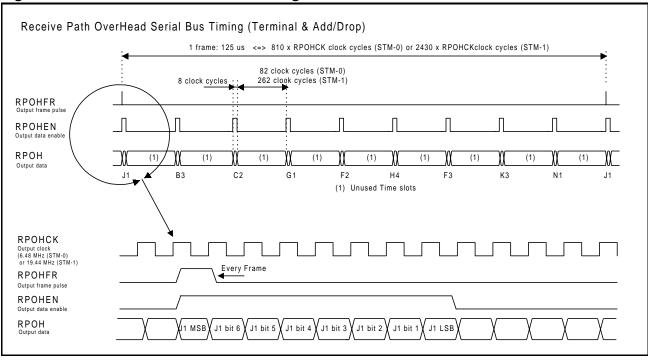

| 122   | RPOH   | O<br>HiZ-4ma | Receive HPOH Serial Access. Serial output of received HPOH data.                                                                                                                                                                               |

| 121   | RPOHCK | O<br>HiZ-4ma | <b>Receive HPOH Serial Access Clock.</b> Used to clock out the RPOH data at 19.44 clock for STM-1 or 6.48 MHz for STM-0.                                                                                                                       |

| 119   | RPOHEN | O<br>HiZ-4ma | Receive HPOH Serial Access Clock Enable. Used to enable RPOHCK clocking of received RPOH data.                                                                                                                                                 |

| 120   | RPOHFR | O<br>HiZ-4ma | Receive HPOH Serial Access Frame Position. This is an 8 KHz synchronization pulse indicating the start (MSB of J1) of the 9 bytes of HPOH input at RPOH. It is synchronous with RPOHCK.                                                        |

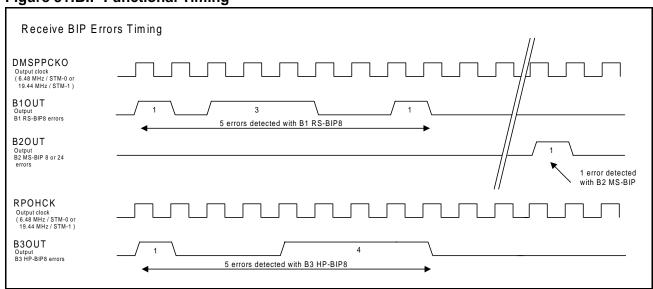

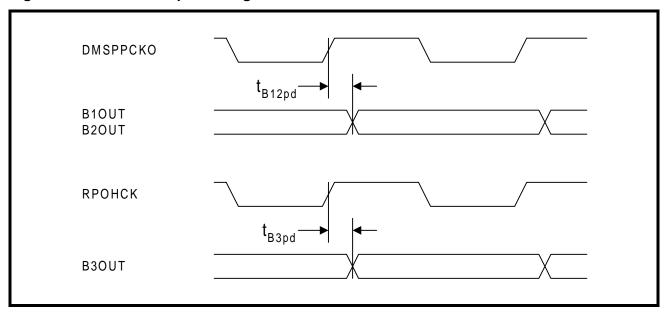

| 177   | BIOUT  | O<br>HiZ-2ma | <b>B1</b> Error Output (BIP). This pin goes High when an error is detected by the regenerator section overhead. It is synchronous to DMSPPCK0.                                                                                                 |

| 124   | B2OUT  | O<br>HiZ-2ma | <b>B2 Error Output (BIP)</b> This pin goes High when an error is detected by the terminal section overhead. It is synchronous to DMSPPCK0                                                                                                      |

Table 2: Signal Description (Sheet 4 of 11)

| Pin # | Name  | Туре    | Description                                                              |

|-------|-------|---------|--------------------------------------------------------------------------|

| 114   | B3OUT | 0       | <b>B3</b> Error Output (BIP) This pin goes High when an error is         |

|       |       | HiZ-2ma | detected by the higher order path overhead. It is synchronous to RPOHCK. |

Table 2: Signal Description (Sheet 5 of 11)

| Pin #                            | Name     | Туре              | Description                                                                                                                                   |  |  |

|----------------------------------|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configuration & Alarm Monitoring |          |                   |                                                                                                                                               |  |  |

| 181                              | OOF      | O<br>HiZ-2ma      | <b>Out of Frame Indicator</b> . Active High when framer enters in an out of frame state. Minimum pulse width is 125 us (1 frame).             |  |  |

| 180                              | LOF      | O<br>HiZ-2ma      | <b>Loss of Frame Indicator</b> . Active High when the framer enters a loss of frame state. Minimum pulse width is 125 us (1 frame).           |  |  |

| 182                              | SD       | O<br>HiZ-2ma      | <b>Signal Degrade.</b> State of register 21H<br>bit 1> bit value.                                                                             |  |  |

| 183                              | SF       | O<br>HiZ-2ma      | <b>Signal Fail.</b> State of register C1H<br>bit 5> bit value.                                                                                |  |  |

| 179                              | AISRX    | O<br>HiZ-2ma      | <b>Receive AIS Signal Indicator</b> . Indicates that an AIS has been detected in the received VC3 or VC4. Active High.                        |  |  |

| 184                              | SCRAMSEL | I<br>TTLin        | <b>Scrambler Disable</b> . This pin should be tied to Low during normal operation. Active High.                                               |  |  |

| 176                              | STMMODE  | I<br>TTLin        | Mode Select. Low selects STM-0, High selects an STM-1.                                                                                        |  |  |

|                                  | (        | Orderwire and Dat | a Byte Access Transmit Side                                                                                                                   |  |  |

| 18                               | TROW     | I<br>TTLin        | <b>Transmit RSOH E1 Orderwire.</b> A 64 Kb/s data input for orderwire byte E1. Data is synchronized with TOWBYC and clocked by TOWC.          |  |  |

| 19                               | TOWC     | O<br>HiZ-2ma      | <b>Transmit RSOH and MSOH Orderwire Clock.</b> A reference clock output at 64 KHz to be used for transmit E1, E2 and F1 byte clocking.        |  |  |

| 20                               | TMOW     | I<br>TTLin        | <b>Transmit MSOH E2 Orderwire.</b> A 64 Kb/s data input for orderwire byte E2. Data is synchronized with TOWBYC and clocked by TOWC.          |  |  |

| 21                               | TDOW     | I<br>TTLin        | <b>Transmit RSOH F1 Orderwire.</b> A 64 Kb/s data input for orderwire byte F1. Data is synchronized with TOWBYC and clocked by TOWC.          |  |  |

| 22                               | TOWBYC   | O<br>HiZ-2ma      | Transmit RSOH and MSOH Orderwire Synchronization Signal. An 8 KHz signal used to byte synchronize the transmitted E1, F1 and E2 data streams. |  |  |

| 32                               | TPOW1    | I<br>TTLin        | <b>Transmit HPOH F2 Orderwire.</b> A 64 Kb/s data input for orderwire byte F2. Data is synchronized with TPOWBYC and clocked by TPOWC.        |  |  |

| 33                               | TPOW2    | I<br>TTLin        | <b>Transmit HPOH F3 Orderwire.</b> A 64 Kb/s data input for orderwire byte F3 Data is synchronized with TPOWBYC and clocked by TPOWC.         |  |  |

| 34                               | TPOWC    | O<br>HiZ-2ma      | <b>Transmit HPOH Orderwire Clock.</b> A reference clock output at 64 KHz to be used for F2 and F3 transmit byte clocking.                     |  |  |

Table 2: Signal Description (Sheet 6 of 11)

| Table 2. O | ignal Description (S | ineer o or rry  |                                                                                                                                                |

|------------|----------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin #      | Name                 | Туре            | Description                                                                                                                                    |

| 35         | TPOWBYC              | O<br>HiZ-2ma    | <b>Transmit HPOH Orderwire Synchronization Signal.</b> An 8 KHz signal used to byte synchronize the F2 and F3 transmit data streams.           |

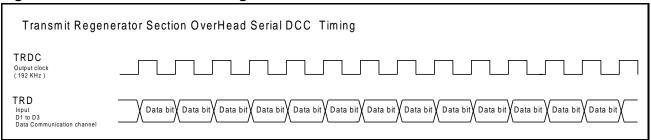

| 23         | TRD                  | I<br>TTLin      | <b>Transmit RSOH D1-D3 Data.</b> A 192 Kb/s data input for RSOH D1-D3 data. Data is clocked in by TRDC.                                        |

| 24         | TRDC                 | O<br>HiZ-2ma    | <b>Transmit RSOH D1-D3 Data Clock.</b> A 192 KHz reference signal used to clock in TRD data.                                                   |

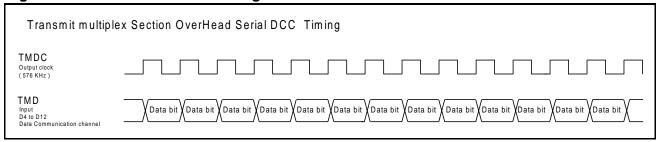

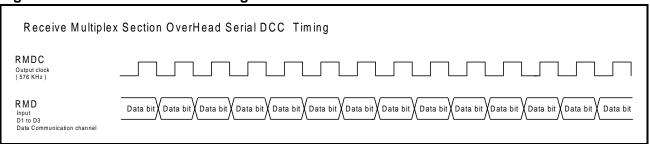

| 25         | TMD                  | I<br>TTLin      | <b>Transmit MSOH D4-D12 Data.</b> A 576 Kb/s data input for MSOH D4-D12 data. Data is clocked in by TMDC.                                      |

| 26         | TMDC                 | O<br>HiZ-2ma    | <b>Transmit MSOH D4-D12 Data Clock.</b> A 576 KHz reference signal used to clock in TMD data.                                                  |

|            | Ord                  | erwire and Data | Byte Access Receive Side                                                                                                                       |

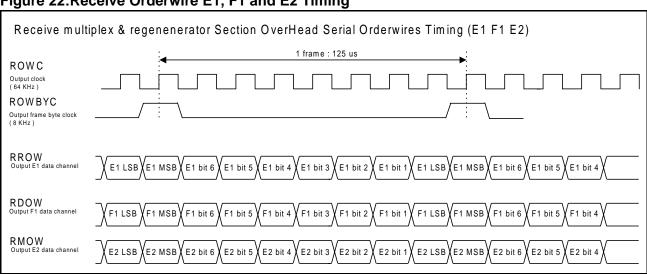

| 133        | RROW                 | O<br>HiZ-2ma    | Receive RSOH E1 Orderwire. A 64 Kb/s data output for received orderwire byte E1. Data is synchronized with ROWBYC and clocked by ROWC.         |

| 132        | ROWC                 | O<br>HiZ-2ma    | <b>Receive RSOH and MSOH Orderwire Clock.</b> A reference clock output at 64 KHz to be used for receive E1, E2 and F1 byte clocking.           |

| 131        | ROWBYC               | O<br>HiZ-2ma    | Receive RSOH and MSOH Orderwire Synchronization Signal. An 8 KHz signal used to byte synchronize the received E1, E2 and F1data streams.       |

| 130        | RMOW                 | O<br>HiZ-2ma    | Receive MSOH E2 Orderwire. A 64 Kb/s data output for received orderwire byte E2. Data is synchronized with ROWYC and clocked by ROWC.          |

| 129        | RDOW                 | O<br>HiZ-2ma    | <b>Receive MSOH F1 Orderwire.</b> A 64 Kb/s data output for received orderwire byte F1. Data is synchronized with ROW-BYC and clocked by ROWC. |

| 118        | RPOW1                | O<br>HiZ-2ma    | Receive HPOH F2 Orderwire. A 64 Kb/s data output for received orderwire byte F2. Data is synchronized with RPOWBYC and clocked by RPOWC        |

| 117        | RPOW2                | O<br>HiZ-2ma    | Receive HPOH F3 Orderwire. A 64 Kb/s data output for received orderwire byte F3. Data is synchronized with RPOWBYC and clocked by RPOWC        |

| 116        | RPOWC                | O<br>HiZ-2ma    | <b>Receive HPOH Orderwire Clock.</b> A reference clock output at 64 KHz to be used for F2 and F3 receive byte clocking.                        |

| 115        | RPOWBYC              | O<br>HiZ-2ma    | <b>Receive HPOH Orderwire Synchronization Signal.</b> An 8 KHz signal used to byte synchronize the F2 and F3 receive data streams.             |

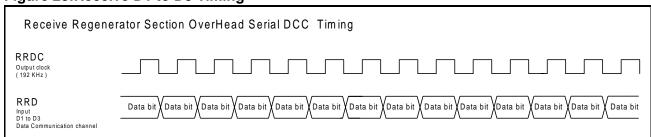

| 128        | RRD                  | O<br>HiZ-2ma    | Receive RSOH D1-D3 Data. A 192 Kb/s data output for RSOH D1-D3 data. Data is clocked out by RRDC.                                              |

| 127        | RRDC                 | O<br>HiZ-2ma    | <b>Receive RSOH D1-D3 Data Clock.</b> A 192 KHz reference signal used to clock out RRD data.                                                   |

Table 2: Signal Description (Sheet 7 of 11)

| Pin #                                | Name                  | Туре             | Description                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------------------------|-----------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 126                                  | RMD                   | O<br>HiZ-2ma     | <b>Receive MSOH D4-D12 Data.</b> A 576 Kb/s data output for MSOH D4-D12 data. Data is clocked out by RMDC.                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 125                                  | RMDC                  | O<br>HiZ-2ma     | <b>Receive MSOH D4-D12 Data Clock.</b> A 576 KHz reference signal used to clock out RMD data.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

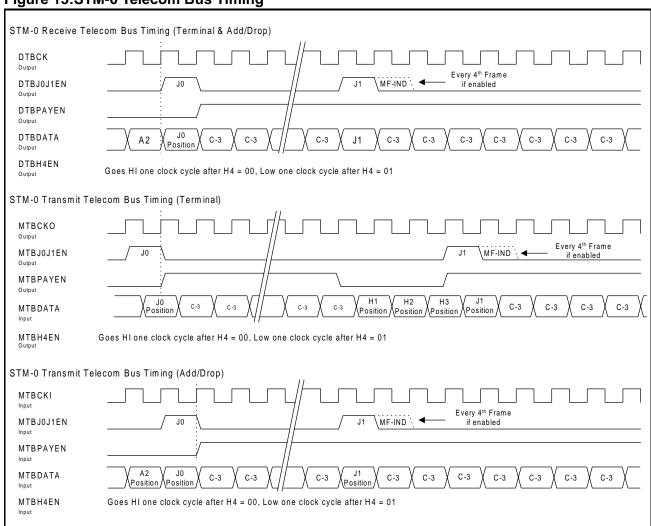

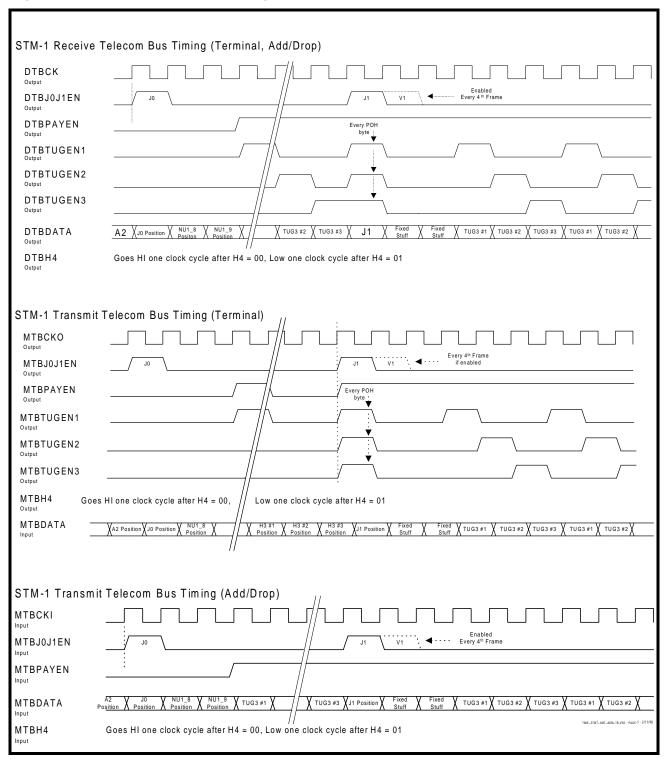

|                                      | Telecom Bus Interface |                  |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 66, 67, 68,<br>69, 70, 71,<br>72, 73 | MTBDATA<7:0>          | I<br>TTLin       | Multiplexer Telecom Bus Data. A byte-wide data input at 19.44 Mbit/s for STM-1 or 6.48 Mbit/s for STM-0. Non-payload byte timeslots (i.e., RSOH, AU pointer, MSOH and HPOH timeslots) can either have a 0 or 1 inserted.                                                                                                                         |  |  |  |  |  |  |

| 74                                   | MTBPAR                | I<br>TTLin       | <b>Multiplexer Telecom Bus Parity</b> . This is a parity check calculated on each MTBDATA<7:0> byte. It is an odd parity.                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 75                                   | MTBCKI                | I<br>TTLin       | Multiplexer Telecom Bus Clock Input. A 6.48MHz (STM-0) or 19.44 MHz (STM-1) input signal used to clock MTB-DATA<7:0>. It is used when the SXT6051 is configured as an ADM. In other configurations the pin should be tied to ground.                                                                                                             |  |  |  |  |  |  |

| 76                                   | МТВСКО                | O<br>HiZ-8ma     | Multiplexer Telecom Bus Clock Output. A 6.48MHz (STM-0) or 19.44 MHz (STM-1) output signal. It is used when the SXT6051 is used in a Terminal configuration.                                                                                                                                                                                     |  |  |  |  |  |  |

| 77                                   | MTBJ0J1EN             | I/O<br>TTLin-4ma | Multiplexer Telecom Bus Frame Indicator. It indicates the presence of J0 and J1 bytes on the transmit bus. In an ADM configuration the pin is set up as an input while in the terminal mode it is set up as an output.                                                                                                                           |  |  |  |  |  |  |

| 78                                   | MTBTUGEN1             | O<br>HiZ-4ma     | Multiplexer Telecom Bus Payload Enable 1. Indicates the presence of TUG3#1 in the case of STM-1. In the case of STM-0 this pin is internally pulled High. In ADM it is not used.                                                                                                                                                                 |  |  |  |  |  |  |

| 79                                   | MTBTUGEN2             | O<br>HiZ-4ma     | Multiplexer Telecom Bus Payload Enable 2. Indicates the presence of TUG3#2 in the case of STM-1. In the case of STM-0 this pin is internally pulled High. In ADM it is not used.                                                                                                                                                                 |  |  |  |  |  |  |

| 80                                   | MTBTUGEN3             | O<br>HiZ-4ma     | Multiplexer Telecom Bus Payload Enable 3. Indicates the presence of TUG3#3 in the case of STM-1. In the case of STM-0 this pin is internally pulled High. In ADM it is not used.                                                                                                                                                                 |  |  |  |  |  |  |

| 81                                   | MTBPAYEN              | I/O<br>TTLin-4ma | Multiplexer Telecom Bus Payload Enable Signal. Indicates the presence of VC-4 in the STM-1 mode or VC-3 in the STM-0 mode. This signal is used as an output when the SXT6051 is configured in a Terminal mode and an input in ADM mode.                                                                                                          |  |  |  |  |  |  |

| 82                                   | MTBH4EN               | TTLin-4ma        | Multiplexer Telecom Bus H4 Multi-Frame Indicator. As an output, it is a 2 KHz signal that indicates the location of the 00 value of H4. The signal goes High after H4 equals "00" and Low after H4 equals" 01". Used as an output when the SXT6051 is configured in a Terminal Mode. As an input (in ADM) it is sampled at the J1 byte location. |  |  |  |  |  |  |

Table 2: Signal Description (Sheet 8 of 11)

| Pin #                                       | Name           | Туре             | Description                                                                                                                                                                                                                                                        |