# MASTER/SLAVE T FLIP-FLOP

UPG701B UPG701P

#### **FEATURES**

- LOGIC LEVELS AND SUPPLY VOLTAGES ARE ECL COMPATIBLE

- ULTRA HIGH SPEED (Operating Clock Frequency-5 GHz)

- HERMETICALLY SEALED PACKAGE ASSURES HIGH RELIABILITY

#### **DESCRIPTION AND APPLICATIONS**

The UPG701B is a high speed GaAs digital integrated circuit. It is a Master-Slave T-type Flip Flop that operates with Set/Reset functions. When the clock input is High, the output is changed. When the clock input is Low, the output state remains unchanged. Its operating clock speed is 5 GHz typically. It is ECL compatible both in I/O levels and supply voltages. The 16-pin ceramic package is low loss and hermetically sealed. Devices are highly reliable because of the stability of WSi refractory gate metallization. This device is compatible with other NEC MSI and SSI GaAs logic products, and can be tested using a MD16EVAL 16-pin evaluation kit.

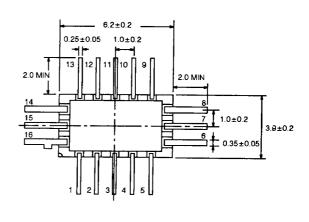

#### **OUTLINE DIMENSIONS** (Units in mm)

#### **OUTLINE H16**

# **ELECTRICAL CHARACTERISTICS** (TA = 25°C)

| PART NUMBER PACKAGE OUTLINE |                           |                                                                              |       | UPG701B, UPG701P<br>H16, CHIP |      |              |

|-----------------------------|---------------------------|------------------------------------------------------------------------------|-------|-------------------------------|------|--------------|

| SYMBOLS                     | PARAMETERS                | TEST CONDITIONS                                                              | UNITS | MIN                           | TYP  | MAX          |

| loo                         | Supply Current            |                                                                              | mA    |                               | 80   | 130          |

| Iss                         | Supply Current            | $V$ DD = 0 V $V$ TT = -2 V $(50 \Omega \text{ termination})$ $V$ ss = -5.2 V | mA    |                               | 60   | 90           |

| Vон                         | High Level Output Voltage |                                                                              | V     | -1.0                          | -0.8 | -0.6         |

| Vol                         | Low Level Output Voltage  |                                                                              | V     | -2.0                          | -1.8 | -1.6         |

| Vтн                         | Threshold Voltage         |                                                                              | V     |                               | -1.3 |              |

| Іон                         | High Level Output Current |                                                                              | mA    |                               | 25   | <del> </del> |

| loL                         | Low Level Output Current  |                                                                              | mA    |                               | 4    |              |

| liн                         | High Level Input Current  |                                                                              | mA    |                               | .75  |              |

| lic .                       | Low Level Input Current   |                                                                              | mA    |                               | .05  |              |

| fфмах                       | Maximum Clock Frequency   |                                                                              | GHz   | 4                             | 5    |              |

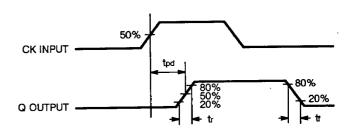

| tPO                         | Switching Time            |                                                                              | ps    |                               | 300  | 400          |

| tr*                         | Output Rise Time          |                                                                              | ps    | ·····-                        | 130  | 200          |

| tr*                         | Output Fall Time          |                                                                              | ps    |                               | 120  | 200          |

Notes: \*The time from 20% to 80% of output voltage.

- The Vcs and VcsB are normally open. They can also be used as a bias adjustment to optimize operating frequency or output waveform.

The Vcs and VcsB are bias terminals which are used to adjust the Flip Flop circuit current and output level respectively.

- 2. The metallized section on the back surface of the package is used as a heat sink and is shared with Vss terminal (Vss = -5.2 V normally). Note: Do not ground the metallized section to GND (0 V). This is to prevent a short circuit with VDD or some other terminals.

# ABSOLUTE MAXIMUM RATINGS (TA = 25°C)

| SYMBOLS | PARAMETERS                 | UNITS | RATINGS         |

|---------|----------------------------|-------|-----------------|

| VDD     | Supply Voltage             | ٧     | +4              |

| Vss     | Supply Voltage             | ٧     | -8              |

| Vп      | Terminating Voltage        | ٧     | - <b>V</b> DD-4 |

| Vin     | Input Voltage              | ٧     | VDD - Vss       |

| Тѕта    | Storage Temperature        | °C    | -65 to +175     |

| Tc(OP)  | Operating Case Temperature | ۰c    | -65 to +125     |

| Рт      | Total Power Dissipation    | mW    | 550             |

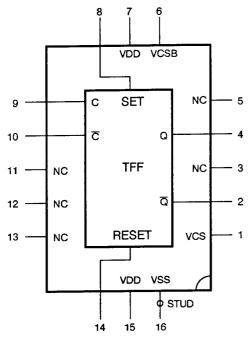

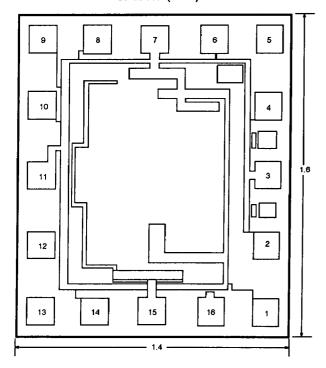

## **CONNECTION DIAGRAM**

#### HANDLING PROCEDURE

When handling the device a ground strap should be used to prevent Electric Static Discharge (ESD) that can damage the GaAs MES FETs in the IC.

### **TRUTH TABLE**

| THOTH TABLE |      |       |           |           |  |

|-------------|------|-------|-----------|-----------|--|

| INPUT       |      |       | OUTPUT    |           |  |

| CLOCK       | SET  | RESET | Qn + 1    | Qn + 1    |  |

|             | LOW  | LOW   | Qn        | Qn        |  |

|             | LOW  | LOW   | Qn        | Qn        |  |

| UNRELATED   | HIGH | LOW   | HIGH      | LOW       |  |

| UNRELATED   | LOW  | HIGH  | LOW       | HIGH      |  |

| UNRELATED   | HIGH | HIGH  | UNCERTAIN | UNCERTAIN |  |

#### Notes:

- Set and reset functions are fully synchronous with respect to clock.

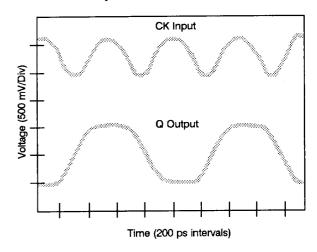

#### **OPERATIONAL WAVEFORMS**

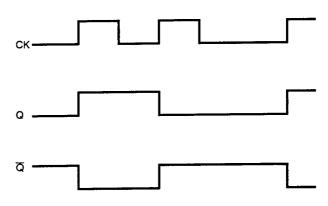

#### **FUNCTION DIAGRAM**

$Q_N + 1 = \overline{Q}_N$

QN + 1; The output after the clock pulse

QN: The output before the clock pulse

When the clock input is HIgh, the output state is changed.

When the clock input is Low, the output state remains unchanged.

# **UPG701B WAVEFORM (2.0 GHz CLOCK FREQUENCY)**

# **OUTLINE DIMENSIONS (Units in mm)**

#### UPG701P (CHIP)

| ٠. | *03 |  |

|----|-----|--|

| 2. | Q   |  |

| 3. | NC  |  |

| 4  | _   |  |

1 Vcs

9. <u>CK</u> 10. CK 11. NC 12. NC 4. Q 5. NC 13. NC 14. Reset

6. Vcsa 7. VDD

15. VDD 8. Set 16. Vss

#### RECOMMENDED CHIP ASSEMBLY CONDITIONS

Die Attachment

Atmosphere: Temperature: AuSn Preform:

N<sub>2</sub> gas 320 ± 3°C UPG701P

0.7 x 0.7 x 0.05<sup>t</sup> (mm), 2 piece

The use of hard solder (AuSi or AuGe) is not recommended. Don't use a solder which has a melting point higher than

AuSn.

Base material: CuW, Cu, KV

Epoxy Die Attach is not recommended.

Bonding:

TCB 30 µm diameter Au wire 260 ± 10°C 44 ± 5g Nz gas

Machine: Wire: Temperature: Bonding Force: Atmosphere: