# **Pulse Detector**

## **GENERAL DESCRIPTION**

The ML8464 is a Pulse Detector designed for use in magnetic disk applications to detect the amplitude peaks on the output of the read/write amplifier. These signal peaks are caused by flux reversal on the disk media, which when connected to the read/write amplifier result in an output consisting of a series of pulses of alternating polarity. The relative time position of these signal peaks is indicated by the leading edge of the TTL output pulses. The Pulse Detector accurately represents the time position of these peaks.

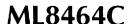

The ML8464 contains three major blocks. The amplifier block contains a wide bandwidth differential amplifier with Automatic Gain Control (AGC) and a precision full wave rectifier. The time channel block includes a programmable differentiator followed by a bidirectional one shot. The gate channel block includes a differential comparator with programmable hysteresis, a D flip-flop and an output bi-directional one shot multivibrator. The ML8464C internally connects the time channel output to the D flip-flop.

#### **FEATURES**

- Wide differential input signal range 20-600mV<sub>P-P</sub>

- TTL compatible digital inputs and output

- Externally gain controlled input differential amplifier

- Variable hysteresis comparator with gating circuitry

- Differentiator with externally programmable time constants

- Standard 12V power requirement

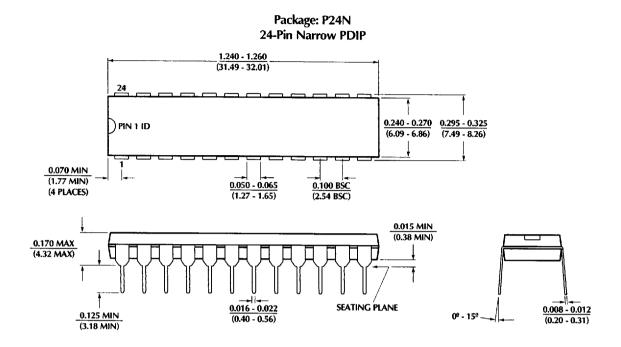

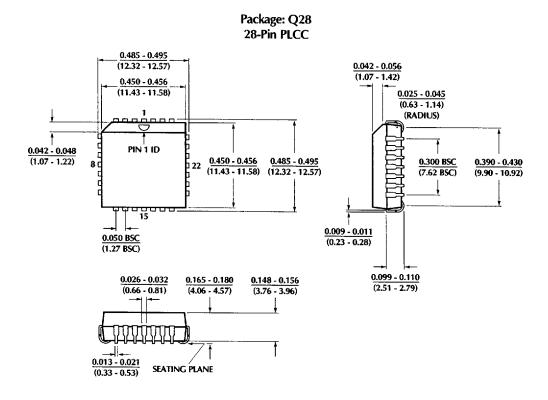

- Available in 24-pin DIP package, or a 28-pin surface mount PCC

- Improved pulse pairing (±1ns max.)

- Handles RLL (1, 7) or (2, 7) data to 24MB

#### **BLOCK DIAGRAM**

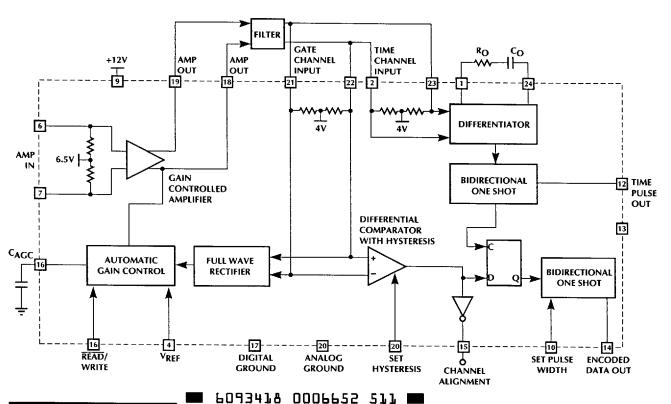

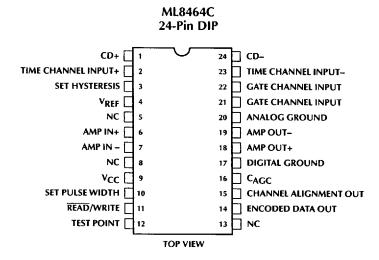

# **PIN CONFIGURATIONS**

# PIN DESCRIPTION

| NAME                                             | FUNCTION                                                                                                                                                         | NAME                 | FUNCTION                                                                                                                |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------|

| AMP IN+/<br>AMP IN-                              | Differential inputs to the amplifier. The output of the read/write head amplifier should be capacitively coupled to these pins.                                  | C <sub>AGC</sub>     | External capacitor between this pin and analog ground is connected for the AGC.                                         |

| AMP OUT+/<br>AMP OUT-                            | Differential outputs of the amplifier. These outputs should be capacitively coupled to the gating channel filter and to the time channel filter.                 | SET PULSE<br>WIDTH   | External capacitor between this pin and digital ground is connected to control the pulse width of the Encoded Data Out. |

| GATE CHANNEL<br>INPUTS                           | Differential inputs to the AGC block<br>and the gating channel. Must be<br>capacitively coupled from the AMP                                                     | READ/WRITE           | TTL input. When low, the chip is read mode and active. When high, the chip is forced into stand by mode.                |

|                                                  | OUT.                                                                                                                                                             | CHANNEL<br>ALIGNMENT | Buffered output of the differential comparator with hysteresis. This                                                    |

| TIME CHANNEL<br>INPUT+/TIME<br>CHANNEL<br>INPUT- | Differential inputs to the time channel differentiator. A filter is required between these pins and AMP OUT pins to band limit the noise and to                  | ALIGINIMEINT         | output is open emitter on ML8464C. The ML8464C is specified with a $2k\Omega$ pull-down resistor to ground.             |

|                                                  | correct for any phase distortion due to read circuitry. Also inputs must be                                                                                      | TEST POINT           | Open emitter-follower test point.                                                                                       |

|                                                  | capacitively coupled to prevent disturbing the DC input level.                                                                                                   | ENCODED<br>DATA OUT  | TTL output. Leading edge of this pin indicates the time position of the peaks.                                          |

| CD+, CD-                                         | External differentiator network is connected between these two pins.                                                                                             | V                    | ·                                                                                                                       |

|                                                  | connected between these two pins.                                                                                                                                | $V_{CC}$             | 12V power supply.                                                                                                       |

| SET HYSTERESIS                                   | DC voltage on this pin sets the amount of hysteresis on the differential comparator.                                                                             | GND                  | Digital ground. Digital signals should be referenced to this pin.                                                       |

| $V_{REF}$                                        | AGC circuit adjusts the gain of the amplifier to make the differential peak to peak voltage on the Gate Channel. Input is four times the DC voltage on this pin. | AGND                 | Analog ground. Analog signals should be referenced to this pin.                                                         |

# **ML8464C**

### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.  $\theta_{JA}$  for 24-Pin Plastic DIP (Copper Lead Frame) 60°C/Watt  $\theta_{JA}$  for 28-Pin PLCC (Copper Lead Frame) ....... 60°C/Watt Storage Temperature Range ...... –65°C to 150°C

| Supply Voltage             | 14V  |

|----------------------------|------|

| TTL Input Voltage          | 5.5V |

| TTL Output Voltage         | 5.5V |

| Input Voltage              | 5 5V |

| Differential Input Voltage | 3V   |

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions of  $T_A = 0$  to  $70^{\circ}$ C,  $V_{CC} = 12V \pm 10\%$ ,  $V_{REF} = 0.5V$ , SET HYSTERESIS = 0.3V, READ/WRITE = 0.8V unless otherwise noted. (All pin numbers refer to DIP package.)

| SYMBOL             | PARAMETER                                                  | CONDITIONS                                           | MIN  | TYP                                                  | MAX                                          | UNITS       |

|--------------------|------------------------------------------------------------|------------------------------------------------------|------|------------------------------------------------------|----------------------------------------------|-------------|

| AMPLIFII           | ER                                                         |                                                      |      | · <del>L</del> · · · · · · · · · · · · · · · · · · · | <u>.                                    </u> | <del></del> |

| Z <sub>INAi</sub>  | Amp In Impedance                                           |                                                      | 0.8  | 1.0                                                  | 1.5                                          | kΩ          |

| A <sub>VMIN</sub>  | Min Voltage Gain                                           | AC Output 4V <sub>P-P</sub> Differential             |      | <u>.                                    </u>         | 6.0                                          | V/V         |

| A <sub>VMAX</sub>  | Min Voltage Gain                                           | AC Output 4V <sub>P-P</sub> Differential             | 180  |                                                      |                                              | V/V         |

| $V_{CAGC}$         | Voltage on C <sub>AGC</sub>                                | A <sub>V</sub> = 6.0                                 |      | 4.5                                                  | 5.5                                          | V           |

|                    |                                                            | $A_V = 180$                                          | 2.8  | 3.4                                                  |                                              | V           |

| GATE CH            | IANNEL                                                     |                                                      |      |                                                      | ·                                            | L.,         |

| Z <sub>INGCI</sub> | Gate Channel Input Impedance                               |                                                      | 1.75 | 2.5                                                  | 3.25                                         | kΩ          |

| I <sub>CAGC</sub>  | Current That Charges C <sub>AGC</sub>                      | Pin 16 = 3.9V,<br>Pin 21 – Pin 22 = 1.3V             | -1.5 | -2.5                                                 | -3.5                                         | m           |

| I <sub>CAGC+</sub> | Current That Discharges C <sub>AGC</sub>                   | Pin 16 = 5.0V,<br>Pin 21 – Pin 22 = 0.7V             |      | 1                                                    | 5                                            | μА          |

| I <sub>VREF</sub>  | V <sub>REF</sub> Input Bias Current                        |                                                      |      | -0.01                                                | -10                                          | μА          |

| $V_{THAGC}$        | AGC Threshold                                              | Pin 16 = 4.2V (Note 1)                               | 0.88 | 1.0                                                  | 1.12                                         | V           |

| I <sub>SH</sub>    | Set Hysteresis Bias Current                                |                                                      |      | -60                                                  | -100                                         | μА          |

| V <sub>THSH</sub>  | Set Hysteresis Threshold                                   | (Note 2)                                             | 0.48 | 0.6                                                  | 0.72                                         | V           |

| TIME CH            | ANNEL                                                      |                                                      |      |                                                      |                                              | <u> </u>    |

| Z <sub>INTC</sub>  | Time Channel Input Impedance                               |                                                      | 3.5  | 5                                                    | 6.5                                          | kΩ          |

| I <sub>CD</sub>    | Current Into Pins 1 & 24 That<br>Discharges C <sub>D</sub> |                                                      | 2.1  | 2.7                                                  | 3.4                                          | mA          |

| WRITE M            | ODE                                                        |                                                      |      | 1                                                    |                                              | 1           |

| Z <sub>INAI</sub>  | Amplifier Input Impedance In<br>Write Mode                 | Pin 11 = 2V                                          | 100  |                                                      | 500                                          | Ω           |

| I <sub>CAGC</sub>  | Pin 16 Current In Write Mode                               | Pin 11 = 2V, Pin 16 = 3.9V<br>Pin 21 – Pin 22 = 1.3V |      | 1.0                                                  | 5.0                                          | μА          |

# DC ELECTRICAL CHARACTERISTICS (Continued)

| SYMBOL            | PARAMETER                              | CONDITIONS                                                        | MIN      | TYP      | MAX      | UNITS |

|-------------------|----------------------------------------|-------------------------------------------------------------------|----------|----------|----------|-------|

| DIGITAL           | PINS                                   |                                                                   | <u> </u> | <u> </u> | <u> </u> | 1     |

| V <sub>IH</sub>   | High Level Input Voltage               | Pin 11                                                            | 2.0      |          |          | V     |

| $V_{IL}$          | Low Level Input Voltage                | Pin 11                                                            |          |          | 0.8      |       |

| VI                | Input Clamp Voltage                    | V <sub>CC</sub> = 10.8V, I <sub>I</sub> = –18mA                   |          |          | -1.5     | V     |

| l <sub>IH</sub>   | High Level Input Current               | V <sub>CC</sub> = 13.2V, V <sub>i</sub> = 2.7V                    |          |          | 20       | μΑ    |

| l <sub>l</sub>    | Input Current at Maximum Input Voltage | $V_{CC} = 13.2V, V_{I} = 5.5V$                                    |          |          | 1        | mA    |

| I <sub>IL</sub>   | Low Level Input Current                | V <sub>CC</sub> = 13.2V, V <sub>I</sub> = 0.5V                    |          | -        | -200     | μА    |

| V <sub>OH</sub>   | High Level Output Voltage              | V <sub>CC</sub> = 10.8V, V <sub>IOH</sub> = -40μA<br>(Notes 3, 7) | 2.4      |          |          | V     |

| V <sub>OL</sub>   | Low Level Output Voltage               | V <sub>CC</sub> = 10.8V, I <sub>OL</sub> = 800μA (Note 7)         |          |          | 0.5      | V     |

| l <sub>OSC</sub>  | Output Short Circuit Current           | $V_{CC} = 13.2V, V_{O} = 0V$                                      |          |          | -100     | mA    |

| Icc               | Supply Current                         | V <sub>CC</sub> = 13.2V                                           |          | 54       | 75       | m     |

| $V_{OHCA}$        | Channel Alignment Pin V <sub>OH</sub>  | 10kΩ Load to GND (Note 3)                                         |          | 7.6      | <u> </u> | V     |

| $V_{OLCA}$        | Channel Alignment Pin V <sub>OL</sub>  | 10kΩ Load to GND (Note 3)                                         |          | 6.9      |          | V     |

| V <sub>OHTP</sub> | Test Point Out Pin V <sub>OH</sub>     | 10kΩ Load to GND                                                  |          | 9.6      |          | V     |

| VOLTP             | Test Point Out Pin V <sub>OL</sub>     | 10kΩ Load to GND                                                  |          | 8.6      |          | V     |

# **AC ELECTRICAL CHARACTERISTICS**

Over recommended operating temperature and supply range of  $V_{CC} = 10.8$  to 13.2V,  $T_A = 0$  to 70°C.

| SYMBOL           | PARAMETER                            | CONDITIONS                                                  | MIN | TYP  | MAX  | UNITS |

|------------------|--------------------------------------|-------------------------------------------------------------|-----|------|------|-------|

| t <sub>P-P</sub> | ML8464-1<br>Pulse Pairing            | f = 2.5MHz                                                  |     | ±0.5 | ±1.0 | ns    |

| t <sub>P-P</sub> | ML8464-1.5<br>Pulse Pairing (Note 6) | $V_{IN} = 40 \text{mV}_{P-P} \text{ differential}$ (Note 4) |     | ±0.8 | ±1.5 | ns    |

| tp_p             | ML8464-2<br>Pulse Pairing            | ,                                                           |     | ±1.5 | ±3.0 | ns    |

Note 1: The AGC threshold is defined as the voltage across the GATE CHANNEL INPUT when the voltage on CAGC is 4.2V.

Note 2: The SET HYSTERESIS threshold is defined as the voltage across the GATE CHANNEL INPUT when the channel alignment output voltage changes state.

Note 3: To prevent inductive coupling from the digital outputs to amplifier inputs, the TTL outputs should not drive more than one ALS TTL load.

Note 4: The filter and differentiator network are described in the pulse pairing set-up.

Note 5: All limits are guaranteed by 100% testing or alternate methods.

Note 6: The 1.5ns pulse pairing specification is available only on the ML8464C, not the ML8464B.

Note 7: ML8464C: Pins 14 and 15 only.

### **FUNCTIONAL DESCRIPTION**

The output from the read/write amplifier is AC coupled to the amp input of the ML8464. The amplifier's output voltage is fed back via an external filter to an internal fullwave rectifier and compared against the external voltage on the  $V_{REF}$  pin. The AGC circuit adjusts the gain of the amplifier to make the peak to peak differential voltage on the GATE CHANNEL INPUT four times the DC voltage on the  $V_{REF}$ . Typically the signal on the amp out will be set for  $4V_{P-P}$  differential. Since the filter usually has a 6dB loss, the signal on the GATE CHANNEL INPUT will be  $2V_{P-P}$  differential. The user should therefore set 0.5V on  $V_{REF}$  which can be done with a simple voltage divider from the +12V supply or other suitable reference.

The peak detection is performed by feeding the output of the amplifier through an external filter to the differentiator. The differentiator output changes state when the input pulse changes direction, generally this will be at the peaks. However, if the signal exhibits shouldering, the differentiator will also respond to noise near the baseline. To avoid this problem, the signal is also fed to a gating channel which is used to define a level either side of the baseline. This gating channel is comprised of a differential comparator with hysteresis and a D flip-flop. The hysteresis for this comparator is externally set via the SET HYSTERESIS pin. In order to have data out, the input amplitude must first cross the hysteresis level which will

change the logic level on the D input of the flip-flop. The peak of the input signal will generate a pulse out of the differentiator and bidirectional one shot. This pulse will clock the new data at the D input through to the output. In this way, when the differentiator is responding to noise at the baseline, the output of the D flip-flop is not changing since the logic level into the D input has not been changed. The comparator circuitry is therefore a gating channel which prevents any noise near the baseline from contaminating the data. The amount of hysteresis is twice the DC voltage on the SET HYSTERESIS pin. For instance, if the voltage on the SET HYSTERESIS pin is 0.3V, the differential AC signal across the gate channel input must be larger than 0.6V before the comparator will change states. In this case, the hysteresis is 30% of a 2V peak to peak differential signal at the gate channel input.

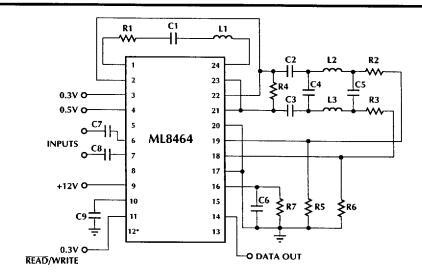

#### PULSE PAIRING MEASUREMENT

The scope probe is connected to Pin 14 (ENCODED DATA OUT) and triggered off of its positive edge. The trigger holdoff is adjusted so that the scope first triggers off the pulse associated with the positive peak and then off the pulse associated with the negative peak. Pulse pairing is displayed on the second pair of pulses on the display. If the second pair of pulses are separated by 6ns, then the pulse pairing for the part is ±3ns.

| R1     | 220 Ω  |

|--------|--------|

| R4     | 680 Ω  |

| R2, R3 | 240 Ω  |

| R5, R6 | 3.3kΩ  |

| R7     | 100k Ω |

| L1     | 1.5 μH |

| L2. L3 | 4.7 µH |

| C1         | 82nF |

|------------|------|

| C2, C3, C6 |      |

| C4         |      |

| C5         |      |

| C7, C8     |      |

| C9         |      |

Figure 1. Pulse Pairing Set Up

■ 6093418 0006657 OT3 **■**

#### THE EXTERNAL DELAY

The ML8464C has no TTL buffers at pins 12 and 13 and closes the signal path internally bringing out a test point at pin 12. Hence, the ML8464C does not allow for the external delay.

#### **TEST POINTS**

The ML8464C uses open emitter followers in an ECL configuration. Hence, the voltage levels are not similar at pins 12 and 15 on both devices. The typical voltage level at pin 12 are  $V_{OH}=9.6V$ ,  $V_{OL}=8.6V$  and at pin 15 are  $V_{OH}=1.6V$ ,  $V_{OL}=1.0V$

#### AGC GAIN CONTROL FACTOR

The AGC reference level is a DC voltage externally set at  $V_{REF}$  (pin 4). Increasing this DC voltage will increase the gain of the gain controlled amplifier.

AGC gain control factor =

$$\frac{V_{OUT\ PEAK}}{V_{REF}}$$

= peak of the AGC amp

AGC gain control factor =

$$\frac{2.0V_{P-P}}{0.5V_{DC}}$$

= 4 for ML8464C

Thus, at  $V_{REF} = 0.5 V_{DC}$ ,  $V_{OUT}$  AGC = 2.0V for ML8464C. This smaller signal amplitude should be taken into consideration at the hysteresis comparator. To set the desired amount of hysteresis, and external DC control voltage is used.

Figure 2.

PAGE(S) INTENTIONALLY BLANK

# PHYSICAL DIMENSIONS inches (millimeters)

### PHYSICAL DIMENSIONS inches (millimeters)

## **ORDERING INFORMATION**

| PART NUMBER    | TEMPERATURE RANGE | PACKAGE          | PULSE PAIRING |

|----------------|-------------------|------------------|---------------|

| ML8464C CP-1   | 0°C to 70°C       | Molded DIP (P24) | ±1ns          |

| ML8464C CQ-1   | 0°C to 70°C       | Molded PCC (Q28) | ±1ns          |

| ML8464C CP-1.5 | 0°C to 70°C       | Molded DIP (P24) | ±1.5ns        |

| ML8464C CQ-1.5 | 0°C to 70°C       | Molded PCC (Q28) | ±1.5ns        |

| ML8464C CP-2   | 0°C to 70°C       | Molded DIP (P24) | ±3ns          |

| ML8464C CQ-2   | 0°C to 70°C       | Molded PCC (O28) | ±3ns          |

© Micro Linear 1997 De Micro Linear is a registered trademark of Micro Linear Corporation

Products described herein may be covered by one or more of the following patents: 4,897,611; 4,964,026; 5,027,116; 5,281,862; 5,283,483; 5,418,502; 5,508,570; 5,510,727; 5,523,940; 5,546,017; 5,559,470; 5,565,761; 5,594,376. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200

Fax: 408/432-0295