Rev. V5

#### **Features**

- High Voltage CMOS Technology

- Four Channel

- Positive Voltage Control

- CMOS device using TTL input levels

- Low Power Dissipation

- Low Cost 4 mm, 20-lead PQFN Package

- 100% Matte Tin Plating over Copper

- Halogen-Free "Green" Mold Compound

- RoHS\* Compliant

### Description

The MADR-009443 is a four channel driver used to translate TTL control inputs into gate control voltages for GaAs FET microwave switches and attenuators. High speed analog CMOS technology is utilized to achieve low power dissipation at moderate to high speeds, encompassing most microwave switching applications. The output HIGH level is optionally 0 to 2 V (relative to GND) to optimize the intermodulation products of FET control devices at low frequencies. For driving PIN diode circuits, the outputs are nominally switched between +5 V & -5 V. The actual driver output voltages will be lower when driving large currents due to the resistance of the output devices.

# Ordering Information<sup>1</sup>

| Part Number        | Package               |

|--------------------|-----------------------|

| MADR-009443-000100 | Bulk Packaging        |

| MADR-009190-000DIE | 100 piece waffle pack |

| MADR-009443-0001TR | 1000 piece reel       |

<sup>1.</sup> Reference Application Note M513 for reel size information.

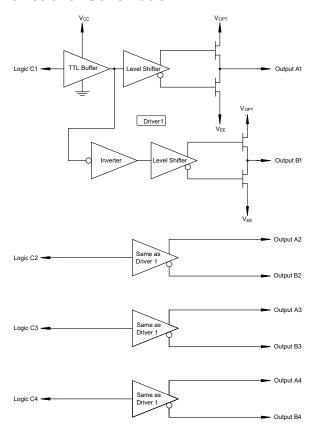

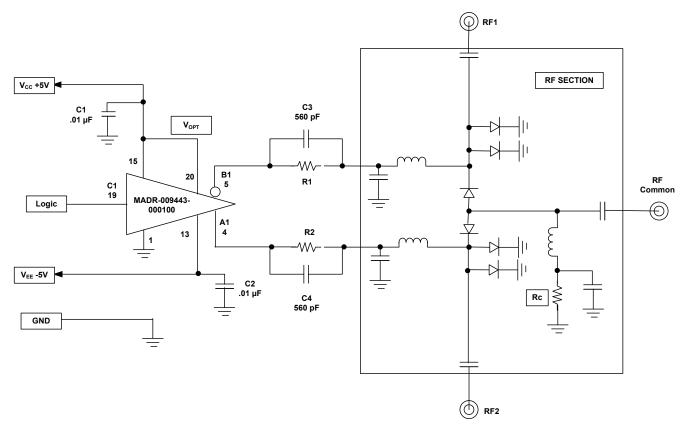

#### **Functional Schematic**

## Pin Configuration<sup>2</sup>

| Pin# | Function  | Pin# | Function         |

|------|-----------|------|------------------|

| 1    | Ground    | 11   | Output A4        |

| 2    | N/C       | 12   | Output B4        |

| 3    | N/C       | 13   | V <sub>EE</sub>  |

| 4    | Output A1 | 14   | N/C              |

| 5    | Output B1 | 15   | V <sub>CC</sub>  |

| 6    | Output A2 | 16   | C4               |

| 7    | Output B2 | 17   | C3               |

| 8    | NC        | 18   | C2               |

| 9    | Output A3 | 19   | C1               |

| 10   | Output B3 | 20   | V <sub>OPT</sub> |

The bottom of the die should be isolated or connected to ground.

<sup>\*</sup> Restrictions on Hazardous Substances, European Union Directive 2011/65/EU.

# Quad Driver for GaAs FET or PIN Diode Switches and Attenuators

Rev. V5

### **DC Characteristics over Guaranteed Operating Range**

| Symbol                | Parameter                                                   | Test Conditions                                                                                                                          | Units | Min.                   | Тур. | Max.                  |

|-----------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|------|-----------------------|

| V <sub>IH</sub>       | Input High Voltage                                          | Guaranteed High Input Voltage                                                                                                            | V     | 2.0                    | _    | _                     |

| V <sub>IL</sub>       | Input Low Voltage                                           | Guaranteed Low Input Voltage                                                                                                             | V     | _                      | _    | 0.8                   |

| V <sub>OH</sub>       | Output High Voltage                                         | I <sub>OH</sub> = -0.5 mA                                                                                                                | V     | V <sub>OPT</sub> - 0.1 | _    | _                     |

| V <sub>OL</sub>       | Output Low Voltage                                          | I <sub>OL</sub> = +0.5 mA                                                                                                                | V     | _                      | _    | V <sub>EE</sub> + 0.1 |

| I <sub>IN</sub>       | Input Leakage Current<br>(per input)                        | $V_{IN} = V_{CC}$ or GND, $V_{EE} = min$ , $V_{CC} = max$ , $V_{OPT} = min$ or max                                                       | nA    | -250                   | _    | 250                   |

| I <sub>OH</sub>       | DC Output Current - High (per output)                       | $V_{CC}$ = +5.0 V, $V_{EE}$ = -5.0 V, $V_{OPT}$ = +5.0 V                                                                                 | mA    | -35                    | _    | _                     |

| I <sub>OL</sub>       | DC Output Current - Low (per output)                        | $V_{CC} = +5.0 \text{ V}, V_{EE} = -5.0 \text{ V}, V_{OPT} = +5.0 \text{ V}$                                                             | mA    | _                      | _    | 35                    |

| I <sub>OH_SPIKE</sub> | Peak Spike Output Current<br>(Rising Edge)<br>(per output)  | $V_{CC}$ = +5.0 V, $V_{EE}$ = -5.0 V, $V_{OPT}$ = +5.0 V, $C_L$ = 25 pF                                                                  | mA    | _                      | 35   | _                     |

| I <sub>OL_SPIKE</sub> | Peak Spike Output Current<br>(Falling Edge)<br>(per output) | $V_{CC}$ = +5.0 V, $V_{EE}$ = -5.0 V, $V_{OPT}$ = +5.0 V, $C_L$ = 25 pF                                                                  | mA    | _                      | 50   | _                     |

| I <sub>cc</sub>       | Quiescent Supply Current                                    | $V_{\text{IN}}$ = $V_{\text{CC}}$ or GND, $V_{\text{EE}}$ = -10.5 V, $V_{\text{CC}}$ = +5.5 V, $V_{\text{OPT}}$ = +5.5 V, No Output Load | μA    | _                      | _    | 20                    |

| ΔI <sub>CC</sub>      | Additional Supply Current (per TTL input pin)               | $V_{CC}$ = max, $V_{IN}$ = $V_{CC}$ -2.1 V                                                                                               | mA    | _                      | _    | 1.0                   |

| I <sub>EE</sub>       | Quiescent Supply Current                                    | $V_{\text{IN}}$ = $V_{\text{CC}}$ or GND, $V_{\text{EE}}$ = -10.5 V, $V_{\text{CC}}$ = +5.5 V, $V_{\text{OPT}}$ = +5.5 V, No Output Load | μA    |                        | _    | 20                    |

| I <sub>OPT</sub>      | Quiescent Supply Current                                    | $V_{\text{IN}}$ = $V_{\text{CC}}$ or GND, $V_{\text{EE}}$ = -10.5 V, $V_{\text{CC}}$ = +5.5 V, $V_{\text{OPT}}$ = +5.5 V, No Output Load | μA    | _                      | _    | 20                    |

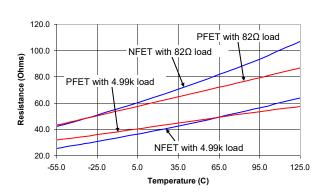

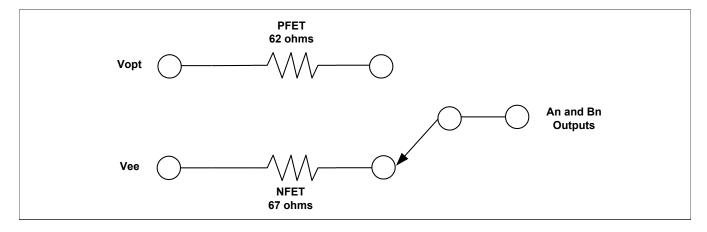

| R <sub>NFET</sub>     | Output Resistance NFET On (to V <sub>EE</sub> )             | $V_{CC}$ = +5.0 V, $V_{EE}$ = -5.0 V, $V_{OPT}$ = +5.0 V, $V_{OUT}$ = -4.9 V +25°C, Note 3                                               | Ω     | _                      | 40   | _                     |

| R <sub>PFET</sub>     | Output Resistance PFET On (to V <sub>OPT</sub> )            | $V_{CC}$ = +5.0 V, $V_{EE}$ = -5.0 V, $V_{OPT}$ = +5.0 V, $V_{OUT}$ = +4.9 V +25°C, Note 3                                               | Ω     | _                      | 45   | _                     |

<sup>3.</sup> See plot of  $R_{NFET}$  and  $R_{PFET}$  for variations over temperature for driving 4.99k and 82  $\Omega$  resistive load. (Note that this corresponds to 1 mA and 33 mA currents at +25°C).  $V_{OUT}$  is approximate for 1 mA load.

Rev. V5

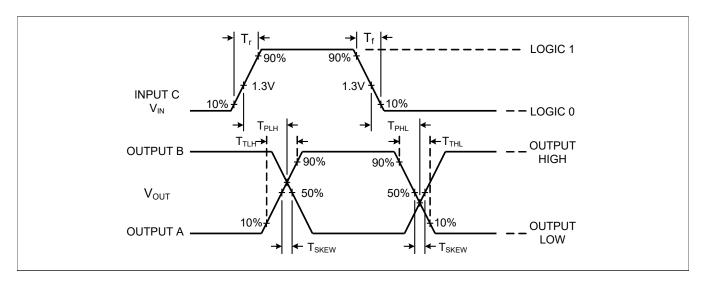

## AC Characteristics Over Guaranteed Operating Range<sup>4</sup>

| Symbol            | Symbol Parameter Unit                                       | Unit  | Typical performance |       |       |

|-------------------|-------------------------------------------------------------|-------|---------------------|-------|-------|

| Symbol            |                                                             | Offic | -40°C               | +25°C | +85°C |

| T <sub>PLH</sub>  | Propagation Delay                                           | ns    | 20                  | 22    | 25    |

| T <sub>PHL</sub>  | Propagation Delay                                           | ns    | 20                  | 22    | 25    |

| T <sub>TLH</sub>  | T <sub>TLH</sub> Output Transition Time (Rising Edge) ns    |       | 5                   | 6     | 8     |

| T <sub>THL</sub>  | Output Transition Time (Falling Edge)                       |       | 5                   | 6     | 8     |

| T <sub>skew</sub> | T <sub>skew</sub> Delay Skew                                |       | 2                   | 2     | 2     |

| PRF (max.)        | PRF (max.) 50% Duty Cycle                                   |       | DC                  | _     | 10    |

| C <sub>IN</sub>   | C <sub>IN</sub> Input Capacitance                           |       | 5                   | 5     | 5     |

| $C_{PDC}$         | C <sub>PDC</sub> Power Dissipation Capacitance <sup>5</sup> |       | 50                  | 50    | 50    |

| C <sub>PDE</sub>  | Power Dissipation Capacitance <sup>5</sup>                  | pF    | 100                 | 100   | 100   |

<sup>4.</sup> VCC = 4.5 V, VOPT = 0 V, VEE = min or max, CL = 25 pF, input LOGIC1 = 3 V, LOGIC0 = 0 V, TRISE, TFALL = 6 ns.

#### **Truth Table**

| Input     | Outputs          |                  |  |  |

|-----------|------------------|------------------|--|--|

| Cn        | An Bn            |                  |  |  |

| Logic "0" | V <sub>EE</sub>  | V <sub>OPT</sub> |  |  |

| Logic "1" | V <sub>OPT</sub> | V <sub>EE</sub>  |  |  |

### **Handling Procedures**

Please observe the following precautions to avoid damage:

### **Static Sensitivity**

Silicon Integrated Circuits are sensitive to electrostatic discharge (ESD) and can be damaged by static electricity. Proper ESD control techniques should be used when handling these devices.

## Output Resistance vs. Temperature<sup>6</sup>

6. Output resistance were measured under the condition of  $V_{CC}$  = +5.0 V,  $V_{OPT}$  = +5.0 V, and  $V_{EE}$  = -5.0 V, with load resistors from outputs to ground.

<sup>5.</sup> Total Power Dissipation is calculated by the following formula: PD = VCC2fC PDC + VEE2fCPDE

## Quad Driver for GaAs FET or PIN Diode **Switches and Attenuators**

Rev. V5

# Guaranteed Operating Ranges (for driving FET or PIN devices)<sup>7,8,9</sup>

| Symbol                                   | Parameter                                          | Unit | Min.  | Тур.       | Max.            |

|------------------------------------------|----------------------------------------------------|------|-------|------------|-----------------|

| V <sub>cc</sub>                          | Positive DC Supply Voltage                         | V    | 4.5   | 5.0        | 5.5             |

| V <sub>EE</sub>                          | Negative DC Supply Voltage                         | V    | -10.5 | -5.0       | -4.5            |

| V <sub>OPT</sub> <sup>10,11</sup>        | Optional DC Output Supply Voltage                  | V    | 0     | _          | V <sub>CC</sub> |

| V <sub>OPT</sub> - V <sub>EE</sub>       | PT - V <sub>EE</sub> Negative Supply Voltage Range |      | 4.5   | Note 10,11 | 16.0            |

| V <sub>CC</sub> - V <sub>EE</sub>        | Positive to negative Supply Range                  | V    | 9.0   | 10.0       | 16.0            |

| T <sub>OPER</sub>                        | T <sub>OPER</sub> Operating Temperature            |      | -40   | +25        | +85             |

| I <sub>OH</sub> DC Output Current - High |                                                    | mA   | -35   | _          | _               |

| I <sub>OL</sub>                          | DC Output Current - Low                            | mA   | _     | _          | 35              |

| T <sub>RISE</sub> , T <sub>FALL</sub>    | Maximum Input Rise or Fall Time                    | ns   | _     | _          | 500             |

Unused logic inputs must be tied to either GND or  $V_{\text{CC}}$ . MACOM recommends that  $V_{\text{CC}}$  be powered on before  $V_{\text{EE}}$ , and powered off after  $V_{\text{EE}}$ . 0.01  $\mu\text{F}$  decoupling capacitors are required on the power supply lines.

<sup>10.</sup> V<sub>OPT</sub> is grounded in most cases when FETs are driven. To improve the intermodulation performance and the 1 dB compression point of GaAs control devices at low frequencies, V<sub>OPT</sub> can be increased to between 1 and 2 V. The nonlinear characteristics of the GaAs control devices will approximate performance at 500 MHz. It should be noted that the control current that is on the GaAs MMICs will increase when positive controls are applied.

<sup>11.</sup> When this driver is used to drive PIN diodes,  $V_{OPT}$  is often set to +5 V, with  $V_{EE}$  set to -5 V.

## **Quad Driver for GaAs FET or PIN Diode Switches and Attenuators**

Rev. V5

## **Absolute Maximum Ratings**<sup>12</sup>

| Symbol                             | Parameter                                                                                                                                                                           |    | Min.                  | Max.                   |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------|------------------------|

| V <sub>CC</sub>                    | Positive DC Supply Voltage                                                                                                                                                          |    | -0.5                  | 7.0                    |

| Icc                                | Positive DC Supply Current (-0.5 V $\leq$ V <sub>IN</sub> $\leq$ 0.8 V; 2.0 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>CC</sub> +0.5 V; V <sub>CC</sub> - V <sub>IN</sub> $\leq$ 7.0 V) | mA | _                     | 20                     |

| V <sub>EE</sub>                    | Negative DC Supply Voltage                                                                                                                                                          | V  | -11.0                 | 0.5                    |

| I <sub>EE</sub>                    | Negative DC Supply Current (per Output) <sup>13</sup>                                                                                                                               | mA | -50                   | _                      |

| V <sub>OPT</sub>                   | Optional DC Output Supply Voltage                                                                                                                                                   | V  | -0.5                  | V <sub>CC</sub> +0.5   |

| I <sub>OPT</sub>                   | Optional DC Output Supply Current (per Output) <sup>13</sup>                                                                                                                        |    | _                     | 50                     |

| V <sub>OPT</sub> - V <sub>EE</sub> | Output to Negative Supply Voltage Range                                                                                                                                             |    | -0.5                  | 18.0                   |

| V <sub>CC</sub> - V <sub>EE</sub>  | Positive to Negative Supply Voltage Range                                                                                                                                           |    | -0.5                  | 18.0                   |

| V <sub>IN</sub>                    | DC Input Voltage                                                                                                                                                                    |    | -0.5<br>Note 14       | V <sub>CC</sub> +0.5   |

| Vo                                 | DC Output Voltage                                                                                                                                                                   |    | V <sub>EE</sub> – 0.5 | V <sub>OPT</sub> + 0.5 |

| P <sub>D</sub> <sup>15</sup>       | Power Dissipation in Still Air                                                                                                                                                      |    | _                     | 1                      |

| T <sub>OPER</sub>                  | Operating Temperature                                                                                                                                                               |    | -55                   | 125                    |

| T <sub>STG</sub>                   | Storage Temperature                                                                                                                                                                 |    | -65                   | 150                    |

| ESD                                | ESD Sensitivity                                                                                                                                                                     |    | 2.0                   | _                      |

<sup>12.</sup> All voltages are referenced to GND. All inputs and outputs incorporate latch-up protection structures.

<sup>13.</sup> The maximum I<sub>EE</sub> and I<sub>OPT</sub> are specified under the condition of V<sub>CC</sub> = +5.5 V, V<sub>EE</sub> = -5.5 V, V<sub>OPT</sub> = +5.5 V, and the total power dissipation is within 1 W in still air.

14. If V<sub>CC</sub> ≥ 6.5 V, then the minimum for V<sub>IN</sub> is V<sub>CC</sub> - 7.0 V.

15. Derate -7 mW/°C from 65°C to 85°C.

Rev. V5

### **Switching Waveforms**

## Equivalent Output Circuit for An and Bn Outputs (33 mA load at 25°C)

Rev. V5

### Typical Application for a SPDT Switch<sup>16</sup>

16. Only one section of MADR-009443 is shown. The other three sections will have equivalent performance.

### **Description of Circuit**

The MADR-009443 provides four pairs of complementary outputs that are each capable of driving a maximum of ±35 mA into a load. In addition, with proper capacitor selection (C3 & C4) used in parallel with the current setting resistor (R1 & R2), additional spiking current can be achieved.

To achieve the Non-Inverting and Inverting complementary voltages, each output is switched between two internal FETs. The FETs are connected to  $V_{\text{OPT}}$  for the positive output and  $V_{\text{EE}}$  for the negative output.  $V_{\text{OPT}}$  and  $V_{\text{EE}}$  are adjustable for various configurations and have the following limitations:  $V_{\text{EE}}$  can be no more negative than -10.5 volts;  $V_{\text{OPT}}$  can be no more positive than +5.5 volts and  $V_{\text{OPT}}$  must always be less than or equal to  $V_{\text{CC}}$ . Increasing  $V_{\text{OPT}}$  beyond  $V_{\text{CC}}$  will prevent the device from switching states when commanded to by the logic input. The most common configuration is to drive  $V_{\text{EE}}$  at -5.0 volts with  $V_{\text{CC}}$  and  $V_{\text{OPT}}$  tied together at +5.0 volts.

Rev. V5

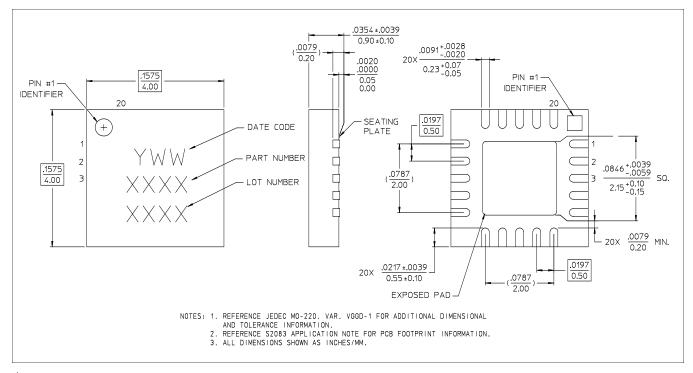

## Lead-Free, 4 mm, 20-lead PQFN<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> Reference Application Note M538 for lead-free solder reflow recommendations. Plating is 100% matte tin over copper.

Rev. V5

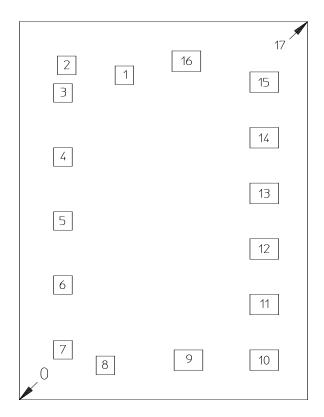

### Die Outline (MADR-009190-000DIE)

# Pad Configuration<sup>17,18</sup> Die Size: 1325 x 1735 μm (nominal)

| Pad<br>No. | X (μm)<br>nominal | Υ (μm)<br>nominal | Pad Size (µm)<br>X x Y  | Pad<br>Function |

|------------|-------------------|-------------------|-------------------------|-----------------|

| 0          | 0                 | 0                 | Lower left edge of die  | N/A             |

| 1          | 482.95            | 1489              | 85 x 85                 | Vee             |

| 2          | 217.85            | 1534.6            | 85 x 85                 | Vcc             |

| 3          | 200.45            | 1407.9            | 85 x 85                 | C4              |

| 4          | 200.45            | 1114.2            | 85 x 85                 | C3              |

| 5          | 200.45            | 820.45            | 85 x 85                 | C2              |

| 6          | 200.45            | 526.8             | 85 x 85                 | C1              |

| 7          | 200.45            | 229.35            | 85 x 85                 | Vopt            |

| 8          | 395.6             | 157.95            | 85 x 85                 | GND             |

| 9          | 777.55            | 181.5             | 132 x 94                | A1              |

| 10         | 1126.35           | 181.75            | 132 x 94                | B1              |

| 11         | 1126.35           | 436.85            | 132 x 94                | A2              |

| 12         | 1126.35           | 691.95            | 132 x 94                | B2              |

| 13         | 1126.35           | 947.05            | 132 x 94                | A3              |

| 14         | 1126.35           | 1202.15           | 132 x 94                | В3              |

| 15         | 1126.35           | 1457.3            | 132 x 94                | A4              |

| 16         | 767.9             | 1553.5            | 132 x 94                | B4              |

| 17         | 1325              | 1735              | Upper right edge of die | N/A             |

<sup>17.</sup> All X,Y dimensions are at bond pad center.

<sup>18.</sup> Die thickness is 8.0 mils.

**Quad Driver for GaAs FET or PIN Diode Switches and Attenuators**

Rev. V5

#### MACOM Technology Solutions Inc. All rights reserved.

Information in this document is provided in connection with MACOM Technology Solutions Inc ("MACOM") products. These materials are provided by MACOM as a service to its customers and may be used for informational purposes only. Except as provided in MACOM's Terms and Conditions of Sale for such products or in any separate agreement related to this document, MACOM assumes no liability whatsoever. MACOM assumes no responsibility for errors or omissions in these materials. MACOM may make changes to specifications and product descriptions at any time, without notice. MACOM makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions. No license, express or implied, by estoppels or otherwise, to any intellectual property rights is granted by this document.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MACOM PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MACOM FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MACOM SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

MACOM products are not intended for use in medical, lifesaving or life sustaining applications. MACOM customers using or selling MACOM products for use in such applications do so at their own risk and agree to fully indemnify MACOM for any damages resulting from such improper use or sale.