# Jew Designs WT11i DEVELOPMENT KIT

# **DATA SHEET**

⊥T Jetober 201 .5 Tuesday, 01 October 2013

Version 1 5

#### **VERSION HISTORY**

| Version | Comment           |

|---------|-------------------|

| 1.4     | Table 2 corrected |

| 1.5     | Minor changes     |

#### **TABLE OF CONTENTS**

| 1  | Introduction                |                | 5 |

|----|-----------------------------|----------------|---|

| 2  | Physical outlook            | 6              | ò |

| 3  | Schematics                  |                | 7 |

| 4  | Assembly                    |                | 7 |

| 5  | Gerber                      |                | 7 |

| 6  | SPI (J1) interface          |                | 3 |

| 7  | GPIO (J2) interface         |                |   |

| 8  | PIO SELECT (J3)             | 10             | ) |

| 9  | RESET (J4)                  |                |   |

| 10 |                             | 10             | ) |

| 11 | 1 Speaker JACK (J6)         |                | 1 |

| 12 | 2 Microphone JACK (J7)      | 1 <sup>2</sup> | 1 |

| 13 |                             | 1              | 1 |

| 14 | 4 RS-232 (J9) DTE interface |                | 2 |

| 15 | 5 USB (J10) interface       |                | 3 |

| 16 | 6 Power supply (J11)        |                | 3 |

| 17 |                             | 13             | 3 |

| 18 | Contact Information         | 14             | 1 |

| Š  |                             |                |   |

|    |                             |                |   |

#### Introduction

#### WT11i Development Kit Contents:

- WT11i development board containing:

- ot Recommended to the state of the state of

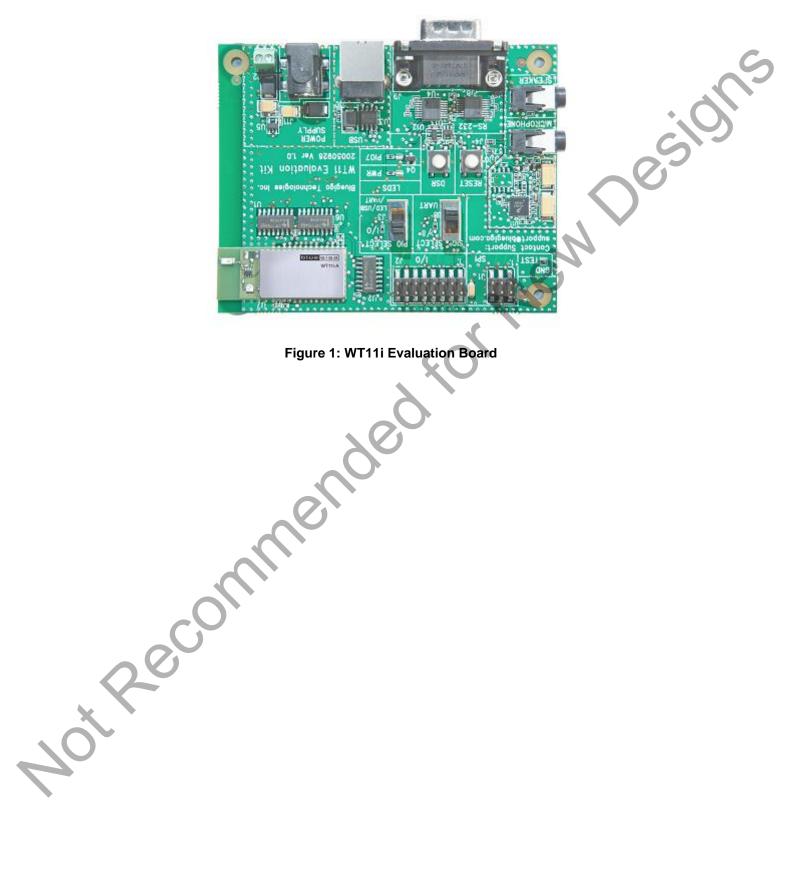

## 2 Physical outlook

Figure 1: WT11i Evaluation Board

#### 3 Schematics

Schematics of WT11 Evaluation Kit can be found from the CD delivered with the package or alternatively downloaded from <a href="http://www.bluegiga.com">http://www.bluegiga.com</a>

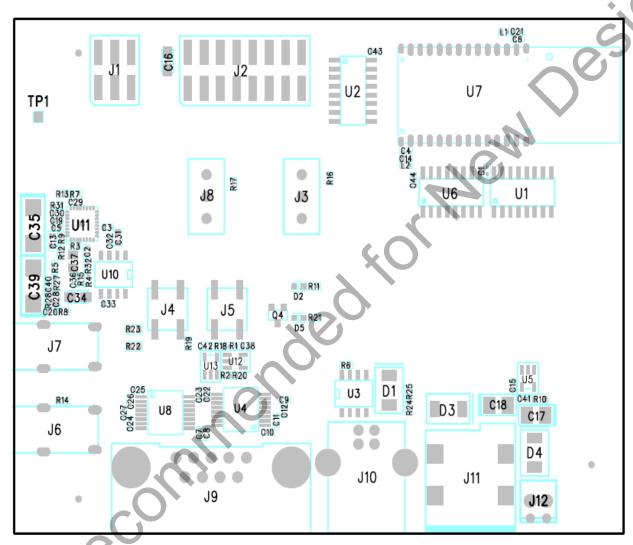

## 4 Assembly

Figure 2: WT11 Evaluation Kit assembly

## 5 Gerber

Gerber of WT11 Evaluation Kit can be downloaded from www.bluegiga.com.

### 6 SPI (J1) interface

SPI interface pin configuration is show in Table 2. The physical interface is 2X3 pin header (AMP146134-2).

| PIN Name: | No.: | I/O:  | Description:             |

|-----------|------|-------|--------------------------|

| MISO      | 1    | 0     | MISO                     |

| 3.3 V     | 2    | POWER | 3.3 V power supply input |

| CLK       | 3    | I     | CLK                      |

| MOSI      | 4    | I     | MOSI                     |

| CSB       | 5    | I     | CSB                      |

| GND       | 6    | GND   | GND                      |

Table 1: SPI Interface PIN description

# 7 GPIO (J2) interface

General purpose interface pin configuration is show in Table 2. The physical interface is 2X8 pin header (*AMP146134-7*).

| PIN Name: | No.: | I/O:  | Description:                            |

|-----------|------|-------|-----------------------------------------|

| RESET     | 1    | I     | Reset                                   |

| 3.3 V     | 2    | POWER | Regulated power supply output (3.3 V)   |

| PIO2      | 3    | I/O   | Programmable IO number 2                |

| PIO3      | 4    | I/O   | Programmable IO number 3                |

| PIO4      | 5    | I/O   | Programmable IO number 4                |

| PIO5      | 6    | 1/0   | Programmable IO number 5                |

| PIO6      | 7    | I/O   | Programmable IO number 6                |

| PIO7      | 8    | VO    | Programmable IO number 7                |

| RTS       | 9    | 0     | UART RTS                                |

| CTS       | 10   | I     | UART CTS                                |

| GND       | 11   | GND   | GND                                     |

| GND       | 12   | GND   | GND                                     |

| TxD       | 13   | 0     | UART TX                                 |

| RxD       | 14   | I     | UART RX                                 |

| GND       | 15   | GND   | GND                                     |

| +V        | 16   | POWER | Unregulated power supply output (5-9 V) |

Table 2: GPIO interface PIN description

#### 8 PIO SELECT (J3)

This switch toggles PIO2 to PIO7 signal connections between J2 connector and LED/USB/UART interfaces.

Note: 'Top' and 'bottom' positions refer to viewing WT11 Evaluation Kit from top side as seen in Figure 2.

- Top position must be used when WT11 module is interfaced trough J2 connector.

- Bottom position is used when WT11 module is interfaced trough the DB9 RS232 connector or if USB port or if link state LED is used.

#### **J3 Switch top position:**

- PIO2 connects to pin 3 on the J2 interface

- PIO3 connects to pin 4 on the J2 interface

- PIO4 connects to pin 5 on the J2 interface

- PIO5 connects to pin 6 on the J2 interface

- PIO6 connects to pin 7 on the J2 interface

- PIO7 connects to pin 8 on the J2 interface

#### J3 Switch bottom position:

- PIO2 connects to USB IO1

- PIO3 connects to nDTR-UART

- PIO4 connects to nCD-UART

- PIO5 connects to nDSR-MUX

- PIO6 connects to VBUS

- PIO7 connects to blue LED on the board marked with PIO7

## 9 RESET (J4)

The RESET button resets the module using the reset pin on the WT11.

### 10 DSR (J5)

The DSR button is connected to PIO5 pin on the WT11. Thus, when you want to use the DSR signal, please refer to the iWRAP 2.1.0 manual. The use of DSR signal is described under SET CONTROL ESCAPE chapter.

## 11 Speaker JACK (J6)

Connect your generic PC headset's 3,5mm speaker plug here.

## 12 Microphone JACK (J7)

Connect your generic PC headset's 3,5mm headphone plug here.

#### 13 SIG Select (J8)

This switch toggles nCTS and RxD signals connection between J2 connector and DB9 RS232 connector.

Note: 'Top' and 'bottom' positions refer to viewing WT11 Evaluation Kit from top side as seen in Figure 2.

- Top position must be used when external WT11 module's nCTS and RxD pins are interfaced trough J2 connector.

- Bottom position must be used when WT11 is interfaced trough the DB9 RS232 connector.

#### J8 Switch top position:

- nCTS connects to pin 10 on the GPIO (J2) interface

- · RxD connects to pin 14 on the GPIO (J2) interface

#### J8 Switch bottom position:

- nCTS connects to nCTS-UART

- RxD connects to RXD-UART

## 14 RS-232 (J9) DTE interface

RS-232 interface PIN configuration is shown in Table 1. The physical interface is D9-male connector (AMP747840-4).

| PIN Name: | No.: | I/O: | Description:  |

|-----------|------|------|---------------|

| NC        | 1    | NC   | Not connected |

| RxD       | 2    | I    | RxD           |

| TxD       | 3    | 0    | TxD           |

| DTR       | 4    | 0    | DTR on        |

| GND       | 5    | GND  | Ground        |

| NC        | 6    | NC   | Not connected |

| RTS       | 7    | 0 60 | RTS           |

| CTS       | 8    | 7    | CTS           |

| NC        | 9    | NC   | Not connected |

Table 3: RS232 PIN configuration

### 15 USB (J10) interface

J10 connector is a standard USB B receptacle connector.

## 16 Power supply (J11)

This connector is used with the 5V power supply delivered with the evaluation kit. Diameter 6.0mm, inner pin diameter 2.0mm.

#### 17 Power supply (J12)

at be 5-9V unre This connector can be used for external power supply. Power supply must be 5-9V unregulated.

loT Portfolio www.silabs.com/loT

**SW/HW** www.silabs.com/simplicity

Quality www.silabs.com/quality

Support and Community community.silabs.com

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are not designed or authorized for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labse®, Bluegiga®, Bluegiga®, Bluegiga®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701