## **Address Generator**

## ADSP-1410

**FEATURES**

16-Bit Addresses with Higher Precision Options

Look-Ahead<sup>TM</sup> Pipeline

80ns Cycle Time

20ns Clock-to-Address Delay

Versatile Addressing Hardware:

30 16-Bit Registers

16-Bit ALU with Left/Right Shift & Carry I/O

Comparator

**Bit Reverser**

**Dual Ports**

**Powerful Single-Cycle Looping Instructions**

Low-Power TTL-Compatible 1.5 Micron CMOS

Technology

175mW Max Power Dissipation

48-Pin DIP (Ceramic or Low-Cost Plastic)

## GENERAL DESCRIPTION

The ADSP-1410 is a fast, flexible address generator optimized for digital signal processors and general purpose computers. This lowpower CMOS device rapidly generates the data memory addresses required by routines such as digital filters, FFTs, matrix operations, and DMAs.

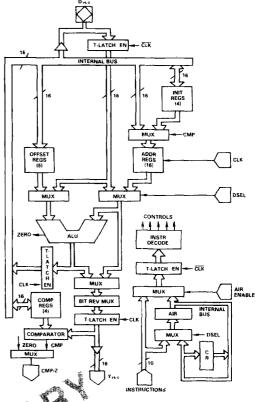

The ADSP-1410's 10-bit microcode instructions include commands for looping, register read/writes, internal data transfers, and logical/shift operations. An internal Alternate Instruction Register (AIR) can also provide the instruction under external control, allowing microcode to be conserved in many applications.

In a single instruction cycle, the ADSP-1410 can:

- output a 16-bit memory address

- modify this memory address

- conditionally reinitialize the address based on a comparison with a preset value.

Consequently, circular buffers and modulo addressing of data memories can be implemented without overhead.

The ADSP-1410's architecture features a 16-bit ALU, a comparator, and 30 16-bit registers. The registers are organized into four files: sixteen address registers, six offset registers, four con pare registers, and four initialization registers.

The ADSP-1410 has a 16-bit address (Y) port for o dresses and a 16-bit data (D) port for I/O between ternal registers. A value provided by the da input to the 1410's ALU or may be directly of port.

## ADSP-1410 ADDRESS GENERATOR

ook-Ahead pipeline eliminates the need for an code pipeline register by internally latching instrucddresses. complementary latching arrangement allows w instruction to be ecoded (in preparation for the following ycle) where the ta memory address for the current cycle is held

Precision (30-bit), single-cycle addressing can be performcascadin two ADSP-1410's. Alternatively, a single P-1410 cappeovide one double-precision address every two

DSP-1410 is available for both commercial and military temrature ranges. Extended temperature range parts are available with high-reliability processing ("PLUS" parts). MIL-grade parts are available processed fully to MIL-STD-883, Class B. Packaging options include a 48-pin ceramic DIP and a low cost 48-pin plastic

Look-Ahead is a trademark of Analog Devices, Inc.