# **ISD1000A Series**

# Single-Chip Voice Record/Playback Devices 16- and 20-Second Durations

#### **GENERAL DESCRIPTION**

Information Storage Devices' ISD1000A ChipCorder™ Series provides high-quality, single-chip record/playback solutions for 16- and 20-second messaging applications. The ISD1000A Series replaces the ISD1000 Series, with improved noise characteristics, and it is fully compatible with ISD1000 Series devices. The CMOS devices include an on-chip oscillator, microphone preamplifier, automatic gain control, antialiasing filter, smoothing filter, and speaker amplifier. In addition, the ISD1000A Series is fully microprocessor-compatible, allowing complex messaging and addressing to be achieved.

Recordings are stored in on-board non-volatile memory cells, providing zero-power message storage. This unique solution is made possible through ISD's patented Direct Analog Storage Technology (DAST $^{\text{TM}}$ ), whereby voice and audio signals are stored directly, in their natural analog form, into memory. Direct analog storage allows natural voice reproduction in a single-chip, solid-state solution.

#### **ISD1000A SERIES SUMMARY**

| Part<br>Number | Duration<br>(Seconds) | Input Sample<br>Rate (KHz) | UpperPass<br>Band (KHz) |

|----------------|-----------------------|----------------------------|-------------------------|

| ISD1016A       | 16                    | 8                          | 3.4                     |

| ISD1020A       | 20                    | 6.4                        | 2.7                     |

#### **FEATURES**

- Easy-to-use single-chip voice record/playback solution

- No external ICs required

- No development system required

- High-quality, natural voice/audio reproduction

- Manual switch or microprocessor controllable

- Playback can be edge- or level-activated

- Single-chip durations of 16 and 20 seconds

- Directly cascadable for longer durations

- Zero-power message storage

- Eliminates battery backup circuits

- Power-Down Mode

- 1 μA standby current (typical)

- Fully addressable to handle multiple messages

- 100-year message retention (typical)

- 100K record cycles (typical)

- On-chip clock source

- On-chip Automatic Gain Control (AGC)

- Single +5 Volt Supply

- Low-voltage (3.6 V to 4.0 V) versions available

- Available in die form, DIP, and SOIC packaging

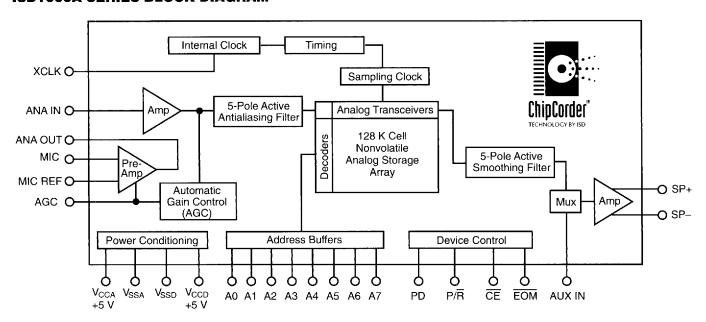

#### ISD1000A SERIES BLOCK DIAGRAM

DATA SHEET

#### **GENERAL DESCRIPTION**

The ISD1000A ChipCorder™ Series devices are designed to record and play back audio and voice information in a single chip with a minimum of circuit complexity. This compact, easy-to-use, nonvolatile, low-power solution has been made possible by ISD's patented DAST™ technology — a breakthrough in Direct Analog Storage Technology in EEPROM. ISD's DAST technology results in storage density that is eight times greater than digital memory. The DAST nonvolatile analog array consists of 128K cells — the equivalent of 1 Mbits of digital storage.

The ISD1000A Series eliminates the need for digital conversion, digital compression, and voice synthesis techniques which often compromise voice quality and are more complicated to use. The ISD1000A Series of devices includes signal conditioning circuits and control functions which enable a complete, high-quality recording and playback system in a single device. The ISD1000A is available in two versions, which store voice in 16- or 20-second DAST arrays. Additional devices may be cascaded to achieve longer recording durations. The nonvolatile storage array is based on production-proven, low-power CMOS EEPROM technology.

The highly integrated ISD1000A Series contains all the basic functions required for high-quality voice recording and playback. The noise-cancelling Microphone Preamplifier and Automatic Gain Control (AGC) record both low-volume and high-volume sounds. The AGC attack and release times are adjusted by an external resistor and capacitor. Antialiasing is performed by a continuous fifth-order Chebyshev filter, requiring no external components or clocks to give toll-quality reproduction. The low corner of the passband is user-settable by two external capacitors. The devices contain their own temperature-stabilized timebase oscillator.

The ISD1000A devices drive a speaker directly through differential outputs. This boosts power by four times and eliminates the need for a series capacitor or an output amplifier. The device will operate from a single 5-volt power supply or from batteries. The device also includes a power down function for applications where minimum power consumption is critical. The CMOS-based design, combined with the nonvolatile storage array, assures the lowest possible overall power consumption.

On-chip control functions make the ISD1000A Series very easy to use in a wide array of applications. Each device offers a variety of operating modes and interface options. The devices may be used in applications that require little more than a few switches and a battery. The devices may also be integrated into electronic systems where digital addresses can be provided for more sophisticated message addressing and control. The

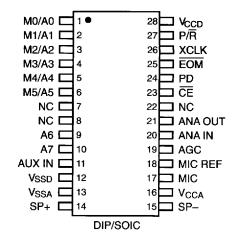

#### **ISD1000A SERIES PINOUTS**

ISD1000A DAST arrays are organized in 160 segments. Addresses A0 through A7 provide access to each segment in the array for message addressing. Addressing provides the capability of constructing messages by concatenating stored phrases and sounds.

# ISD1000A SERIES — PIN DESCRIPTIONS

#### Microphone Input (MIC)

An external microphone should be AC coupled to this pin via a series capacitor. The user-selectable value of the input series capacitor, together with the internal  $10~\mathrm{K}\Omega$  resistance on this pin, determines the low frequency cutoff for the ISD1000A Series passband.

#### Microphone Reference Input (MIC REF)

By connecting this pin to  $V_{SSA}$  (analog ground) via a series capacitor, common mode noise can be rejected at the preamplifier. The capacitor value should be exactly the same value as the input coupling capacitor used for microphone input. Using this approach may provide up to a 10 dB noise improvement. IF THIS INPUT IS UNUSED, IT MUST BE LEFT DISCONNECTED.

#### **Analog Output (ANA OUT)**

This pin provides the preamplifier output to the user. The voltage gain of the preamplifier is determined by the voltage level at the AGC pin. It has a maximum gain of about 24 dB for small input signal levels.

#### **Analog Input (ANA IN)**

The analog input pin transfers its signal to the chip for recording. For microphone inputs, the ANA OUT pin should be connected via an external capacitor to the ANA IN pin. This capacitor value, together with the 2.7  $K\Omega$  input impedance of ANA IN, can be selected to give additional cutoff at the low-frequency end of the voice passband. If the desired input is derived from a source other than a microphone, the signal can be fed, capacitively coupled, into the ANA IN pin directly.

# **Automatic Gain Control Input (AGC)**

The AGC dynamically adjusts the gain of the preamplifier to compensate for the wide range of microphone input levels. The AGC allows the full range of whispers to loud sounds to be recorded with minimal distortion. The "attack" time is determined by the time constant of a  $5\,\mathrm{K}\Omega$  internal resistance and an external capacitor (C2) connected from the AGC pin to  $V_{SSA}$  analog ground. The "release" time is determined by the time constant of an external resistor (R2) and an external capacitor (C2) connected in parallel between the AGC Pin and  $V_{SSA}$  analog ground. Nominal values of  $470\,\mathrm{K}\Omega$  and  $4.7\,\mu\mathrm{F}$  give satisfactory results in most cases. For AGC voltages of 1.5 V and below, the preamplifier is at its maximum gain of  $24\,\mathrm{dB}$ . Reduction in preamplifier gain occurs for voltages of approximately  $1.8\,\mathrm{V}$ .

# Speaker Outputs (SP+/SP-)

The SP+ and SP-pins provide direct drive for loudspeakers with impedances as low as 16 ohms. A single output may be used, however, for direct-drive loudspeakers, the two opposite-polarity outputs give an improvement in output power of up to four times over a single-ended connection. Furthermore, a single-ended connection requires an AC-coupling capacitor between the SP pin and the speaker. When the SP+ and SP-connections are used, this capacitor is not required.

The speaker outputs are held at V<sub>SSA</sub> levels during record and power down. It is therefore not possible to parallel speaker outputs of multiple ISD1000A devices or the outputs of other speaker drivers.

CONNECTION OF SPEAKER OUTPUTS IN PARAL-LELMAY CAUSE DAMAGE TO THE DEVICE. NEVER GROUND OR DRIVE AN UNUSED SPEAKER OUTPUT.

# Power Down Input (PD)

When not recording or playing back, the PD pin should be pulled HIGH to place the part in a very low power mode (see  $I_{SB}$  specification). When  $\overline{EOM}$  pulses LOW for an overflow condition, PD should be brought HIGH to reset the address pointer back to the beginning of the Record/Playback space.

# Chip Enable Input (CE)

The  $\overline{CE}$  pin is taken LOW to enable all Playback and Record operations. The address inputs and Playback/Record input (P/ $\overline{R}$ ) are latched by the falling edge of  $\overline{CE}$ . When  $\overline{CE}$  is taken HIGH, the ISD1000A is unselected, and the auxiliary input is directed into the speaker amplifier.

# Playback/Record Input $(P/\overline{R})$

The  $P/\overline{R}$  input is latched by the falling edge of the  $\overline{CE}$  pin. A HIGH level selects a Playback cycle while a LOW level selects a Record cycle. For a Record cycle, the address inputs provide the starting address and

recording continues until PD or  $\overline{\text{CE}}$  is pulled HIGH or an overflow is detected (i.e. the chip is full). When a Record cycle is terminated by pulling PD or  $\overline{\text{CE}}$  HIGH, an End-Of-Message  $(\overline{\text{EOM}})$  marker is stored at the current address in memory. For a Playback cycle, the address inputs provide the starting address and the device will play until an  $\overline{\text{EOM}}$  marker is encountered. The device can continue past an  $\overline{\text{EOM}}$  marker in an operational mode, or if  $\overline{\text{CE}}$  is held LOW in address mode. (See Table 1, Page 5 for more Operational Modes).

# Address/Mode Inputs (A0-A7)

The Address/Mode Inputs provide two functions in the ISD1000A Series: 1. Message address (A6 or A7 = LOW) and 2. ISD1000A Series Operational Mode Options (A6 AND A7 = HIGH).

Operational mode options are shown in Table 1 (Page 4). There are a maximum of 160 message addresses (or segments). Each segment corresponds to one of 160 rows in the analog storage array. The message addresses (segments) are in locations 0 through 159 contiguous. The playback/record duration of each segment depends upon the device and is as follows:

| Part Number | Segment Playback/Record Duration |  |  |  |  |  |

|-------------|----------------------------------|--|--|--|--|--|

| ISD1016A    | 0.100 sec.                       |  |  |  |  |  |

| ISD1020A    | 0.125 sec.                       |  |  |  |  |  |

An operation may be started at any address, as defined by address pins A0-A7. Record or playback continues with automatic incrementing of the internal on-chip address until either  $\overline{CE}$  is brought HIGH (Record), an end of message marker is encountered (Playback with  $\overline{CE}$  HIGH), or an overflow (device full) condition results.

# Optional External Clock Input (XCLK)

This signal is normally tied to ground in application circuits. If, however, greater timing precision is desired, (internal clock has +2.25 % tolerance over temperature and voltage range), the chip can be externally clocked through this pin. For the ISD10xxA"I," (Industrial Temperature), the internal clock variance has a 5% tolerance over the temperature and voltage ranges. A regulated power supply is recommended.

For the ISD1016A the external clock should be a 1024 KHz signal, and for the ISD1020A, a 819 KHz signal. The duty cycle on the input clock is not critical, as the clock is immediately divided by two. IF THE XCLK IS NOT USED, THIS INPUT MUST BE CONNECTED TO GROUND.

#### End-Of-Message Output (EOM)

A non-volatile marker is automatically inserted at the end of each recorded message. It remains there until the message

is recorded over. The EOM output pulses LOW for a period of T<sub>EOM</sub> at the end of each message, or in the event of a message overflow (device full).

In addition, the ISD1000A Series has an internal  $V_{CC}$ detect circuit to maintain message integrity should V<sub>CC</sub> fall below 3.5V. In this case, EOM goes LOW and the device is fixed in Playback-only mode. The EOM marker provides a convenient handshake signal for a processor, and also facilitates the cascading of devices.

# Auxiliary Input (AUX IN)

The Auxiliary Input is multiplexed through to the output amplifier and speaker output pins when CE is HIGH and Playback has ended, or if the device is in overflow. When cascading multiple ISD1000A devices, the AUX IN pin is used to connect a Playback signal from a following device to the previous output speaker drivers. For noise considerations, it is suggested that the auxiliary input not be driven when the storage array is active.

# Voltage Inputs (V<sub>CCA</sub>, V<sub>CCD</sub>)

To minimize noise, the analog and digital circuits in the ISD1000A Series devices use separate power busses. These +5 V busses are brought out to separate pins and should be tied together as close to the supply as possible. In addition, these supplies should be decoupled as close to the package as possible.

# Ground Inputs (V<sub>SSA</sub>, V<sub>SSD</sub>)

The ISD1000A Series of devices utilizes separate analog and digital ground busses. These pins should be tied together as close to the package as possible and connected through a low-impedance path to power supply ground.

# **OPERATIONAL MODES**

The ISD1000A Series is designed with several built-in operational modes provided to allow maximum functionality with a minimum of additional components, described in detail below. The operational modes use the address pins on the ISD1000A devices, but are mapped outside the valid address range. When the two Most Significant Bits (MSBs) are HIGH, the remaining address signals are interpreted as mode bits and NOT as address bits. Therefore, operational modes and direct addressing are not compatible and cannot be used simultaneously.

There are two important considerations for using operational modes. First, all operations begin initially at address 0, which is the beginning of the ISD1000A address space. Later operations can begin at other address locations, depending on the operational mode(s) chosen. In addition, the address pointer is reset to 0 when the device is changed from Record to Playback, Playback to Record, or when a Power-Down cycle is executed.

Second, an Operational Mode is executed when  $\overline{CE}$  goes LOW and the two MSBs are HIGH. This Operational Mode remains in effect until the next LOW-going CE signal, at which point the current address/mode levels are sampled and executed.

(Note: The two MSBs are on pins 9 and 10 for each ISD1000A Series member.)

#### **OPERATIONAL MODE DESCRIPTIONS**

The Operational Modes can be used in conjunction with a microcontroller, or they can be hard-wired to provide the desired system operation.

# M0 — Message Cueing

Message Cueing allows the user to skip through messages, without knowing the actual physical addresses of each message. Each CE LOW pulse causes the internal address pointer to skip to the next message. This mode should be used for Playback only, and is typically used with the M4 Operational Mode.

# M1 — Delete **EOM** Markers

The M1 Operational Mode allows sequentially recorded messages to be concatenated into a single message with only one EOM marker set at the end of the combined message. When this operational mode is configured, messages recorded sequentially are played back as one continuous message.

# M2 — Used for Cascading

During playback, EOM pulses LOW at array overflow only.

#### M3 — Message Looping

The M3 Operational Mode allows for the automatic, continuously repeated playback of the message located at the beginning of the address space. A message CAN completely fill the ISD1000A device and will loop from beginning to end without EOM going LOW.

#### M4 — Consecutive Addressing

During normal operations, the address pointer will reset when a message is played through to an  $\overline{EOM}$  marker. The M4 Operational Mode inhibits the address pointer reset on EOM, allowing messages to be played back consecutively.

#### M5 — CE Level Activated

The default mode for ISD1000A devices is for CE to be edgeactivated on Playback and level-activated on Record. The M5 Operational Mode causes the  $\overline{\text{CE}}$  pin to be interpreted as level-activated as opposed to edge-activated during Playback. This is specifically useful for terminating Playback operations using the CE signal. In this mode, CE LOW begins a Playback cycle,  $\overline{CE}$  HIGH stops the cycle, and  $\overline{CE}$ LOW again will begin playing at the point where the message was stopped without resetting the address pointer.

**DATA SHEET**

#### **TABLE 1. OPERATIONAL MODES**

| Mode<br>Control | Function               | Typical Use                                        | Jointly*<br>Compatible |

|-----------------|------------------------|----------------------------------------------------|------------------------|

| M0              | Message cueing         | Fast-forward through messages                      | M4, M5                 |

| M1              | Delete EOM markers     | Position EOM marker at the end of the last message | M3, M4, M5             |

| M2              | Cascading              | Adding devices to extend duration                  |                        |

| M3              | Looping                | Continuous playback from address 0                 | M1, M5                 |

| M4              | Consecutive addressing | Record/Play multiple consecutive messages          | M0, M1, M5             |

| M5              | CE level-activated     | Allows message pausing                             | M0,M1, M3, M4          |

<sup>\*</sup> Indicates additional operational modes which can be used simultaneously with the given mode.

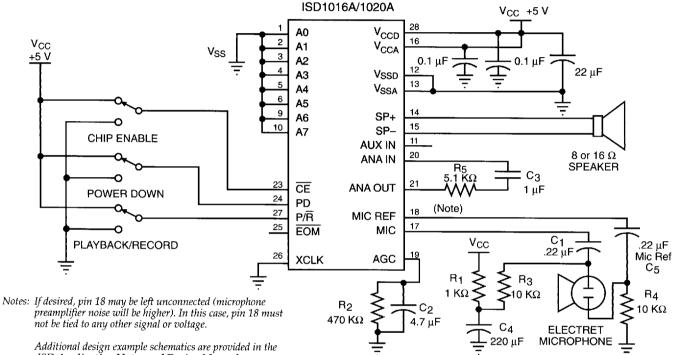

#### **APPLICATION EXAMPLE - DESIGN SCHEMATIC**

# ISD Application Notes and Design Manual.

# **APPLICATION EXAMPLE -BASIC DEVICE CONTROL**

| Control<br>Step | Function            | Action                              |

|-----------------|---------------------|-------------------------------------|

| 1               | Power up chip and   | 1. PD = LOW                         |

|                 | select record/play- | 2. $P/R = As$ desired               |

|                 | back mode           |                                     |

| 2               | Set message address | Set addresses                       |

|                 | for record/playback | A0-A7                               |

| 3               | Begin playback/     | $\overline{\text{CE}}$ = Pulsed LOW |

|                 | record              |                                     |

| 4               | End cycle           | CE = HIGH and                       |

|                 |                     | EOM reached                         |

| Part | Function                                                        | Comments                                                                         |

|------|-----------------------------------------------------------------|----------------------------------------------------------------------------------|

| R1   | Microphone power supply decoupling                              | Reduces power supply noise                                                       |

| R2   | Release time constant                                           | Sets release time for AGC                                                        |

| R3   | Microphone biasing resistor                                     | Provides biasing for microphone operation                                        |

| C1   | Microphone DC-block-<br>ing capacitor. Low-<br>frequency cutoff | Decouples microphone<br>bias from chip. Provides<br>single-pole low-freq. cutoff |

| C2   | Attack/Release time constant                                    | Sets attack/release<br>time for AGC                                              |

| C3   | Low-frequency cutoff capacitor                                  | Provides additional pole for low-frequency cutoff                                |

| C4   | Microphone power supply decoupling                              | Reduces power supply noise                                                       |

| C5   | Common-mode capacitor                                           | Provides common-<br>mode noise rejection                                         |

**APPLICATION EXAMPLE - PASSIVE COMPONENTS**

- DATA SHEET

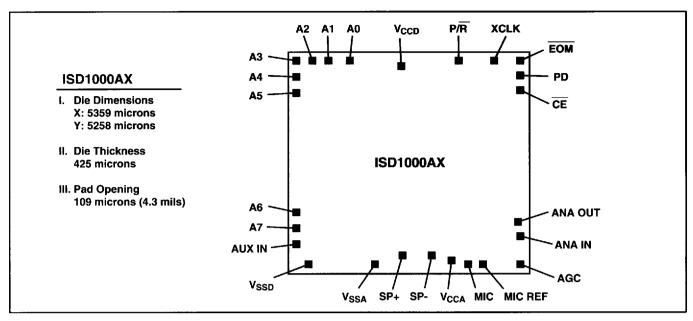

# DIE BONDING PHYSICAL LAYOUT (1)

# PIN/PAD DESIGNATIONS (1,2)

| Pin                     | Pin Name                             | X Axis         | Y Axis          | Pin              | Pin Name                             | X Axis | Y Axis  |

|-------------------------|--------------------------------------|----------------|-----------------|------------------|--------------------------------------|--------|---------|

| A0                      | Address                              | -1712.5        | 2445.5          | V <sub>CCA</sub> | V <sub>CC</sub> Analog Power Supply  | 952.5  | -2412   |

| A1                      | Address                              | -2068          | 2445.5          | MIC              | Microphone Input                     | 1217.5 | -2459   |

| A2                      | Address                              | -2278          | 2445.5          | MIC REF          | Microphone Reference                 | 1439   | -2459   |

| A3                      | Address                              | -2509.5        | 2368            | AGC              | Automatic Gain Control               | 2450.5 | -2410   |

| A4                      | Address                              | -2509.5        | 2145.5          | ANA IN           | Analog Input                         | 2484.5 | -1980.5 |

| A5                      | Address                              | -2509.5        | 1885.5          | ANA OUT          | Analog Output                        | 2466.5 | -1715.5 |

| A6                      | Address                              | -2509.5        | -1525.5         | CE               | Chip Enable                          | 2495.5 | 1989    |

| A7                      | Address                              | -2509.5        | -1764           | PD               | Power Down                           | 2495.5 | 2201    |

| AUX IN                  | Auxiliary Input                      | -2509.5        | <i>-</i> 2178.5 | EOM              | End of Message                       | 2493   | 2443    |

| $\overline{ m V_{SSD}}$ | V <sub>SS</sub> Digital Power Supply | -2359.5        | -2456.5         | XCLK             | External Clock                       | 1970   | 2445.5  |

| V <sub>SSA</sub>        | V <sub>SS</sub> Analog Power Supply  | <b>-46</b> 9.5 | -2456.5         | P/R              | Playback/Record                      | 900    | 2445.5  |

| SP+                     | Speaker Output +                     | -29            | -2362.5         | V <sub>CCD</sub> | V <sub>CC</sub> Digital Power Supply | -52.5  | 2390    |

| SP-                     | Speaker Output –                     | 508            | -2362.5         |                  |                                      |        |         |

Note: 1. Applies to ISD1000A Series product fabricated subsequent to February, 1993.

2. Pad coordinates (in microns) relative to die center

#### **ABSOLUTE MAXIMUM RATINGS**

| Condition                                                         | Value                                                    |

|-------------------------------------------------------------------|----------------------------------------------------------|

| Temperature under bias                                            | -65° C to +125° C                                        |

| Storage temperature range                                         | -65° C to +150° C                                        |

| Voltage applied to any pin                                        | $(V_{SS} - 0.3 \text{ V})$ to $(V_{CC} + 0.3 \text{ V})$ |

| Voltage applied to any pin (Input current limited to $\pm$ 20 mA) | $(V_{SS} - 1.0 \text{ V})$ to $(V_{CC} + 1.0 \text{ V})$ |

| Lead temperature (soldering – 10 seconds)                         | 300° C                                                   |

| V <sub>CC</sub> - V <sub>SS</sub>                                 | - 0.3 V to + 7.0 V                                       |

Stresses above those listed may cause permanent damage to the device. Exposure to the absolute maximum ratings may affect device reliability. Functional operation is not implied at these conditions.

#### **DC PARAMETERS**

Operating Conditions:  $T_A = 0^\circ$  C to  $70^\circ$  C <sup>(1)</sup>,  $V_{CC} = 4.5$  V to 6.5 V <sup>(2)</sup>,  $V_{SS} = 0$  V <sup>(3)</sup>; unless otherwise noted

| Symbol                                | Parameters                          | Min          | Typ (4) | Max        | Units | Conditions                 |

|---------------------------------------|-------------------------------------|--------------|---------|------------|-------|----------------------------|

| V <sub>IL</sub>                       | Input Low Voltage                   |              |         | 0.8        | V     |                            |

| V <sub>IH</sub>                       | Input High Voltage                  | 2.0          |         |            | V     |                            |

| V <sub>OL</sub>                       | Output Low Voltage                  |              |         | 0.4        | V     | $I_{OL} = 4.0 \text{ mA}$  |

| V <sub>OH</sub>                       | Output High Voltage                 | 2.4          |         |            | V     | I <sub>OH</sub> = - 1.6 mA |

| $V_{OH1}$                             | Output High Voltage                 | $V_{CC}-0.4$ |         |            | V     | $I_{OH} = -10 \mu A$       |

| $I_{CC}$                              | V <sub>CC</sub> Current (Operating) |              | 25      | 30         | mA    | $R_{EXT} = \infty$ (5)     |

| $I_{\mathrm{SB}}$                     | V <sub>CC</sub> Current (Standby)   |              | 1       | 10         | μΑ    | (5)                        |

| $\overline{\mathrm{I}_{\mathrm{IL}}}$ | Input Leakage Current               |              |         | <u>+</u> 1 | μΑ    |                            |

| R <sub>EXT</sub>                      | Output Load Impedance               | 16           |         |            | Ω     | Speaker Load               |

| R <sub>MIC</sub>                      | Preamp In Input Resistance          |              | 10      |            | ΚΩ    | Pins 17, 18                |

| R <sub>AUX</sub>                      | AUX Input Resistance                |              | 10      | •          | ΚΩ    |                            |

| R <sub>ANA IN</sub>                   | ANA IN Input Resistance             |              | 3.0     |            | ΚΩ    |                            |

| A <sub>PRE1</sub>                     | Preamp Gain 1                       |              | 24      |            | dB    | AGC = 0.0  V               |

| A <sub>PRE2</sub>                     | Preamp Gain 2                       |              | -45     | 15         | dB    | AGC = 2.5 V                |

| A <sub>AUX</sub>                      | AUX IN/SP+ Gain                     | 0.9          |         | 1.0        | V/V   |                            |

| $A_{ARP}$                             | ANA IN to SP+/-                     |              | 22      |            | dB    |                            |

| R <sub>AGC</sub>                      | AGC Output Resistance               |              | 5       |            | ΚΩ    |                            |

| I <sub>PREH</sub>                     | Preamp Out Source                   |              | -1      |            | mA    | $@V_{OUT} = 1.0 \text{ V}$ |

| I <sub>PREL</sub>                     | Preamp In Sink                      |              | 0.8     |            | mA    | $@V_{OUT} = 2.0 \text{ V}$ |

Notes: 1. Case temperature.

- 2.  $V_{CC} = V_{CCA} = V_{CCD}$ . 3.  $V_{SS} = V_{SSA} = V_{SSD}$ . 4. Typical values @  $T_A = 25^{\circ}$  C and 5.0 V. 5.  $V_{CCA}$  and  $V_{CCD}$  connected together.

- DATA SHEET

# AC PARAMETERS (ISD1016A — 16-SECOND DURATION)

Operating Conditions:  $T_A = 25^\circ$  C to  $70^\circ$  C  $^{(1)}$ ,  $V_{CC} = 4.5$  V to 6.5 V  $^{(2)}$ ,  $V_{SS} = 0$  V  $^{(3)}$ ; unless otherwise noted

| Symbol             | Characteristic                | Min   | Typ (4) | Max  | Units | Conditions                  |

|--------------------|-------------------------------|-------|---------|------|-------|-----------------------------|

| FS                 | Internal Clock Sampling Freq. |       | 8       |      | KHz   |                             |

| BW                 | Passband <sup>(5)</sup>       |       | 3400    |      | Hz    |                             |

| THD                | Total Harmonic Distortion     |       | 1       |      | %     | @1 KHz                      |

| P <sub>OUT</sub>   | Speaker Output Power          |       |         | 50   | mW    | $R_{EXT} = 16 \Omega^{(6)}$ |

| V <sub>OUT</sub>   | Voltage Across Speaker Pins   |       |         | 2.5  | V p-p | $R_{\rm EXT} = 600  \Omega$ |

| $V_{IN1}$          | Mic Input Voltage             |       |         | 20   | mV    | Peak-to-Peak <sup>(7)</sup> |

| V <sub>IN2</sub>   | Ana In Input Voltage          |       |         | 50   | mV    | Peak-to-Peak                |

| $V_{IN3}$          | Aux In Input Voltage          |       |         | 1.25 | V p-p | $R_{\rm EXT} = 16 \Omega$   |

| $T_{SET}$          | Control/Address Setup Time    | 300   |         |      | nsec  |                             |

| $T_{HOLD}$         | Control/Address Hold Time     | 0     |         |      | nsec  |                             |

| T <sub>CE</sub>    | CE Pulse Width                | 100   |         |      | nsec  |                             |

| $T_{\mathrm{PUD}}$ | Power-Up Delay                | 18.75 |         |      | msec  |                             |

| $T_{PDR}$          | PD Pulse Width - Record       |       | 25      |      | msec  |                             |

| $T_{PDP}$          | PD Pulse Width - Play         |       | 12.5    |      | msec  |                             |

| $T_{PDS}$          | PD Pulse Width - Static       |       | 100     |      | nsec  |                             |

| $T_{PDH}$          | Power Down Hold               | 0     |         |      | nsec  |                             |

| $T_{REC}$          | Record Time                   |       | 16      |      | sec   |                             |

| $T_{PLAY}$         | Playback Time                 |       | 16      |      | sec   |                             |

| T <sub>EOM</sub>   | EOM Pulse Width               | -     | 12.5    |      | msec  |                             |

Notes: 1. Case temperature. 2.  $V_{CC} = V_{CCA} = V_{CCD}$ . 3.  $V_{SS} = V_{SSA} = V_{SSD}$ . 4. Typical values @  $T_A = 25^{\circ}$  C and 5.0 V. 5. Low-frequency cutoff depends upon value of external capacitors (see Pin Descriptions). 6. From AUX IN; if ANA IN is driven at 50 mV p-p, the  $P_{OUT} = 12.2$  mW, typical. 7. With 12 K $\Omega$  series resistor at ANA IN.

**ISD1000A SERIES**

- DATA SHEET -

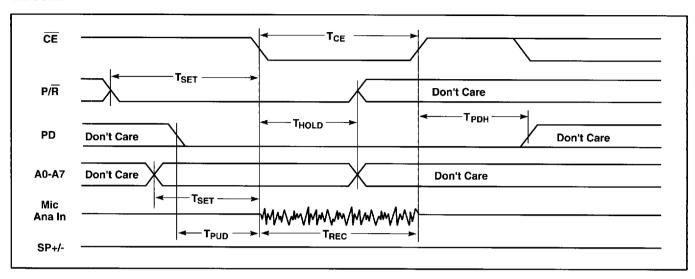

# **TIMING DIAGRAMS (ISD1016A)**

# **RECORD**

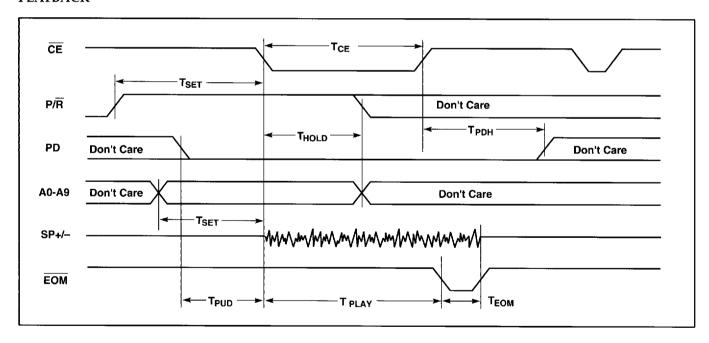

# **PLAYBACK**

DATA SHEET

# AC PARAMETERS (ISD1020A — 20-SECOND DURATION)

Operating Conditions:  $T_A = 25^{\circ}$  C to  $70^{\circ}$  C  $^{(1)}$ ,  $V_{CC} = 4.5$  V to 6.5 V  $^{(2)}$ ,  $V_{SS} = 0$  V  $^{(3)}$ ; unless otherwise noted

| Symbol            | Characteristic                | Min   | Typ (4) | Max  | Units | Conditions                           |

|-------------------|-------------------------------|-------|---------|------|-------|--------------------------------------|

| FS                | Internal Clock Sampling Freq. |       | 6.4     |      | KHz   |                                      |

| BW                | Passband (3)                  |       | 2700    |      | Hz    |                                      |

| THD               | Total Harmonic Distortion     |       | 1       |      | %     | @1 KHz                               |

| P <sub>OUT</sub>  | Speaker Output Power          |       |         | 50   | mW    | $R_{\text{EXT}} = 16 \ \Omega^{(6)}$ |

| V <sub>OUT</sub>  | Voltage Across Speaker Pins   |       |         | 2.5  | V p-p | $R_{\text{EXT}} = 600 \ \Omega$      |

| V <sub>IN1</sub>  | Mic Input Voltage             |       |         | 20   | mV    | Peak-to-Peak (7)                     |

| V <sub>IN2</sub>  | Ana In Input Voltage          |       |         | 50   | mV    | Peak-to-Peak                         |

| V <sub>IN3</sub>  | Aux In Input Voltage          |       |         | 1.25 | V p-p | $R_{\rm EXT} = 16 \Omega$            |

| T <sub>SET</sub>  | Control/Address Setup Time    | 300   |         |      | nsec  |                                      |

| T <sub>HOLD</sub> | Control/Address Hold Time     | 0     |         |      | nsec  |                                      |

| T <sub>CE</sub>   | CE Pulse Width                | 100   |         |      | nsec  |                                      |

| T <sub>PUD</sub>  | Power-Up Delay                | 31.25 |         |      | msec  |                                      |

| T <sub>PDR</sub>  | PD Pulse Width - Record       |       | 31.25   |      | msec  |                                      |

| T <sub>PDP</sub>  | PD Pulse Width - Play         |       | 15.625  |      | msec  |                                      |

| T <sub>PDS</sub>  | PD Pulse Width - Static       |       | 100     |      | nsec  |                                      |

| T <sub>PDH</sub>  | Power Down Hold               | 0     |         |      | nsec  |                                      |

| T <sub>REC</sub>  | Record Time                   |       | 20      |      | sec   |                                      |

| T <sub>PLAY</sub> | Playback Time                 |       | 20      |      | sec   |                                      |

| T <sub>EOM</sub>  | EOM Pulse Width               |       | 15.6    |      | msec  |                                      |

Notes: 1. Case temperature.

1. Cuse temperature. 2.  $V_{CC} = V_{CCA} = V_{CCD}$ . 3.  $V_{SS} = V_{SSA} = V_{SSD}$ . 4. Typical values @  $T_A = 25^{\circ}$  C and 5.0 V.

5. Low-frequency cutoff depends upon value of external capacitors

(see Pin Descriptions).

6. From AUX IN; if ANA IN is driven at 50 mV p-p, the  $P_{OUT} = 12.2$  mW, typical.

7. With 12 K $\Omega$  series resistor at ANA IN

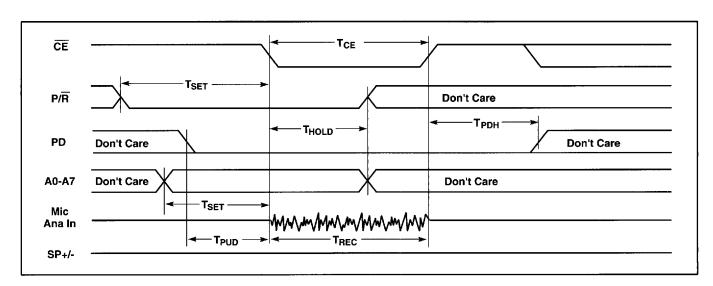

# **TIMING DIAGRAMS (ISD1020A)**

**RECORD**

- DATA SHEET

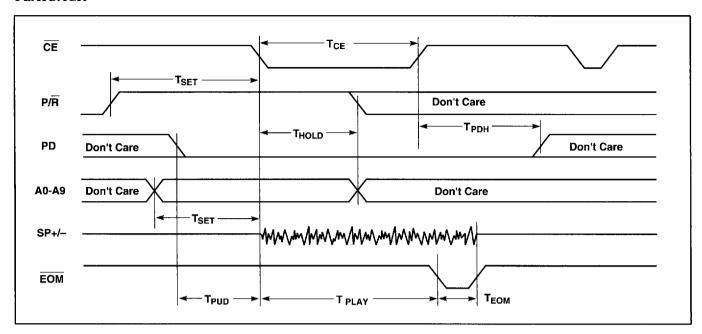

# **TIMING DIAGRAMS (ISD1020A, CONT.)**

# **PLAYBACK**

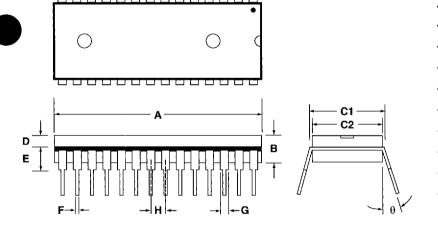

# **PACKAGE DIAGRAMS**

28-Lead Plastic Dual In-Line Package (DIP) Type P

|    | INCHES |       |       | MILLIMETERS |       |       |  |  |

|----|--------|-------|-------|-------------|-------|-------|--|--|

|    | Min    | Nom   | Max   | Min         | Nom   | Max   |  |  |

| A  | 1.445  | 1.450 | 1.455 | 36.7        | 36.83 | 36.95 |  |  |

| В  |        | .150  |       |             | 3.89  |       |  |  |

| C1 | .600   |       | .625  | 15.24       |       | 15.88 |  |  |

| C2 | .530   | .540  | .550  | 13.46       | 13.72 | 13.97 |  |  |

| D  | 1.25   | 1.30  | 1.35  | <br>2.92    | 3.05  | 3.18  |  |  |

| Е  | .125   | .130  | .135  | 3.18        |       | 3.43  |  |  |

| F  | .015   | .018  | .022  | 0.38        | 0.46  | 0.56  |  |  |

| G  | .055   | .060  | .065  | 1.40        | 1.52  | 1.65  |  |  |

| Н  |        | .100  |       |             | 2.54  |       |  |  |

| θ  | 0°     | 7°    | 15°   | 0°          | 7°    | 15°   |  |  |

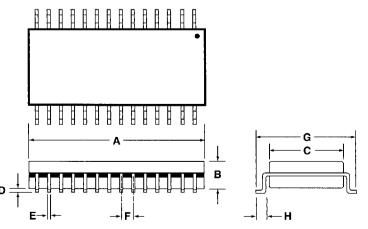

# 28-Lead Plastic Small Outline Package (SOIC) Type G

|   |      | NCHE<br>  Nom | _    |       | LIMET<br>Nom  |       |

|---|------|---------------|------|-------|---------------|-------|

| A | .706 | .714          | .718 | 17.93 | 18.14         | 18.24 |

| В | .086 | .088          | .090 | 2.18  | 2.24          | 2.29  |

| С | .340 | .346          | .350 | 8.64  | 8.79          | 8.89  |

| D | .004 | .007          | .010 | .102  | .178          | .254  |

| E | .014 | .016          | .020 | .360  | .410          | .480  |

| F |      | .050          |      |       | 1.27          |       |

| G | .463 | .470          | .477 | 11.76 | 12.00         | 12.12 |

| Н | .020 | .031          | .042 | .510  | . <b>7</b> 90 | 1.07  |

| _     |    |   | _ |   | _ |    |  |

|-------|----|---|---|---|---|----|--|

| - 1 3 | ΔΙ | Δ |   | н | - | ьι |  |

#### **ORDERING INFORMATION**

When placing an order for the ISD1000A Series devices, please refer to the following part numbers:

| Part No.                                                                                      | Rec/Play Duration  | Description                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISD1016AP<br>ISD1016API<br>ISD1016APL*<br>ISD1016AG<br>ISD1016AGI<br>ISD1016AGL*<br>ISD1016AX | 16 sec.<br>16 sec. | 28-pin plastic dual in-line package (DIP) Industrial Temperature, -40°C to 85°C (DIP) Low Voltage, 3.6 V to 4.0 V (DIP) 28-lead small-outline integrated circuit (SOIC) Industrial Temperature, -40°C to 85°C (SOIC) Low Voltage, 3.6 V to 4.0 V (SOIC) Bare unpackaged die |

| ISD1020AP<br>ISD1020API<br>ISD1016APL*<br>ISD1020AG<br>ISD1020AGI<br>ISD1016AGL*              | 20 sec.<br>20 sec. | 28-pin plastic dual in-line package (DIP) Industrial Temperature, -40°C to 85°C (DIP) Low Voltage, 3.6 V to 4.0 V (DIP) 28-lead small-outline integrated circuit (SOIC) Industrial Temperature, -40°C to 85°C (SOIC) Low Voltage, 3.6 V to 4.0 V (SOIC)                     |

<sup>\*</sup> Note: Please contact your ISD Sales Office or Representative for ISD1000A"L" (Low Voltage) Data Sheet Addendum.

#### **IMPORTANT NOTICES**

THE WARRANTY FOR EACH PRODUCT OF INFORMATION STORAGE DEVICES, INC. IS CONTAINED IN A WRITTEN WARRANTY WHICH GOVERNS SALE AND USE OF SUCH PRODUCT. SUCH WARRANTY IS CONTAINED IN THE PRINTED TERMS AND CONDITIONS UNDER WHICH SUCH PRODUCT IS SOLD, OR IN A SEPARATE WRITTEN WARRANTY SUPPLIED WITH THE PRODUCT. PLEASE REFER TO SUCH WRITTEN WARRANTY WITH RESPECT TO ITS APPLICABILITY TO CERTAIN APPLICATIONS OF SUCH PRODUCT.

The ISD products described herein may not be used or resold for use in recordable greeting cards, i.e., articles, usually constructed of paper or cardboard (but not limited to these materials), that include artwork (including pre-imprinted or customer-affixed photographs or artwork) and/or editorials that have the look and feel of greeting cards and are able to be inserted into an envelope (but do not necessarily need to be so inserted) and primarily intended to be presented or delivered to an individual as a greeting card, that allow the sender to record and the recipient to play back an audio signal message.

The ISD products described herein are subject to an exclusive arrangement with one or more third parties which provides that such ISD products may not be sold for use by any person, other than such third party(ies) in recordable ornaments, i.e., decorative ornaments intended to be sold separately at retail, primarily designed and marketed for decorating the interior of residences at the Christmas or Easter season that allow a person to record and play back an audio signal message.

The products described herein are subject to an exclusive license to a third party which provides that such products may not be used or sold for use by any person other than such licensee in the field of implantable medical devices to be used in connection with the cardiovascular, muscular, or neurological systems of the human and animal body, or in external devices used to program or monitor such implantable medical devices, including but not limited to programmers, pacing system analyzers, defibrillation system analyzers, monitors, and transtelephonic medical equipment.

THESE PRODUCTS MAY BE SUBJECT TO FURTHER RESTRICTIONS ON USE OR RESALE. PLEASE CONTACT INFORMATION STORAGE DEVICES, INC. FOR A LIST OF THE CURRENT ADDITIONAL RESTRICTIONS ON THESE PRODUCTS. BY PURCHASING THESE PRODUCTS, THE PURCHASER OF THESE PRODUCTS AGREES TO COMPLY WITH SUCH RESTRICTIONS. PLEASE CONTACT ISD FOR CLARIFICATION OF ANY RESTRICTIONS DESCRIBED HEREIN.

Information Storage Devices ("ISD") reserves the right without further notice to change the ISD1000A Series product specifications identified in this publication to improve reliability, function, or design.

The 100-year retention and 100K record cycle projections are based upon accelerated reliability tests, as published in the ISD Reliability Report, and are neither warranteed nor guaranteed by ISD.

ISD assumes no responsibility or liability for any use of the ISD1000A Series products. ISD conveys no license or title, either expressed or implied, under any patent, copyright, or mask work right to the ISD1000A Series products, and ISD makes no warranties or representations that the ISD1000A Series products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Applications described in this publication are for illustrative purposes only, and ISD makes no warranties or representations that the ISD1000A Series products will be suitable for such applications.

Information contained in this ISD1000A Series product specification supersedes all data for the ISD1000A Series products published by ISD prior to October, 1993.

CORPORATE HEADQUARTERS 2841 Junction Avenue San Jose, CA 95134 TEL: 408/428-1400 FAX: 408/428-1422 ISD is registered by the U.S. Patent and Trademark Office. DAST and ChipCorder are trademarks of Information Storage Devices, Inc.

© 1993 INFORMATION STORAGE DEVICES, INC. ALL RIGHTS RESERVED