# 2164A FAMILY 65,536 × 1 BIT DYNAMIC RAM

|                                  | 2164A·15 | 2164A-20 |

|----------------------------------|----------|----------|

| Maximum Access Time (ns)         | 150      | 200      |

| Read, Write Cycle (ns)           | 260      | 330      |

| Page Mode Read, Write Cycle (ns) | 125      | 170      |

- HMOS-D III technology

- Low capacitance, fully TTL compatible inputs and outputs

- Single +5V supply, ±10% tolerance

- 128 refresh cycle/2 ms RAS only refresh

- Compatible with the 2118

- Extended page mode, read-modifywrite and hidden refresh operation

- Inputs allow a 2.0V negative overshoot

- Industry standard 16-pin DIP

- Compatible with Intel's microprocessors and DRAM controllers

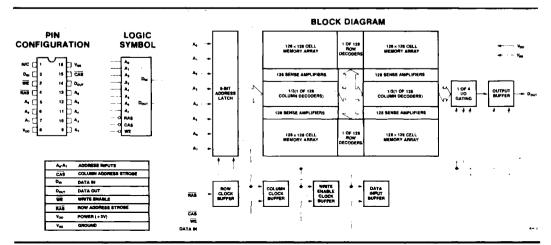

The 2164A is a 65,536 word by 1-bit N-channel MOS dynamic Random Access Memory fabricated with Intel's HMOS-D III technology for high system performance and reliability. The 2164A design incorporates high storage cell capacitance to provide wide internal device margins for reduced noise sensitivities and more reliable system operation. Moreover, high storage cell capacitance results in low soft error rates without the need for a die coat. HMOS-D III process employs the use of redundant elements.

The 2164A is optimized for high speed, high performance applications such as mainframe memory, buffer memory, microprocessor memory, peripheral storage and graphic terminals. For memory intensive microprocessor applications the 2164A is fully compatible with Intel's DRAM controllers and microprocessors to provide a complete DRAM system.

Multiplexing the 16 address bits into the 8 address input pins allows the 2164A to achieve high packing density. The 16 pin DIP provides for high system bit densities, and is compatible with widely available automated testing and insertion equipment. The two 8-bit TTL level address segments are latched into the 2164A by the two TTL clocks, Row Address Strobe (FAS) and Column Address Strobe (CAS). Non-critical timing requirements for the RAS and CAS clocks allow the use of the address multiplexing technique while maintaining high performance.

The non-latched, three state, TTL compatible data output is controlled by  $\overline{CAS}$ , independent of  $\overline{RAS}$ . After a valid read or read-modify-write cycle, data is held on the data output pin by holding  $\overline{CAS}$  low. The data output is returned to a high impedance state, by returning  $\overline{CAS}$  to a high state. Hidden refresh capability allows the device to maintain data at the output by holding  $\overline{CAS}$  low while  $\overline{RAS}$  is used to execute  $\overline{RAS}$ -only refresh cycles. Refreshing is accomplished by performing  $\overline{RAS}$ -only cycles, hidden refresh cycles, or normal read or write cycles on the 128 address combinations of addresses  $A_0$  through  $A_6$ , during a 2 ms period.

## **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature                                   |

|-------------------------------------------------------|

| Under Bias 10 °C to + 80 °C                           |

| Storage Temperature Cerdip - 65 °C to + 150 °C        |

| Plastic - 55°C to + 125°C                             |

| Voltage on Any Pin except V <sub>DD</sub>             |

| Relative to V <sub>SS</sub>                           |

| Voltage on $V_{DD}$ Relative to $V_{SS}$ 1.0V to 7.5V |

| Data Out Current 50 mA                                |

| Power Dissipation 1.0 W                               |

#### \*COMMENT:

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## D.C. AND OPERATING CHARACTERISTICS[1]

$T_A = 0$ °C to 70°C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

|                  |                                                           |       | Limits              |      |      |                                                                           |       |

|------------------|-----------------------------------------------------------|-------|---------------------|------|------|---------------------------------------------------------------------------|-------|

| Symbol           | Parameter                                                 | Min.  | Typ. <sup>[2]</sup> | Max. | Unit | · ·                                                                       | Notes |

| lu               | Input Load Current (any input)                            |       |                     | 10   | μÄ   | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>DD</sub>                      |       |

| llo              | Output Leakage Current for<br>High Impedance State        |       | -                   | 10   | μА   | Chip Deselected: CAS at V <sub>IH</sub> ,<br>D <sub>OUT</sub> = 0 to 5.5V |       |

| I <sub>DD1</sub> | V <sub>DD</sub> Supply Current, Standby                   |       | 3.                  | 5    | mA   | CAS and RAS at VIH                                                        |       |

|                  | V. Sundh Current Oneretine                                |       | 42                  | 55   | mA   | 2164A-15, t <sub>RC</sub> = t <sub>RCMIN</sub>                            | 3     |

| DD2              | V <sub>DD</sub> Supply Current, Operating                 |       | 33                  | 45   | mA-  | 2164A-20, t <sub>RC</sub> = t <sub>RCMIN</sub>                            | 3     |

|                  | V <sub>DD</sub> Supply Current, RAS-Only                  | 1     | 30                  | 45   | mA   | 2164A-15, t <sub>RC</sub> = t <sub>RCMIN</sub>                            |       |

| DD3              | Cycle                                                     |       | 24                  | 40   | mA   | 2164A-20, t <sub>RC</sub> = t <sub>RCMIN</sub>                            |       |

| I <sub>DD5</sub> | V <sub>DD</sub> Supply Current, Standby<br>Output Enabled |       |                     | 6    | mA   | CAS at V <sub>IL</sub> , RAS at V <sub>IH</sub>                           | 3     |

| V <sub>IL</sub>  | Input Low Voltage (all inputs)                            | - 1.0 |                     | 0.8  | V    |                                                                           | 4.    |

| V <sub>IH</sub>  | Input High Voltage (all inputs)                           | 2.4   |                     | 7.0  | V    |                                                                           |       |

| V <sub>OL</sub>  | Output Low Voltage                                        | T     |                     | 0.4  | ٧    | 1 <sub>OL</sub> = 4.2 mA                                                  | 5     |

| V <sub>OH</sub>  | Output High Voltage                                       | 2.4   |                     |      | V    | I <sub>OH</sub> = -5 mA                                                   | 5     |

#### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. Typical values are for T<sub>A</sub> = 25 °C and nominal supply voltages.

- 3. IDD is dependent on output loading when the device output is selected. Specified IDD MAX is measured with the output open.

- 4. Specified V<sub>II, MIN</sub> is for steady state operation. During transitions the inputs may overshoot to -2.0V for periods not to exceed 20 ns.

- 5. Test conditions apply only for D.C. characteristics. A.C. parameters specified with a load equivalent to 2 TTL loads and 100 pF.

#### CAPACITANCE[1]

$T_A = 25$  °C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

| Symbol          | Parameter        | Тур. | Max. | Unit |

|-----------------|------------------|------|------|------|

| C <sub>11</sub> | Address, Data In | 3    | 5    | p₹   |

| C <sub>12</sub> | WE, Data Out     | 3    | 6    | рF   |

| C <sub>13</sub> | RAS, CAS         | 4    | 8    | pF   |

#### NOTES:

Capacitance measured with Boonton Meter or effective capacitance calculated from the equation;

$$C = \frac{1\Delta t}{\Delta V}$$

with  $\Delta V$  equal to 3 volts and power supplies at nominal levels.

## A.C. CHARACTERISTICS [1,2,3]

$T_A = 0$  °C to 70 °C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

#### READ, WRITE, READ-MODIFY-WRITE AND REFRESH CYCLES

|                  |                                      | 2164 | IA-15 | 2164 | IA-20 |      |       |

|------------------|--------------------------------------|------|-------|------|-------|------|-------|

| Symbol           | Parameter                            | Min. | Max.  | Min. | Max.  | Unit | Notes |

| t <sub>RAC</sub> | Access Time From RAS                 |      | 150   |      | 200   | ns   | 4,5   |

| t <sub>CAC</sub> | Access Time From CAS                 |      | 85    |      | 120   | ns   | 5,6   |

| t <sub>REF</sub> | Time Between Refresh                 |      | 2     |      | 2     | ms   |       |

| t <sub>RP</sub>  | RAS Precharge Time                   | 100  |       | 120  |       | ns   |       |

| tCPN             | CAS Precharge Time (non-page cycles) | 25   | _     | 35   | _     | ns   |       |

| t <sub>CRP</sub> | CAS to RAS Precharge Time            | - 20 |       | - 20 |       | กร   |       |

| t <sub>RCD</sub> | RAS to CAS Delay Time                | 30   | 65    | 35   | 80    | ns   | 7     |

| t <sub>RSH</sub> | RAS Hold Time                        | 85   |       | 120  |       | กร   |       |

| t <sub>CSH</sub> | CAS Hold Time                        | 150  |       | 200  |       | ns   |       |

| t <sub>ASR</sub> | Row Address Set-Up Time              | 0    |       | . 0  |       | ns   |       |

| tRAH             | Row Address Hold Time                | 20   |       | 25   |       | ns   |       |

| 1 <sub>ASC</sub> | Column Address Set-Up Time           | 0    |       | ō    |       | ns   |       |

| t <sub>CAH</sub> | Column Address Hold Time             | 25   |       | 30   |       | ns   |       |

| t <sub>AR</sub>  | Column Address Hold Time to RAS      | 90   |       | 110  |       | ns   |       |

| t <sub>T</sub>   | Transition time (Rise and Fall)      | 3    | 50    | 3    | 50    | กร   | 8     |

| toff             | Output Buffer Turn Off Delay         | 0    | 30    | 0    | 40    | ns   | 1     |

#### **READ AND REFRESH CYCLES**

| t <sub>RC</sub>  | Random Read Cycle Time                   | 260 |       | 330 |       | ns |   |

|------------------|------------------------------------------|-----|-------|-----|-------|----|---|

| t <sub>RAS</sub> | RAS Pulse Width                          | 150 | 10000 | 200 | 10000 | ns |   |

| t <sub>CAS</sub> | CAS Pulse Width                          | 85  | 10000 | 120 | 10000 | ns |   |

| t <sub>RCS</sub> | Read Command Set-Up Time                 | 0   |       | 0   |       | กร |   |

| t <sub>BCH</sub> | Read Command Hold Time referenced to CAS | 5   |       | 5   |       | ns | 9 |

| t <sub>BBH</sub> | Read Command Hold Time referenced to RAS | 20  |       | 20  |       | ns | 9 |

#### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. An initial pause of 500  $\mu$ s is required after power up followed by a minimum of eight (8) initialization cycles (any combination of cycles containing a RAS clock such as RAS-only refresh). 8 initialization cycles are required after extended periods of bias (greater than 2 ms) without clocks.

- 3. A.C. Characteristics assume  $t_T = 5$  ns.

- 4. Assumes that  $t_{RCD} \le t_{RCD}$  (max). If  $t_{RCD}$  is greater than  $t_{RCD}$  (max) then  $t_{RAC}$  will increase by the amount that  $t_{RCD}$  exceeds  $t_{RCD}$  (max).

- 5. Load = 2 TTL loads and 100 pF.

- 6. Assumes  $t_{RCD} \ge t_{RCD}(max)$ .

- t<sub>RCD</sub>(max) is specified as a reference point only. If t<sub>RCD</sub> is less than t<sub>RCD</sub>(max) access time is t<sub>RCD</sub>. If t<sub>RCD</sub> is greater than t<sub>RCD</sub>(max) access time is t<sub>RCD</sub> + t<sub>CAC</sub>. t<sub>RCD</sub>(min) = t<sub>RAH</sub> + t<sub>ASC</sub> + t<sub>T</sub> + t<sub>T</sub> (t<sub>T</sub> = 5 ns).

- 8. t<sub>T</sub> is measured between V<sub>IH</sub>(min) and V<sub>IL</sub>(max).

- 9. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

## A.C. CHARACTERISTICS (con't.)

#### WRITE CYCLE

|                  |                                | 2164 | 2164A-15 2164A-20 |      |       |      |       |

|------------------|--------------------------------|------|-------------------|------|-------|------|-------|

| Symbol           | Parameter                      | Min. | Max.              | Min. | Max.  | Unit | Notes |

| tRC              | Random Write Cycle Time        | 260  |                   | 330  |       | ns   |       |

| TRAS             | RAS Pulse Width                | 150  | 10000             | 200  | 10000 | ns   |       |

| t <sub>CAS</sub> | CAS Pulse Width                | 85   | 10000             | 120  | 10000 | ns   |       |

| twcs,            | Write Command Set-Up Time      | - 10 |                   | - 10 |       | ns   | 10    |

| t <sub>WCH</sub> | Write Command Hold Time        | 30   |                   | 40   |       | ns   |       |

| twcn             | Write Command Hold Time to RAS | 95   |                   | 120  |       | ns   |       |

| twp              | Write Command Pulse Width      | 30   |                   | 40   |       | ns   |       |

| t <sub>RWL</sub> | Write Command to RAS Lead Time | 40   |                   | 50   |       | ns   |       |

| tcwL             | Write Command to CAS Lead Time | 40   |                   | 50   |       | ns   |       |

| tos              | Data-In Set-Up Time            | 0    |                   | 0    | •     | ns   |       |

| t <sub>DH</sub>  | Data-In Hold Time              | 30   |                   | 40   |       | ns   |       |

| t <sub>DHR</sub> | Data-In Hold Time to RAS       | 95   |                   | 120  |       | ns   |       |

#### **READ-MODIFY-WRITE CYCLE**

| tRWC             | Read-Modify-Write Cycle time | 280 |       | 355 |       | ns | ** |

|------------------|------------------------------|-----|-------|-----|-------|----|----|

| t <sub>RRW</sub> | RMW Cycle RAS Pulse Width    | 170 | 10000 | 225 | 10000 | ns |    |

| terw             | RMW Cycle CAS Pulse Width    | 105 | 10000 | 145 | 10000 | ns |    |

| t <sub>RWD</sub> | RAS to WE Delay              | 125 |       | 170 |       | ns | 10 |

| tcwp             | CAS to WE Delay              | 60  |       | 90  |       | ns | 10 |

#### NOTES:

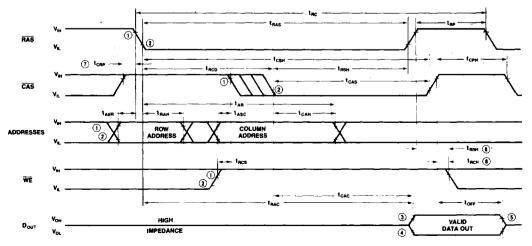

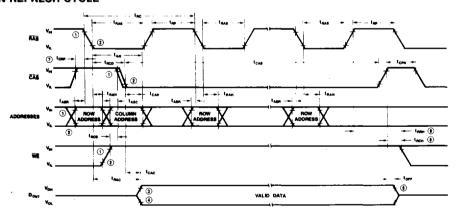

## **WAVEFORMS**

#### **READ CYCLE**

<sup>10.</sup> t<sub>WCS</sub>, t<sub>CWD</sub> and t<sub>RWD</sub> are specified as reference points only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub>(min) the cycle is an early write cycle and the data out pin will remain high impedance throughout the entire cycle. If t<sub>CWD</sub> ≥ t<sub>CWD</sub>(min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub>(min) the cycle is a read-modify-write cycle and the data out will contain the data read from the selected address. If neither of the above conditions is satisfied, the condition of the data out is indeterminate.

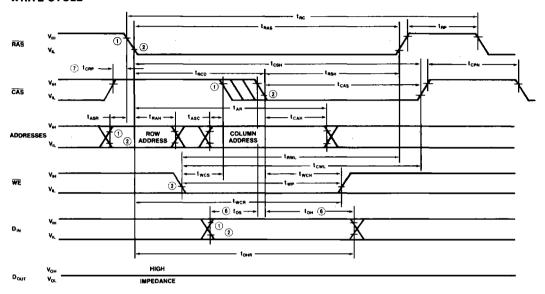

## **WAVEFORMS**

#### **WRITE CYCLE**

#### **READ-MODIFY-WRITE CYCLE**

- NOTES: 1,2. VIH MIN and VIL MAX are reference levels for measuring timing of input signals.

- 3.4. V<sub>OH MIN</sub> and V<sub>OL MAX</sub> are reference levels for measuring timing of D<sub>OUT</sub>.

5. t<sub>OFF</sub> is measured to l<sub>OUT</sub> ≤ |l<sub>CO</sub>|.

6. t<sub>DS</sub> and t<sub>DH</sub> are referenced to CAS or WE, whichever occurs last.

- 7. t<sub>CRP</sub> requirement is only applicable for RAS/CAS cycles preceded by a CAS-only cycle (i.e., for systems where CAS has not been decoded with RAS).

- 8. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

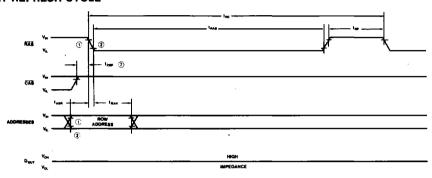

#### **WAVEFORMS**

#### **RAS-ONLY REFRESH CYCLE**

#### **HIDDEN REFRESH CYCLE**

NOTES: 1,2.  $V_{IH\ MIN}$  and  $V_{IL\ MAX}$  are reference levels for measuring timing of input signals.

- 3.4. V<sub>OH MIN</sub> and V<sub>OL MAX</sub> are reference levels for measuring timing of D<sub>DUT</sub>.

3.4. V<sub>OH MIN</sub> and V<sub>OL MAX</sub> are reference levels for measuring timing of D<sub>DUT</sub>.

3.4. t<sub>OH</sub> is measured to l<sub>OUT</sub> ≤ |t<sub>LO</sub>|.

6. t<sub>DS</sub> and t<sub>DH</sub> are referenced to CAS or WE, whichever occurs last.

7. t<sub>CRP</sub> requirement is only applicable for RAS/CAS cycles preceded by a CAS-only cycle (i.e., for systems where CAS has not been decoded with RAS).

- 8. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

## D.C. AND A.C. CHARACTERISTICS, PAGE MODE [6,7,11]

$T_A = 0$  °C to 70 °C,  $V_{DD} = 5V \pm 10$  %,  $V_{SS} = 0V$ , unless otherwise noted.

|                   |                                                                                                 | 2164A |       | 216  | 4A-20 |      |       |

|-------------------|-------------------------------------------------------------------------------------------------|-------|-------|------|-------|------|-------|

| Symbol            | Parameter                                                                                       | Min.  | Max.  | Min. | Max.  | Unit | Notes |

| t <sub>PC</sub>   | Page Mode Read or Write Cycle                                                                   | 125   | _     | 170  |       | ns   |       |

| t <sub>PCM</sub>  | Page Mode Read Modify Write                                                                     | 145   |       | 195  |       | ns   |       |

| t <sub>CP</sub>   | CAS Precharge Time, Page Cycle                                                                  | 30    |       | 40   |       | ns   |       |

| t <sub>RPM1</sub> | RAS Pulse Width, Page Mode                                                                      |       | 10000 |      | 10000 | ns   |       |

| tCAS              | CAS Pulse Width                                                                                 | 85    | 10000 | 120  | 10000 | ns   |       |

| I <sub>DD4</sub>  | V <sub>DD</sub> Supply Current Page Mode,<br>Minimum t <sub>PC</sub> , Minimum t <sub>CAS</sub> |       | 40    |      | 35    | mA   | 8     |

## EXTENDED PAGE MODE[11,12]

|                   |                                     | 2164A-15<br>S6493 |       |      | IA-20<br>494 |      |       |

|-------------------|-------------------------------------|-------------------|-------|------|--------------|------|-------|

| Symbol            | Parameter                           | Min.              | Max.  | Min. | Max.         | Unit | Notes |

| t <sub>RPM2</sub> | RAS Pulse Width, Extended Page Mode |                   | 75000 |      | 75000        | ns   |       |

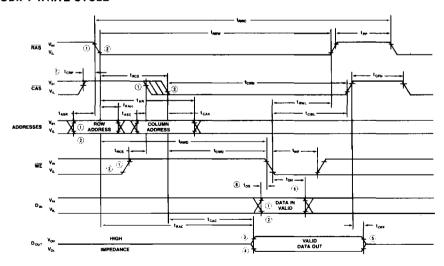

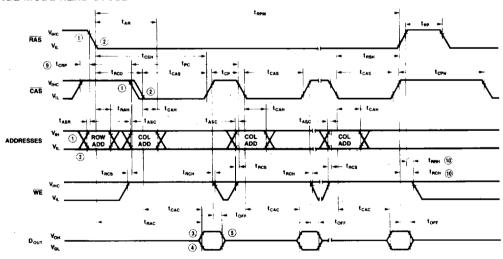

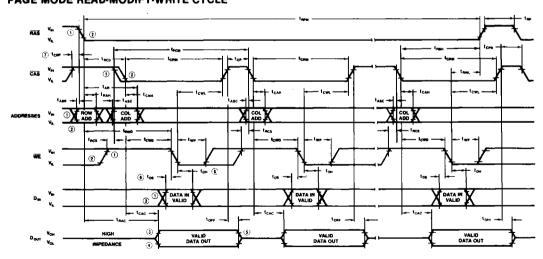

#### **WAVEFORMS**

#### PAGE MODE READ CYCLE

NOTES: 1,2.  $V_{IH\ MIN}$  and  $V_{IL\ MAX}$  are reference levels for measuring timing of input signals.

- 3.4. V<sub>OH MIN</sub> and V<sub>OL MAX</sub> are reference levels for measuring timing of D<sub>OUT</sub>.

5. t<sub>OFF</sub> is measured to l<sub>OUT</sub> ≤ | l<sub>LO</sub>.

- 6. All voltages referenced to V<sub>SS</sub>.

- 7. A.C. characteristic assume  $t_T = 5$  ns.

- 8. See the typical characteristics section for values of this parameter under alternate conditions.

- 9. t<sub>CRP</sub> requirement is only applicable for RAS/CAS cycles preceded by a CAS-only cycle (i.e., for systems where CAS has not been decoded with RAS).

- 10. Either tech or teen must be satisfied.

- 11. All previously specified A.C. and D.C. characteristics are applicable.

- 12. For extended page mode operation, order 2164A-15 S6493, 2164A-20 S6494.

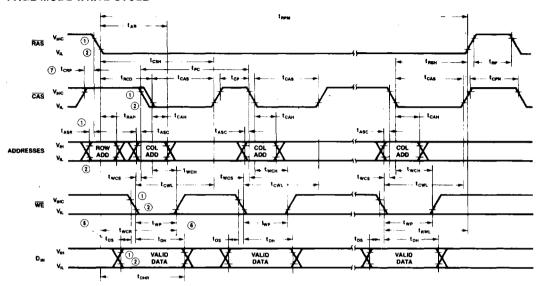

#### **WAVEFORMS**

#### PAGE MODE WRITE CYCLE

## PAGE MODE READ-MODIFY-WRITE CYCLE

NOTES: 1,2.  $V_{IH\ MIN}$  and  $V_{IL\ MAX}$  are reference levels for measuring timing of input signals.

- 3,4. V<sub>OH MIN</sub> and V<sub>OL MAX</sub> are reference levels for measuring timing of D<sub>OUT</sub>.

- 5. t<sub>OFF</sub> is measured to I<sub>OUT</sub> ≤ I<sub>LO</sub>].

6. t<sub>OS</sub> and t<sub>DH</sub> are referenced to <del>CAS</del> or <del>WE</del>, whichever occurs last.

7. t<sub>CRP</sub> requirement is only app<u>licable for <del>RAS/CAS</del></u> cycles preceded by a <del>CAS</del>-only cycle (i.e., for systems where <del>CAS</del> has not been decoded with RAS).

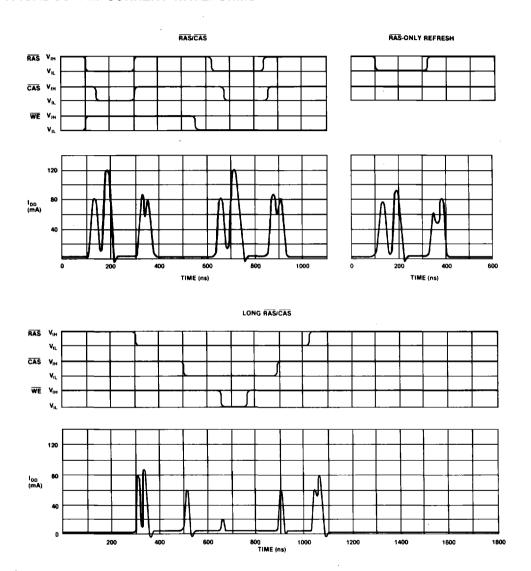

#### TYPICAL SUPPLY CURRENT WAVEFORMS

Typical power supply waveforms vs. time are shown for the RAS/CAS timings of Read/Write, Read/Write (long RAS/CAS), and RAS-only refresh cycles. I<sub>DD</sub> current transients at the RAS and CAS edges require adequate decoupling of these supplies.

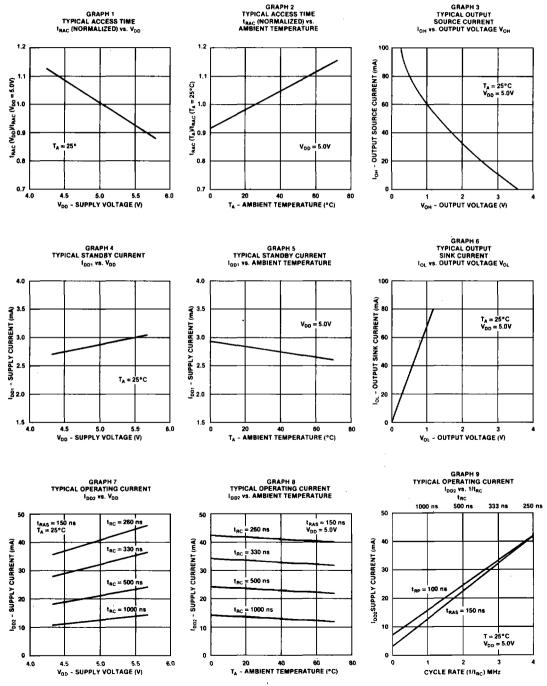

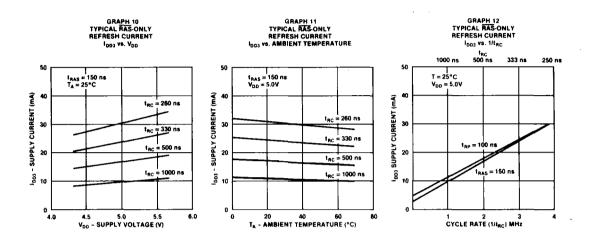

The effects of cycle time,  $V_{DD}$  supply voltage and ambient temperature on the  $I_{DD}$  current are shown

in graphs included in the Typical Characteristics Section. Each family of curves for  $I_{DD1},\,I_{DD2},\,$  and  $I_{DD3}$  is related by a common point at  $V_{DD}=5.0V$  and  $T_A=25\,^{\circ}\text{C}$  for  $t_{RAS}=150$  ns and  $t_{RC}=260$  ns. The typical  $I_{DD}$  current for a given condition of cycle time,  $V_{DD}$  and  $T_A$ , can be determined by combining the effects of the appropriate family of curves.

#### TYPICAL CHARACTERISTICS

## TYPICAL CHARACTERISTICS

#### **DEVICE DESCRIPTION**

The Intel 2164A is produced with HMOS-D III, a high performance MOS technology which incorporates redundant elements. This process, combined with new circuit design concepts, allows the 2164A to operate from a single + 5V power supply, eliminating the + 12V and - 5V requirements. Pin 1 is not connected, which allows P.C.B. layout for future higher density memory generations.

The 2164A is functionally compatible with the 2118, the industry standard 5V-only 16-pin 16K dynamic RAM. This allows simple upgrade from 16K to 64K density merely by adding one additional multiplexed address line.

## **RAS/CAS Timing**

RAS and CAS have minimum pulse widths as defined by t<sub>RAS</sub> and t<sub>CAS</sub> respectively. These minimum pulse widths must be maintained for proper device operation and data integrity. A cycle, once begun by bringing RAS and/or CAS low, must not be ended or aborted prior to fulfilling the minimum clock signal pulse width(s). A new cycle can not begin until the minimum precharge time, t<sub>RP</sub>, has been met.

## Read Cycle

A Read cycle is performed by maintaining Write Enable (WE) high during a RAS/CAS operation. The

output pin of a selected device will remain in a high impedance state until valid data appears at the output at access time.

## **Write Cycle**

A Write cycle is performed by taking WE low during a RAS/CAS operation. Data Input (D<sub>IN</sub> must be valid relative to the negative edge of WE or CAS, whichever transition occurs last.

## Refresh Cycles

There are 512 sense amplifiers, each controlling 128 storage cells. Thus, the 2164A is refreshed in 128 cycles. Any combination of the seven (7) low order Row Addresses RA<sub>0</sub> through RA<sub>6</sub>, will select two rows of data cells (256 cells/row). Row address 7 is not critical during a refresh operation and can be either high or low. Although any cycle, Read, Write, Read-Modify-Write, or RAS-only, will refresh the memory, the RAS-only cycle is recommended, since it allows about 20% system power reduction over the other types of cycles.

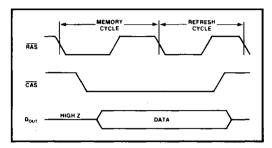

#### Hidden Refresh

A standard feature of the 2164A is that refresh cycles may be performed while maintaining valid data at the output pin. This is referred to as Hidden Refresh. Hidden Refresh is performed by holding CAS at V<sub>IL</sub> and taking RAS high and, after a specified precharge period (tap), executing a

"RAS-Only" refresh cycle, but with CAS held low (see figure below).

This feature allows a refresh cycle to be "hidden" among data cycles without affecting the data availability. The part will be internally refreshed at the row addressed at the time of the second RAS.

## **Data Output Operation**

The 2164A Data Output ( $D_{OUT}$ ), which has three-state capability, is controlled by  $\overline{CAS}$ . During  $\overline{CAS}$  high state ( $\overline{CAS}$  at  $V_{IH}$ ), the output is in the high impedance state. The following table summarizes the  $D_{OUT}$  state for various types of cycles.

Intel® 2164A Data Output Operation for Various Types of Cycles

| Type of Cycle           | D <sub>OUT</sub> State             |

|-------------------------|------------------------------------|

| Read Cycle              | Data from Addressed<br>Memory Cell |

| Early Write Cycle       | Hi-Z                               |

| RAS-Only Refresh Cycle  | Hi-Z                               |

| CAS-Only Cycle          | Hi-Z                               |

| Read-Modify-Write Cycle | Data from Addressed<br>Memory Cell |

| Delayed Write Cycle     | Indeterminate                      |

#### Power On

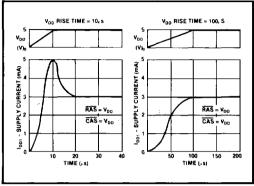

An initial pause of 500  $\mu s$  is required after the application of the  $V_{DD}$  supply, followed by a minimum of eight (8) initialization cycles (any combination of cycles containing a RAS clock such as RAS-only refresh). 8 initialization cycles are required after extended periods of bias (greater than 2 ms) without clocks. The  $V_{DD}$  current ( $I_{DD}$ ) requirement of the 2164A during power on, is however, dependent upon the input levels of RAS and CAS and the rise time of  $V_{DD}$  shown in Figure 1.

If  $\overline{\text{RAS}} = V_{\text{SS}}$  during power on, the device may go into an active cycle and  $I_{\text{DD}}$  would show spikes similar to those shown for the  $\overline{\text{RAS}}/\overline{\text{CAS}}$  timings. It

is recommended that  $\overline{RAS}$  and  $\overline{CAS}$  track with  $V_{DD}$  during power on or be held at a valid  $V_{IH}$ .

Figure 1. Typical IDD vs. VDD During Power Up

## **Page Mode Operation**

Page Mode operation allows additional columns of the selected device to be accessed at the common row address set. This is done by maintaining RAS low while successive CAS cycles are performed.

Page Mode operation allows a maximum data transfer rate as Row addresses are maintained internally and do not have to be reapplied. During this operation, Read, Write and Read-Modify-Write cycles are possible. Following the entry cycle into Page Mode operation, access is t<sub>CAC</sub> dependent. The Page Mode cycle is dependent upon CAS pulse width (t<sub>CAS</sub>) and the CAS precharge period (t<sub>CP</sub>).

## **Extended Page Mode Operation**

An optional feature of the 2164A is extended page mode operation which allows an entire page (row) of data to be read or written during a single  $\overline{\text{RAS}}$  cycle. By providing a fast  $t_{PC}$  and long  $\overline{\text{RAS}}$  pulse width ( $t_{\text{RPM2}}$ ), the 2164A-15 S6493 permits transfers of large blocks of data, such as required by bitmapped graphic applications.

#### SYSTEM DESIGN CONSIDERATIONS

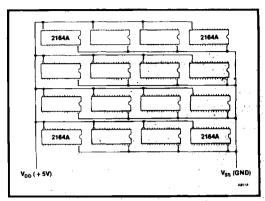

#### Ground and Power Gridding

Ground and power gridding can contribute to excess noise and voltage drops. An example of an unacceptable method is presented in Figure 2. This type of layout results in accumulated transient noise and voltage drops for the device located at the end of each trace (path).

Figure 2. Unacceptable Power Distribution

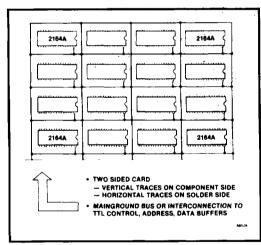

Transient effects can be minimized by adding extra circuit board traces in parallel to reduce interconnection inductance (Figure 3).

Figure 3. Recommended Power Distribution

— Gridding

#### **Power and Ground Plane**

A better alternative to power and gridding is power and ground planes. Although this requires two additional inner layers to the PC board, noise and supply voltage fluctuations are greatly reduced. If power and ground planes are used, gridding is optional but typically used for increased reliability of power and ground connections and further reduction of electromagnetic noise.

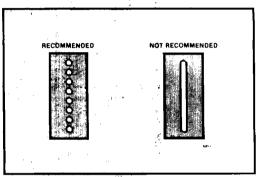

It is preferable on power/ground planes to use circular volds for device pins rather than slotted volds (Figure 4). This provides maximum decoupling and minimum crosstalk between signal traces.

Figure 4. Recommended Voids for Multilayer PC Boards

#### **Power Supply Decoupling**

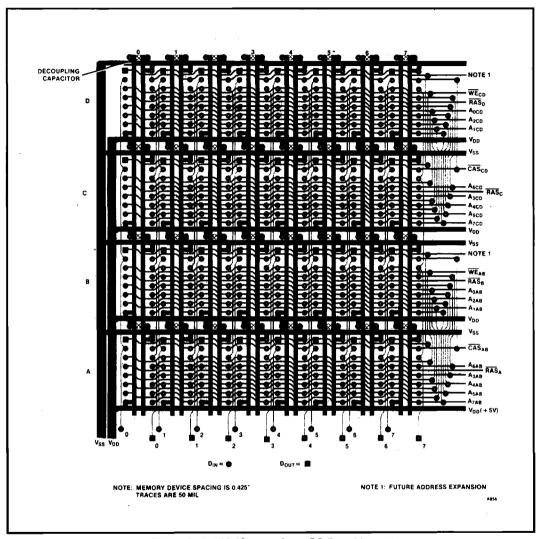

For best results, decoupling capacitors are placed on the memory array board at each memory location (Figure 5). High frequency 0.1  $\mu$ F ceramic capacitors are the recommended type. Noise is minimized because of the low impedance across the circuit board traces. Typical V<sub>DD</sub> noise levels for this arrangement are less than 300 mV.

A large tantalum capacitor (typically one 100  $\mu$ F per 64 devices) is required at the circuit board edge connector power input pins to recharge the 0.1  $\mu$ F capacitors between memory cycles.

For further details see application note (A.N.) #131, 2164A Dynamic RAM Device Description, or A.N. #133, Designing Memory Systems for Microprocessor Using the Intel 2164A and 2118 Dynamic RAMs.

Figure 5. 2164A Memory Array PC Board Layout