# 262144×9 BIT DYNAMIC RANDOM ACCESS MEMORY MODULE

MB85240-10 MB85240-12

> December 1987 Edition 1.0

#### 262,144 x 9 BIT CMOS STATIC COLUMN RANDOM ACCESS MEMORY

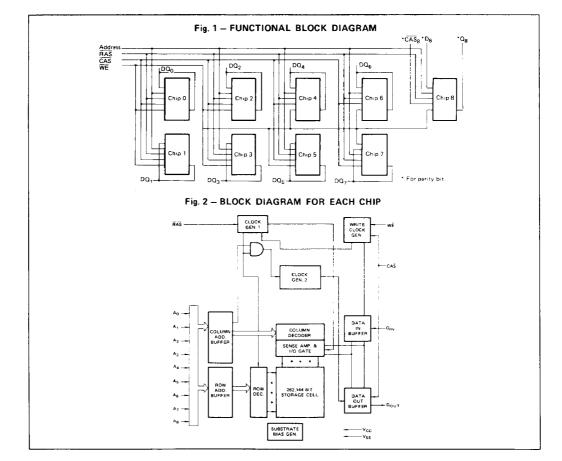

This Fujitsu MB85240 is a fully decoded, 262,144 words x 9 bits CMOS static column random access memory composed of nine 256k SCRAM chips (MB81C258x9). This module is designed for high speed, high performance applications such as main frame memory, buffer memory, and video memory, and for applications to battery backed-up systems where very low power dissipation and compact layout is required. The electrical characteristics of the MB85240 are quite same as the original MB81C258; each timing requirements are noncritical, and power supply tolerance is very wide. All inputs and outputs are TTL compatible.

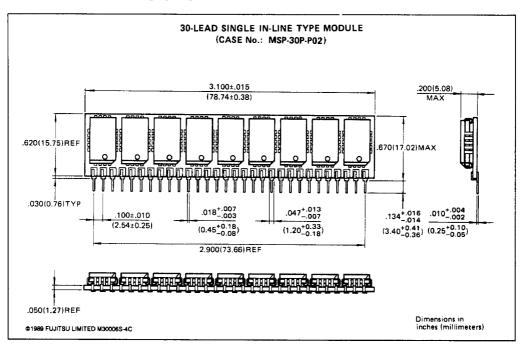

- 262,144 x 9 SCRAM MODULE, 30-pin SIP and socket type

- Row Access Time (t<sub>RAC</sub>)

100 ns max. (MB85240-10)

120 ns max. (MB85240-12)

- Random Cycle Time (t<sub>BC</sub>)

- 200 ns min. (MB85240-10)

- 230 ns min. (MB85240-12)

- Address Access Time (t<sub>AA</sub>)

- 45 ns max. (MB85240-10)

- 55 ns max. (MB85240-12)

- Static Mode Cycle Time (t<sub>SC</sub>)

50 ns min. (MB85240-10)

60 ns min. (MB85240-12)

- Low Power Dissipation

- 2970 mW max. (MB85240-10)

2475 mW max. (MB85240-12)

99 mW max, standby with TTL level input 15 mW max, standby with CMOS level input

- +5V supply, ±10% tolerance

- 32ms/256 refresh cycles capability

- RAS-only, CAS-before-RAS and Hidden refresh capability

#### ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                          | Symbol                             | Value        | Unit |

|-------------------------------------------------|------------------------------------|--------------|------|

| Voltage on any pin relative to V <sub>SS</sub>  | V <sub>IN</sub> , V <sub>OUT</sub> | -1.0 to +7.0 | V    |

| Voltage on $V_{CC}$ supply relative to $V_{SS}$ | Vcc                                | -1.0 to +7.0 | V    |

| Storage temperature                             | T <sub>STG</sub>                   | -55 to 125   | °c   |

| Power dissipation                               | PD                                 | 9.0          | w    |

| Short circuit output current                    | -                                  | 50           | mA   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### CAPACITANCE (TA = 25°C, f = 1MHz)

| Parameter                                           | Symbol           | Тур | Max | Unit |

|-----------------------------------------------------|------------------|-----|-----|------|

| Input Capacitance, A <sub>0</sub> to A <sub>8</sub> | CINI             |     | 80  | pF   |

| Input Capacitance, RAS                              | C <sub>IN2</sub> |     | 88  | pF   |

| Input Capacitance, CAS                              | CIN3             |     | 70  | pF   |

| Input Capacitance, WE                               | C <sub>IN4</sub> |     | 49  | pF   |

| Input Capacitance, CAS <sub>8</sub>                 | C <sub>IN5</sub> |     | 11  | pF   |

| Input Capacitance, D <sub>8</sub>                   | C <sub>IN6</sub> |     | 7   | pF   |

| I/O Capacitance, DQ <sub>0</sub> to DQ <sub>7</sub> | C <sub>D</sub> Q |     | 15  | pF   |

| Output Capacitance, Q <sub>8</sub>                  | C <sub>O</sub>   |     | 11  | pF   |

#### RECOMMENDED OPERATING CONDITIONS (Referenced to VSS)

| Parameter          | Symbol | Min  | Тур | Max | Unit | Operating<br>Temperature |

|--------------------|--------|------|-----|-----|------|--------------------------|

| Supply Voltage     | Vcc    | 4.5  | 5.0 | 5.5 | V    |                          |

|                    | Vss    | 0    | 0   | О   | V    |                          |

| Input High Voltage | VIH    | 2.4  | _   | 6.5 | V    | 0°C to +70°C             |

| Input Low Voltage  | VIL    | -1.0 | _   | 0.8 | V    |                          |

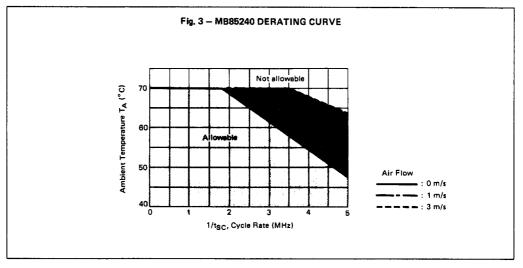

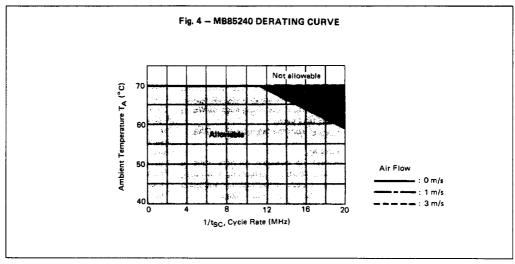

Note \*: Ambient temperature is dependent on cycle time and cooling conditions. See the derating curve Fig. 3 for normal cycle, and Fig. 4 for static mode cycle.

# DC CHARACTERISTICS (Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                              |                                    | Symbol           | Min | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----|-----|------|

| OPERATING/REFRESH CURRENT* Average Power Supply Current                                                                | MB85240-10                         |                  |     | 540 | 1    |

| (RAS, CAS cycling; t <sub>RC</sub> = min)                                                                              | MB85240-12                         | I <sub>cc1</sub> | }   | 450 | m A  |

| STANDBY CURRENT<br>Standby Power Supply Current                                                                        | TTL Level                          |                  |     | 18  |      |

| (RAS, CAS = V <sub>IH</sub> )                                                                                          | CMOS Level                         | CC2              |     | 2.7 | mA   |

| STATIC MODE OPERATING CURRENT* Average Power Supply Current                                                            | MB85240-10                         |                  |     | 360 |      |

| (RAS = CAS = V <sub>IL</sub> , WE or Address = cycling;<br>t <sub>SC</sub> = min)                                      | MB85240-12                         | ссз              |     | 315 | mA   |

| CAS-BEFORE-RAS REFRESH CURRENT* Average Power Supply Current                                                           | MB85240-10                         | 1 <sub>CC4</sub> |     | 495 | mA   |

| (RAS cycling, CAS-before-RAS refresh;<br>t <sub>RC</sub> = min)                                                        | MB85240-12                         | 1004             |     | 405 | "'A  |

| INPUT LEAKAGE CURRENT, ALL INPUTS (V <sub>IN</sub> = 0V to 5.5V, V <sub>CC</sub> = 5V, V <sub>SS</sub> = 0V, all other | INPUT LEAKAGE CURRENT, ALL INPUTS  |                  |     | 10  |      |

| test = 0V)                                                                                                             | test = 0V)                         |                  | -30 | 30  | μΑ   |

| OUTPUT LEAKAGE CURRENT<br>Each output is high impedance<br>(Data is disable, V <sub>OUT</sub> = 0V to 5.5V)            | I <sub>O(L)</sub>                  | -10              | 10  | μΑ  |      |

| OUTPUT LEVELS Output High Voltage (I <sub>OH</sub> = -5 mA) Output Low Voltage (I <sub>OL</sub> = 4.2 mA)              | V <sub>OH</sub><br>V <sub>OL</sub> | 2.4              | 0.4 | v   |      |

Note 1): I<sub>CC</sub> is dependent on the output loading and cycle time. Output pins are open.

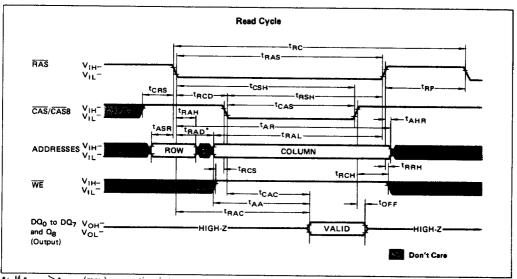

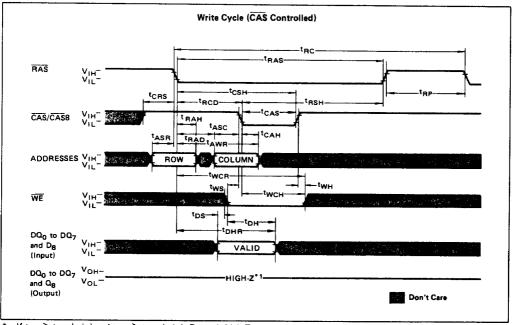

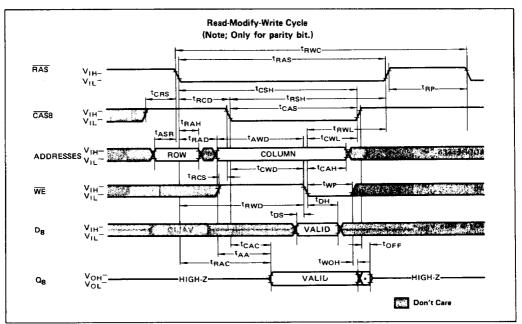

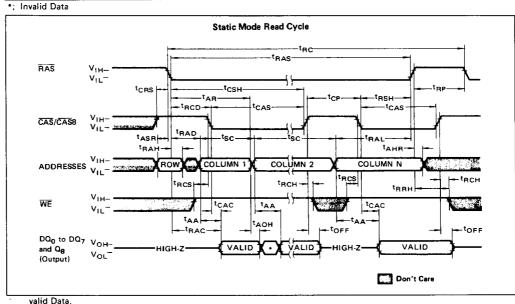

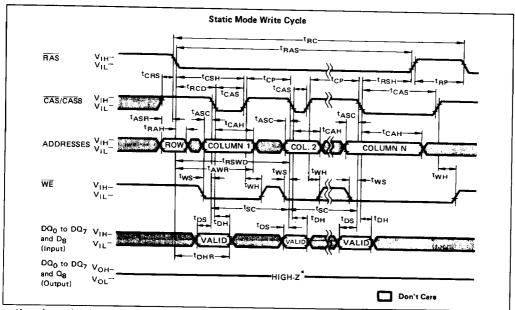

AC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.) Note 1, 2

| Parameter NOTE                                 | Symbol            | MB85240-10 |        | MB85240-12 |        | l    |

|------------------------------------------------|-------------------|------------|--------|------------|--------|------|

| Parameter NOTE                                 | Symbol            | Min        | Max    | Min        | Max    | Unit |

| Time between Refresh                           | t <sub>REF</sub>  | _          | 32     | _          | 32     | ms   |

| Random Read/Write Cycle Time                   | t <sub>RC</sub>   | 200        | _      | 230        | _      | ns   |

| Read-Modify-Write Cycle Time 15                | t <sub>RWC</sub>  | 245        | _      | 285        | _      | ns   |

| Access Time from RAS 3 5                       | t <sub>RAC</sub>  | -          | 100    | _          | 120    | ns   |

| Access Time from CAS                           | t <sub>CAC</sub>  | _          | 25     | _          | 30     | пѕ   |

| Output Buffer Turn Off Delay Time              | t <sub>OFF</sub>  | 0          | 25     | 0          | 25     | ns   |

| Transition Time                                | tγ                | 3          | 50     | 3          | 50     | ns   |

| Column Address Access Time 4 5                 | t <sub>AA</sub>   | _          | 45     | -          | 55     | ns   |

| Output Hold Time from Column Address<br>Change | t <sub>AOH</sub>  | 5          | _      | 5          | _      | ns   |

| Access Time from WE Precharge                  | twpA              | -          | 25     | _          | 30     | ns   |

| Access Time Relative to Last Write 6 15        | tALW              | _          | 90     | _          | 110    | ns   |

| Write latched Output Hold Time                 | t <sub>wo</sub> H | 0          | _      | 0          | _      | ns   |

| RAS Precharge Time                             | t <sub>RP</sub>   | 90         | _      | 100        | _      | ns   |

| RAS Pulse Width                                | t <sub>RAS</sub>  | 65         | 100000 | 75         | 100000 | ns   |

| RAS Hold Time                                  | t <sub>RSH</sub>  | 25         | -      | 30         | _      | ns   |

| CAS Pulse Width (Read)                         | tcas              | 25         | 100000 | 30         | 100000 | ns   |

| CAS Pulse Width (Write)                        | t <sub>CAS</sub>  | 15         | 100000 | 20         | 100000 | ns   |

| CAS Hold Time (Read)                           | t <sub>CSH</sub>  | 100        | -      | 120        | _      | ns   |

| CAS Hold Time (Write)                          | t <sub>CSH</sub>  | 80         | _      | 95         | _      | ns   |

| RAS to CAS Delay Time                          | t <sub>RCD</sub>  | 25         | 75     | 25         | 90     | ns   |

| CAS to RAS Set Up Time                         | t <sub>CRS</sub>  | 20         | _      | 25         | -      | ns   |

| Row Address Set Up Time                        | t <sub>ASR</sub>  | 0          | _      | 0          | _      | ns   |

| Row Address Hold Time                          | t <sub>RAH</sub>  | 15         | -      | 15         | _      | ns   |

| Column Address Set Up Time 7                   | t <sub>ASC</sub>  | 0          | _      | 0          | _      | ns   |

| Column Address Hold Time 7                     | t <sub>CAH</sub>  | 20         | _      | 25         | _      | ns   |

| RAS to Column Address Delay Time 8 9           | t <sub>RAD</sub>  | 20         | 55     | 20         | 65     | ns   |

| Column Address Hold Time Reference to RAS      | t <sub>AR</sub>   | 100        | _      | 120        | -      | ns   |

| Write Address Hold Time Referenced to RAS      | tawr              | 80         | _      | 90         |        | ns   |

# AC CHARACTERISTICS (Cont'd) (Recommended operating conditions unless otherwise noted.) Note 1, 2

| Parameter NOTE                                                       | Sumbol            | MB85240-10<br>Symbol |     | MB85240-12 |     | T    |

|----------------------------------------------------------------------|-------------------|----------------------|-----|------------|-----|------|

| Talanteter Rose                                                      | Symbol            | Min                  | Max | Min        | Max | Unit |

| Read Address to RAS Lead Time                                        | tHAL              | 45                   | _   | 55         | _   | ns   |

| Column Address Hold Time Referenced to RAS Rising Time               | t <sub>AHR</sub>  | 15                   | _   | 15         | _   | ns   |

| Last Write to Column Address Delay Time                              | t <sub>LWAD</sub> | 25                   | 45  | 30         | 55  | ns   |

| Column Address Hold Time Referenced to Last Write                    | t <sub>AHLW</sub> | 90                   | -   | 110        | -   | ns   |

| Read Command Set Up Time Referenced to CAS                           | t <sub>RCS</sub>  | 0                    | -   | 0          | -   | ns   |

| Read Command Hold Time Referenced to RAS                             | t <sub>BBH</sub>  | 10                   | _   | 10         | _   | ns   |

| Read Command Hold Time Referenced to CAS                             | t <sub>RCH</sub>  | 0                    | -   | 0          | _   | ns   |

| WE Pulse Width                                                       | t <sub>WP</sub>   | 15                   | _   | 20         | _   | ns   |

| WE Inactive Time                                                     | t <sub>WI</sub>   | 15                   | _   | 20         | _   | ns   |

| Write Command Hold Time                                              | twch              | 15                   | _   | 20         | _   | ns   |

| Write Command to RAS Lead Time 15                                    | t <sub>RWL</sub>  | 25                   | _   | 30         | _   | ns   |

| Write Command to CAS Lead Time 15                                    | tcwL              | 25                   | _   | 30         | _   | ns   |

| RAS to WE Delay Time 14 15                                           | t <sub>RWD</sub>  | 100                  | _   | 120        | _   | ns   |

| CAS to WE Delay Time                                                 | tcwp              | 25                   |     | 30         | _   | ns   |

| Column Address to WE Delay Time 15                                   | t <sub>AWD</sub>  | 45                   | -   | 55         | _   | ns   |

| RAS to Second Write Delay Time                                       | trswo             | 105                  | _   | 125        | _   | ns   |

| Write Command Hold Time Referenced to RAS                            | twcn              | 80                   | _   | 95         | -   | ns   |

| Write Set Up Time for Output Disable                                 | t <sub>WS</sub>   | 0                    |     | 0          | _   | ns   |

| Write Hold Time for Output Disable 14                                | ŧwн               | 0                    |     | 0          | _   | ns   |

| D <sub>IN</sub> Set Up Time                                          | t <sub>DS</sub>   | 0                    | -   | 0          | _   | ns   |

| D <sub>IN</sub> Hold Time                                            | t <sub>DH</sub>   | 20                   | _   | 25         | _   | ns   |

| D <sub>IN</sub> Hold Time Reference to RAS                           | t <sub>DHR</sub>  | 80                   | _   | 90         | _   | ns   |

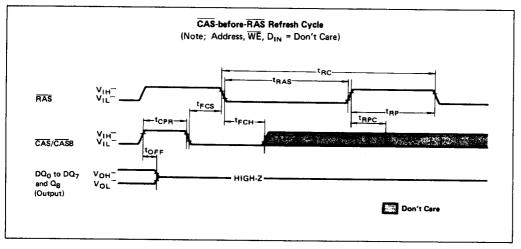

| Refresh Set Up Time for CAS Referenced to RAS (CAS-before-RAS cycle) | t <sub>FC</sub> s | 20                   | _   | 25         | _   | ns   |

### **AC CHARACTERISTICS (Cont'd)**

(Recommended operating conditions unless otherwise noted.) Note 1, 2

|                                                                                          |                   | MB85240-10 |     | MB85240-12 |     | .,   |

|------------------------------------------------------------------------------------------|-------------------|------------|-----|------------|-----|------|

| Parameter NOTES                                                                          | Symbol            | Min        | Max | Min        | Max | Unit |

| Refresh Hold T <u>ime</u> for <u>CAS</u> Referenced to <u>RAS</u> (CAS-before-RAS cycle) | t <sub>FCH</sub>  | 20         | -   | 25         | _   | ns   |

| CAS Precharge Time<br>(CAS-before-RAS cycle)                                             | t <sub>CP</sub> A | 20         | _   | 25         | _   | ns   |

| RAS Precharge Time to CAS<br>Active Time (Refresh cycles)                                | t <sub>RPC</sub>  | 20         | _   | 20         | _   | ns   |

| Static Mode Read/Write Cycle Time                                                        | t <sub>sc</sub>   | 50         | _   | 60         | _   | ns   |

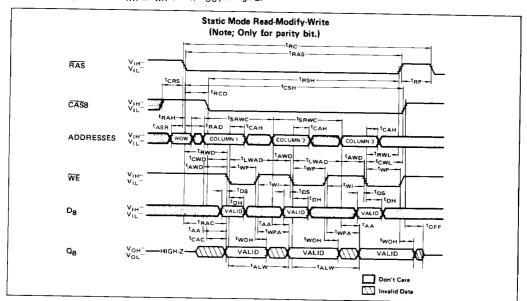

| Static Mode Read-Modify-Write Cycle Time                                                 | tsawc             | 95         | -   | 115        | _   | ns   |

| Static Mode CAS Precharge Time                                                           | t <sub>CP</sub>   | 15         | _   | 20         |     | ns   |

#### NOTES:

- An Initial pause (RAS = CAS = V<sub>IH</sub>) of 200 µs is required after power-up followed by any 8 RAS-only cycles before proper device operation is achieved. In case of using internal refresh counter, a minimum of 8 CAS-before-RAS initialization cycles instead of 8 RAS cycles are required.

- $\blacksquare$  AC characteristics assume  $t_T$  = 5ns,  $V_{IN}$  = 0V to 3V,  $V_{IH}$  = 2.4V,  $V_{IL}$  = 0.8V,  $V_{OH}$  = 2.4V, and  $V_{OL}$  = 0.4V.

- Assumes that  $t_{RAD} \le t_{RAD}$  (max). If  $t_{RAD}$  is greater than the maximum recommended value shown in this table,  $t_{RAC}$  will be increased by the amount that  $t_{RAD}$  exceeds the value shown.

- Assumes that  $t_{RAD} \ge t_{RAD}$  (max).

- Measured with a load equivalent to 2 TTL loads and 100pF.

- Assumes that  $t_{LWAD} \le t_{LWAD}$  (max). If  $t_{LWAD}$  is greater than the maximum recommended value shown in this table,  $t_{ALW}$  will be increased by the amount that  $t_{LWAD}$  exceeds the value shown.

- Write Cycle Only.

- Operation within the t<sub>RAD</sub> (max) limit insures that t<sub>RAC</sub> (max) can be met. t<sub>RAD</sub> (max) is specified as a reference point only; if t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub> (max) limit, then access time is controlled by

- $\mathbf{9} t_{\mathsf{RAS}} (\mathsf{min}) = t_{\mathsf{RAH}} (\mathsf{min}) + t_{\mathsf{T}} (t_{\mathsf{T}} = \mathsf{5ns})$

- 10 t<sub>AHR</sub> is specified to latch column address by the rising edge of RAS.

- Operation within the t<sub>LWAD</sub> (max) limit insures that t<sub>ALW</sub> (max) can be met. t<sub>LWAD</sub> (max) is specified as a reference point only; if t<sub>LWAD</sub> is greater than the specified t<sub>LWAD</sub> (max) limit, then access time is controlled by t<sub>AA</sub>.

- $\mathbf{12} t_{LWAD} (min) = t_{AHW} (min) + t_T (t_T = 5ns)$

- Either tarm or tach must be satisfied for a read cycle.

- In tws,  $t_{WH}$ , and  $t_{RWD}$  are specified as a reference point only. If  $t_{WS} \geq t_{WS}$  (min) and  $t_{WH} \geq t_{WH}$  (min), the data output pin will remain High-Z state throughout entire cycle. It  $t_{RWD} \geq t_{RWD}$  (min). The data output will contain data read from the selected cell.

- 15 Parity bit only.

\*; If  $t_{RAD} \ge t_{RAD}$  (max), access time is  $t_{AA}$

\*; If  $t_{WS} \ge t_{WS}$  (min) and  $t_{WH} \ge t_{WH}$  (min),  $D_{OUT}$  is high-Z.

\*; If  $t_{WS} \ge t_{WS}$  (min) and  $t_{WH} \ge t_{WH}$  (min),  $D_{OUT}$  is high-Z.

\*; Only for parity bit.

#### **FUNCTIONAL TRUTH TABLE**

| RAS | CAS and<br>CAS <sub>8</sub>                               | WE                  | $DQ_0$ to $DQ_7$ , $D_8$ and $Q_8$                                                                                  | Function                                                                                 |

|-----|-----------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| H   | Н                                                         | Don't Care          | High-Z                                                                                                              | Standby                                                                                  |

| L   | L                                                         | Н                   | Valid Data Out <sup>1⟩</sup>                                                                                        | Ready cycle                                                                              |

| L   | L                                                         | L                   | Valid Data In <sup>2)</sup>                                                                                         | Write cycle                                                                              |

| L   | L <sub>3)</sub>                                           | Don't Care          | High-Z                                                                                                              | CAS-before RAS Refresh cycle                                                             |

| L   | Н                                                         | Don't Care          | High-Z                                                                                                              | RAS-only Refresh cycle                                                                   |

| L   | H ( <del>CAS</del> )<br>L ( <del>CAS</del> <sub>B</sub> ) | H → L <sup>4)</sup> | High-Z (DQ <sub>0</sub> to DQ <sub>7</sub> )<br>Valid Data In (D <sub>8</sub> )<br>Valid Data Out (Q <sub>8</sub> ) | RAS-only Refresh cycle (Except for Pairyt bit) Read-Write/Read-Modify-Write (Parity bit) |

Notes: 1): DQ Pins are output mode.

2): DQ pins are input mode.

3):  $t_{FCS} \ge t_{FCS}$  (min) 4):  $t_{CWD} \ge t_{CWD}$  (min)

### 5

#### DESCRIPTION

#### Address Inputs:

A total of eighteen binary input address bits are required to decode any one of the 262,144 storage cells within each MB81C258. Nine row address bits are established on the address input pins (Ao to As) and latched with the Row Address Strobe (RAS). The nine column address bits are established on the address input pins (Ao to Aa) after the Row Address Hold Time (t<sub>RAH</sub>) has been satisfied. In read cycle, the column address are not latched by the Column Address Strobe (CAS), so the column address must be stable until the output becomes valid. In write cycle, the column address are latched by the later falling edge of CAS or WE.

#### Write Enable:

Read or Write cycle is selected with the  $\overline{WE}$  inputs. A high on  $\overline{WE}$  selects read cycle and low selects write cycle. The write operation is asserted on the later falling edge of  $\overline{CAS}$  or  $\overline{WE}$  (Both  $\overline{CAS}$  and  $\overline{WE}$  are low). The time period of the write operation is determined by internal circuit, thus next write operation will be inhibited during the write operation.

#### Data Input:

Data is written into the MB85240 during write or read-modify-write cycle. The input data is strobed and latched by the later falling edge of CAS or WE.

#### **Data Output:**

Each output buffer is three state TTL compatible with a fan out of two standard TTL loads. Data out has the same porality as data in. Each output is in high impedance state until CAS is brought low. In a read cycle, the access time is determined by the following conditions:

- t<sub>RAC</sub> from the falling edge of RAS.

t<sub>AA</sub> from the column address inputs.

- 3.  $t_{CAC}$  from the falling edge of  $\overline{CAS}$ . When both  $t_{RCD}$  and  $t_{RAD}$  satisfy their maximum limits,  $t_{RAC} = t_{RCD} + t_{CAC}$  or  $t_{RAC} = t_{RAD} + t_{AA}$ .

Data outputs remain valid while the column address inputs are kept constant. However, when  $\overline{CAS}$  goes high, the output returns to high impedance state.

#### Static Mode:

The static mode operation allows continuous read, write, or read-modify-write cycle within a row by applying new column address. In the static mode,  $\overline{CAS}$  can be kept low throughout static mode operation. The following four cycles are allowed in the static mode.

- 1. Static mode read cycle:

- In a static mode read cycle, the access time is t<sub>RAC</sub> from the falling edge of RAS or t<sub>AA</sub> from the column address input. The data remains valid for a time t<sub>AOH</sub> after the column address is changed.

- 2. Static mode write cycle:

- In a static mode write cycle, the data is written into the cell triggered by the later falling edge of CAS or WE. If both t<sub>WS</sub> and t<sub>WH</sub> are greater than their minimum limits, the data output pin is kept high impedance state through the static mode write cycle.

- Static mode read-modify-write cycle; In the static mode read-modify-write cycle, WE goes low after t<sub>AWD</sub> from the column address inputs and t<sub>CWD</sub> from the falling edge of CAS. The data and column address inputs are strobed and latched by the falling edge a of WE.

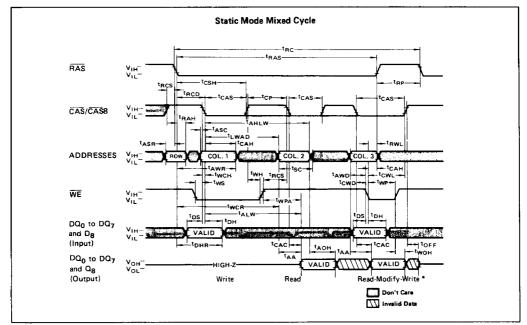

- 4. Static mode mixed cycle;

- In the static mode, read, write, and read-modify-write cycles can be mixed in any order.

In the next read cycle of static mode write cycle or read-modify-write cycle, the access time is determined by the following conditions.

- t<sub>ALW</sub> from the later falling edge of CAS or WE at previous write cycle.

- 2. tAA from the column address inputs.

- t<sub>WPA</sub> from the rising edge of WE at the read cycle.

- 4. t<sub>CAC</sub> from the falling edge of CAS.

#### Refresh

Refresh of dynamic memory cells is accomplished by performing a memory cycle at each of the 256 row addresses (A<sub>0</sub> to A<sub>7</sub>) at least every 32ms.

The MB85240 offers the following three types of refresh.

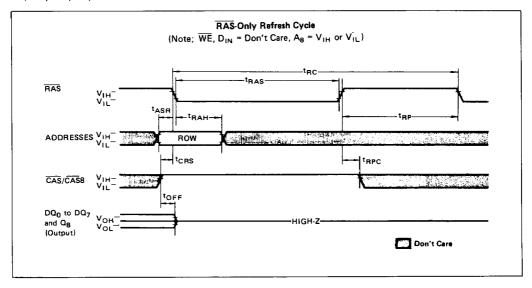

- RAS-only refresh;

- The RAS-only refresh avoids any output during refresh because each output buffer is high impedance state

due to  $\overline{CAS}$  high. Strobing of each  $\frac{256}{RAS}$  row address (A<sub>0</sub> to A<sub>7</sub>) with  $\overline{RAS}$  will cause all bits in each row to be refreshed. During  $\overline{RAS}$ -only refresh cycle, either V<sub>IH</sub> or V<sub>IL</sub> is permitted to A<sub>B</sub>.

- 2. CAS-before-RAS refresh;

- CAS-before-RAS refreshing available on the MB85240 offers an alternate refresh method. If CAS is held low for the specified period (t<sub>FCS</sub>) before RAS goes low, on chip refresh control clock generator and the internal refresh address counter are enabled, and an internal refresh operation, the refresh address counter is automatically incremented in preparation for the next CAS-before-RAS refresh.

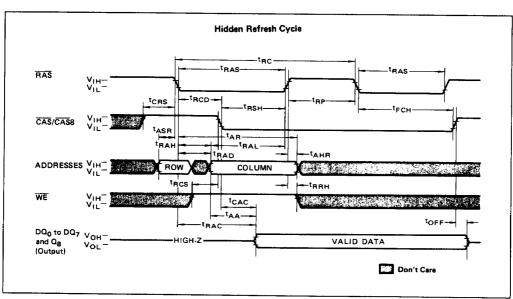

- 3. Hidden refresh:

A hidden refresh cycle will be executed while maintaining latest valid output datas at the DQ pins by extending the CAS low time. For the MBB5240, a hidden refresh cycle is CAS-before-RAS refresh. The internal refresh address counter provides the refresh address, as in a normal CAS-before-RAS refresh cycle.

#### Notice for using MB8520

The MB85240 is a SIP (Single-In-Line-Package) module which is composed of nine MB81C258 DRAMs housed in plastic LCC, and assembled on the epoxy printed circuit board. Generally the multilayer PCB board has large wiring capacitance. This disadvantage causes relatively noise induction between signal lines and power supply lines ( $V_{SS}$  or  $V_{CC}$ ).

Furthermore, as the MB85240 is a very high-speed memory, the timing windows to strobe address  $\overline{WE}$  and  $D_{IN}$  signals are very short (Approx. 10ns). Therefore, it is very sensitive even to very sharp noise.

From the above reasons, special care should be taken for use the MB85240. The following notices are recommended;

#### **DESCRIPTION**

- 1. Provide a externally capacitor of approx. a few  $\mu F$  each module, the MB85240 has the nine decoupling capacitors (0.22 µF on each SCRAM  $0.22 \, \mu F \times 9$ ).

- 2. Remove noise, riging, overshoot and undershoot from the address, clocks

- and DQ lines, so that the MB85240 won't latch wrong signals due to the noise induction between signal lines 4. Provide an appropriate dumping if and between signal and power supply

- 3. Keep enough timing margin and remove critical timing in the board

- design, to avoid the problem mentioned in the above item 2.

- necessary, to avoid excessive overshoot or undershoot on the TTL input waveforms.

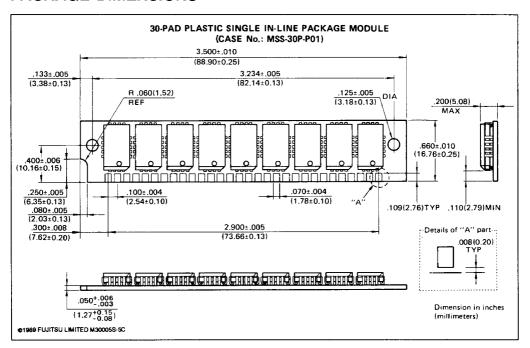

### PACKAGE DIMENSIONS

#### PACKAGE DIMENSIONS