# TMC3211

# Integer Divider 32-Bit. 20 MOPS

#### **Features**

- 32-bit by 16-bit fixed-point integer division with 32-bit quotient

- 20 MHz clock rate and pipelined throughput rate

- Three-bus I/O architecture allows unrestricted throughput

- · Easy system interfacing

- · Status flags for divide-by-zero and inexact result

- · All inputs and outputs TTL compatible

## **Applications**

- · Graphics and image processors

- Matrix operations and geometric transforms

- · Perspective extraction

- · Radar signal processing

- Range scaling

## **Description**

The TMC3211 is a fast monolithic two's complement integer divider which can divide a 32-bit dividend by a 16-bit divisor to produce a 32-bit quotient, with a maximum pipelined throughput of 20 MOPS (Million Operations Per Second).

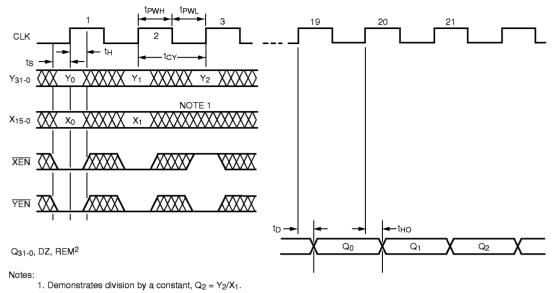

Data is input on separate busses, and quotients are available on a 32-bit output bus with synchronous three-state enable. All data inputs and outputs are registered and TTL compatible. All input and output signal timing is referenced to the rising edge of Clock.

The TMC3211 has a single system clock and separate load enable controls for the dividend and divisor registers. This allows the device to be used in applications requiring division by a constant. Underflow automatically produces the expected zero quotient, and dividing by zero sets a divide-by-zero output flag.

The internal architecture of the TMC3211 allows all 32-bit two's complement integer dividends and nonzero 16-bit two's complement integer divisors, without prenormalization. The output quotient format is 32-bit integer.

The TMC3211 makes a full-precision, full-speed divide function available to designers of workstations, image processors, and radar systems who need to perform perspective extractions, matrix operations, range scaling, and other complex functions.

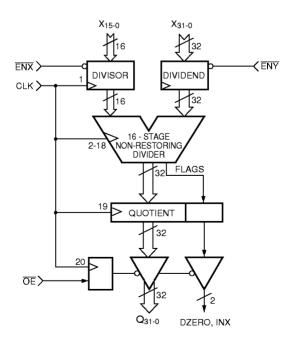

# **Block Diagram**

# **Functional Description**

#### **General Information**

The TMC3211 consists of input registers, a pipelined array divider, and output (quotient) registers. The 16-bit divisor and 32-bit dividend input registers can each be loaded independently using the two synchronous load enable controls. The divider is a 16-stage pipelined non-restoring array which produces a 32-bit quotient and condition flags which indicate an attempted division by zero, or operations which yield a non-zero remainder or inexact result.

The 32-bit parallel quotient output register includes three-state output drivers with synchronous enable control, which permits multiple TMC3211s to be operated in parallel or connected directly to a system bus.

The TMC3211 requires a total of 19 clock cycles to generate a full 32-bit quotient result. Once the internal pipeline is full, a new quotient is available at the output every clock cycle.

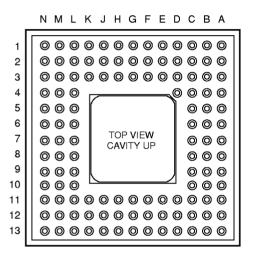

### **Pin Assignments**

| Pin        | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|------------|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| A1         | GND             | C5  | Y <sub>11</sub> | G11 | Q <sub>17</sub> | L10 | Q <sub>27</sub> |

| A2         | Y <sub>14</sub> | C6  | Y <sub>8</sub>  | G12 | $V_{DD}$        | L11 | $V_{DD}$        |

| А3         | Y <sub>13</sub> | C7  | Y <sub>4</sub>  | G13 | Q <sub>16</sub> | L12 | GND             |

| <b>A</b> 4 | $V_{DD}$        | C8  | Y <sub>0</sub>  | H1  | Y <sub>24</sub> | L13 | Q <sub>24</sub> |

| A5         | Y <sub>9</sub>  | C9  | Q <sub>1</sub>  | H2  | Y <sub>25</sub> | M1  | Y <sub>31</sub> |

| A6         | Y <sub>6</sub>  | C10 | $Q_5$           | НЗ  | GND             | M2  | X <sub>0</sub>  |

| <b>A</b> 7 | Y <sub>5</sub>  | C11 | GND             | H11 | GND             | М3  | X <sub>2</sub>  |

| A8         | Y <sub>2</sub>  | C12 | GND             | H12 | Q <sub>19</sub> | M4  | X <sub>4</sub>  |

| A9         | REM             | C13 | $Q_9$           | H13 | Q <sub>18</sub> | M5  | X <sub>6</sub>  |

| A10        | Q               | D1  | Y <sub>18</sub> | J1  | Y <sub>26</sub> | M6  | X <sub>9</sub>  |

| A11        | Q <sub>3</sub>  | D2  | Y <sub>17</sub> | J2  | Y <sub>27</sub> | M7  | X <sub>11</sub> |

| A12        | Q <sub>6</sub>  | D3  | GND             | J3  | $V_{DD}$        | M8  | X <sub>14</sub> |

| A13        | $V_{DD}$        | D11 | $V_{DD}$        | J11 | V <sub>DD</sub> | М9  | CLK             |

| B1         | YEN             | D12 | Q <sub>10</sub> | J12 | Q <sub>21</sub> | M10 | Q <sub>30</sub> |

| B2         | Y <sub>15</sub> | D13 | Q <sub>11</sub> | J13 | Q <sub>20</sub> | M11 | GND             |

| ВЗ         | $V_{DD}$        | E1  | Y <sub>20</sub> | H1  | Y <sub>24</sub> | M12 | GND             |

| B4         | Y <sub>12</sub> | E2  | Y <sub>19</sub> | H2  | Y <sub>25</sub> | M13 | Q <sub>25</sub> |

| B5         | Y <sub>10</sub> | E3  | GND             | Н3  | GND             | N1  | GND             |

| B6         | Y <sub>7</sub>  | E11 | GND             | H11 | GND             | N2  | X <sub>21</sub> |

| B7         | Y <sub>3</sub>  | E12 | Q <sub>12</sub> | H12 | Q <sub>19</sub> | N3  | X <sub>3</sub>  |

| B8         | Y <sub>1</sub>  | E13 | Q <sub>13</sub> | H13 | Q <sub>18</sub> | N4  | X <sub>5</sub>  |

| B9         | DZ              | F1  | Y <sub>22</sub> | L1  | Y <sub>30</sub> | N5  | X <sub>7</sub>  |

| B10        | Q <sub>2</sub>  | F2  | Y <sub>21</sub> | L2  | $V_{DD}$        | N6  | X <sub>10</sub> |

| B11        | Q <sub>4</sub>  | F3  | $V_{DD}$        | L3  | GND             | N7  | X <sub>12</sub> |

| B12        | Q <sub>7</sub>  | F11 | $V_{DD}$        | L4  | $V_{DD}$        | N8  | X <sub>13</sub> |

| B13        | Q <sub>8</sub>  | F12 | Q <sub>14</sub> | L5  | GND             | N9  | XEN             |

| C1         | Y <sub>16</sub> | F13 | Q <sub>15</sub> | L6  | X <sub>8</sub>  | N10 | ŌEQ             |

| C2         | $V_{DD}$        | G1  | Y <sub>23</sub> | L7  | $V_{DD}$        | N11 | Q <sub>29</sub> |

| СЗ         | $V_{DD}$        | G2  | GND             | L8  | X <sub>15</sub> | N12 | Q <sub>28</sub> |

| C4         | GND             | G3  | $V_{DD}$        | L9  | Q <sub>31</sub> | N13 | Q <sub>26</sub> |

# **Pin Descriptions**

| Signal<br>Type | Signal<br>Name  | Pin Number                                                                                                                                                                  | Description                                                                                                                                                                                                                      |

|----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power          | V <sub>DD</sub> | B3, A4, A13, D11, F11, G12, J11,<br>K11, L11, L7, L4, L2, J3, G3, F3,<br>C2, C3                                                                                             | <b>Supply Voltage, Ground.</b> The TMC3211 operates on a single +5V supply. All power and ground lines must be connected.                                                                                                        |

|                | GND             | A1, C4, C11, C12, E11, H11, L12,<br>M12, M11, L5, L3, N1, K3, H3,<br>G2, E3, D3                                                                                             |                                                                                                                                                                                                                                  |

| Clock          | CLK             | <b>M</b> 9                                                                                                                                                                  | <b>System Clock.</b> The TMC3211 has a single Clock input. All input and output signal timing is referenced to the rising edge of Clock.                                                                                         |

| Inputs         | Y31-0           | M1, L1, K2, K1, J2, J1, H2, H1, G1, F1, F2, E1, E2, D1, D2, C1, B2, A2, A3, B4, C5, B5, A5, C6, B6, A6, A7, C7, B7, A8, B8, C8                                              | <b>Dividend Data.</b> The 32-bit Dividend is presented through the registered Y input port. Y <sub>31</sub> is the sign bit. The LSB is Y <sub>0</sub> .                                                                         |

|                | X15-0           | U8, M8, N8, N7, M7, N6, M6, L6,<br>NS, MS, N4, M4, N3, M3, N2, M2                                                                                                           | <b>Divisor Data.</b> The 16-bit Divisor is presented through the registered X input port. X <sub>15</sub> is the sign bit. The LSB is X <sub>0</sub> .                                                                           |

| Outputs        | Q31-0           | L9, M10, N11, N12, L10, N13,<br>M13, L13, K12, K13, J12, J13,<br>H12, H13, G11, G13, F13, F12,<br>E13, E12, D13, D12, C13, B13,<br>B12, A12, C10, B11, A11, B10,<br>C9, A10 | <b>Quotient Data.</b> The current Quotient is available on the registered Q output bus. Q <sub>31</sub> is the sign bit. The LSB is Q <sub>0</sub> .                                                                             |

| Controls       | YEN             | B1                                                                                                                                                                          | <b>Dividend Write Enable.</b> Data present at the Dividend input Y <sub>31-0</sub> is latched into the input registers on the rising edge of clock when the enable control YEN is LOW.                                           |

|                | XEN             | N9                                                                                                                                                                          | <b>Divisor Write Enable.</b> Data present at the Divisor input X <sub>15-0</sub> is latched into the input registers on the rising edge of clock when the enable control XEN is LOW.                                             |

|                | ŌĒQ             | N10                                                                                                                                                                         | Quotient Output Enable. The quotient output bus Q <sub>31-0</sub> and flags DZ and REM are in the high-impedance state when the registered Output Enable OEQ is HIGH. When OEQ is LOW, they are enabled on the next clock cycle. |

| Flags          | DZ              | B9                                                                                                                                                                          | <b>Divide-By Zero Flag.</b> When a zero divisor is input, the resulting invalid output quotient will be accompanied by a registered Divide-By-Zero Flag HIGH.                                                                    |

|                | REM             | A9                                                                                                                                                                          | Inexact Remainder Flag. Whenever a division operation leaves a nonzero remainder, the resulting qotient is accompanied by a registered nonzero Remainder Flag HIGH.                                                              |

| No<br>Connect  |                 | D4                                                                                                                                                                          | Index Pin                                                                                                                                                                                                                        |

# **Applications Discussion**

#### **Division Using A Constant**

By utilizing the separate input data register load enable controls, the TMC3211 can perform division by a constant. The data currently held remain in the input registers until updated by the user.

#### **Data Formats**

The TMC3211 supports fixed-point two's complement data formats. By keeping track of the binary points of the input data, the user can then interpret the resulting quotient properly. Two possible binary weightings of the input and output bits are as follows:

| Pin | D31              | D30             | D29             | D28             | D27             | D26             | D25             | D24             | D23             | D22             | D21             | D20             | D19             | D18             | D17             | D16             | D15              | D14             | D13             | D12             | D11 | D10             | D9             | D8             | D7             | D6             | D5             | D4             | D3             | D2             | D1 | D0             |

|-----|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|-----|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----|----------------|

| Y   | -2 <sup>31</sup> | 2 <sup>30</sup> | 2 <sup>29</sup> | 2 <sup>28</sup> | 2 <sup>27</sup> | 2 <sup>26</sup> | 2 <sup>25</sup> | 2 <sup>24</sup> | 2 <sup>23</sup> | 2 <sup>22</sup> | 2 <sup>21</sup> | 2 <sup>20</sup> | 2 <sup>19</sup> | 2 <sup>18</sup> | 2 <sup>17</sup> | 2 <sup>16</sup> | 2 <sup>15</sup>  | 214             | 2 <sup>13</sup> | 2 <sup>12</sup> | 211 | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 2 <sup>0</sup> |

| X   |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 | -2 <sup>15</sup> | 214             | 2 <sup>13</sup> | 212             | 211 | 210             | 2 <sup>9</sup> | 2 <sup>8</sup> | 27             | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 2 <sup>0</sup> |

| Q   | -2 <sup>31</sup> | 2 <sup>30</sup> | 2 <sup>29</sup> | 2 <sup>28</sup> | 2 <sup>27</sup> | 2 <sup>26</sup> | 2 <sup>25</sup> | 2 <sup>24</sup> | 2 <sup>23</sup> | 2 <sup>22</sup> | 2 <sup>21</sup> | 2 <sup>20</sup> | 2 <sup>19</sup> | 2 <sup>18</sup> | 2 <sup>17</sup> | 2 <sup>16</sup> | 2 <sup>15</sup>  | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 211 | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21 | 2 <sup>0</sup> |

Figure 1. Integer Data Format

| Υ | -2 <sup>0</sup>  | .2-1 | 2-2             | 2-3             | 2-4 | 2-5             | 2-6            | 2-7            | 2-8            | 2 <sup>-9</sup> | 2-10           | 2-11           | 2-12           | 2-13           | 2-14 | 2-15           | 2-16            | 2-17             | 2-18 | 2-19 | 2-20            | 2-21            | 2-22 | 2-23 | 2-24            | 2-25 | 2-26 | 2-27 | 2-28 | 2-29 | 2-30 | 2-31             |

|---|------------------|------|-----------------|-----------------|-----|-----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|----------------|------|----------------|-----------------|------------------|------|------|-----------------|-----------------|------|------|-----------------|------|------|------|------|------|------|------------------|

| х |                  |      |                 |                 |     |                 |                |                |                |                 |                |                |                |                |      |                | -2 <sup>0</sup> | .2 <sup>-1</sup> | 2-2  | 2-3  | 2-4             | 2 <sup>-5</sup> | 2-6  | 2-7  | 2-8             | 2-9  | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2 <sup>-15</sup> |

| Q | -2 <sup>15</sup> | .214 | 2 <sup>13</sup> | 2 <sup>12</sup> | 211 | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup>  | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 21   | 2 <sup>0</sup> | 2-1             | 2-2              | 2-3  | 2-4  | 2 <sup>-5</sup> | 2-6             | 2-7  | 2-8  | 2 <sup>-9</sup> | 2-10 | 2-11 | 2-12 | 2-13 | 2-14 | 2-15 | 2-16             |

Figure 2. Fractional Data Format

where a leading minus sign indicates a sign bit.

Care must be taken when adopting fractional data formats. By observing the binary weighting applied to the input data in the dividend and divisor, the binary point of the quotient can then be correctly established. The difference lies only in constant scale factors, which must be considered in order to maintain a data format which is compatible with the bit weighting of the hardware system. The two most common choices are fractional and integer notation. If integer notation is used, the LSBs of the dividend, divisor, and quotient all have the same value. With fractional notation the MSBs are all of equal weight.

#### Divide by Zero

The flag DZ indicates that the divisor input for the current calculation was a zero, independent of the dividend. Dividing by zero is an undefined operation yielding a meaningless quotient. Thus, this flag must be monitored to guard against possible errors.

#### **Inexact Results**

The flag REM is provided to indicate that the current quotient left a nonzero remainder and was truncated toward zero

#### **Negative Full-Scale Overflow**

Due to a finite data word width, a two's complement overflow error occurs under the following unique condition:

Divisor Y=80000000H (- Full-Scale) Dividend X=FFFFH (-1)

Result:

Quotient Q=80000000H (- Full-Scale)

As stated above, this is due to a limitation in the number of bits available to indicate a positive full-scale quotient, and data overflows into the MSB position to indicate an incorrect sign.

2. Assumes  $\overline{OEQ}$  = Low.

Figure 3. Timing Diagram

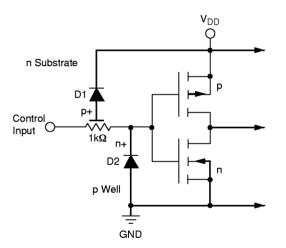

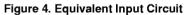

Figure 5. Equivalent Output Circuit

# **Absolute Maximum Ratings**

(beyond which the device may be damaged)<sup>1</sup>

| Parameter      |                                                                | Min  | Max                   | Units |

|----------------|----------------------------------------------------------------|------|-----------------------|-------|

| Supply Voltage |                                                                | -0.5 | +7.0                  | V     |

| Input Voltage  |                                                                | -0.5 | V <sub>DD</sub> + 0.5 | V     |

| Output         | Applied Voltage <sup>2</sup>                                   | -0.5 | V <sub>DD</sub> + 0.5 | V     |

|                | Forced Current <sup>3,4</sup>                                  | -3.0 | 6.0                   | mA    |

|                | Short-circuit duration (single output in HIGH state to ground) |      | 1                     | sec   |

| Temperature    | Operating, case                                                | -60  | +130                  | °C    |

|                | Junction                                                       |      | 175                   | °C    |

|                | Lead, soldering (10 seconds)                                   |      | 300                   | °C    |

|                | Storage                                                        | -65  | +150                  | °C    |

#### Notes:

- 1. Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions. Functional operation under any of these conditions is NOT implied.

- 2. Applied voltage must be current limited to specified range, and measured with respect to GND.

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# **Operating Conditions**

|       |                                |                       | Tem  | perature R | ange |       |

|-------|--------------------------------|-----------------------|------|------------|------|-------|

|       |                                |                       |      | Standard   |      |       |

| Param | eter                           | Test Conditions       | Min. | Nom.       | Max. | Units |

| VDD   | Supply Voltage                 |                       | 4.75 | 5.0        | 5.25 | V     |

| VIL   | Input Voltage, Logic LOW       |                       |      |            | 0.8  | ٧     |

| VIH   | Input Voltage, Logic HIGH      |                       | 2.0  |            |      | V     |

| loL   | Output Current, Logic LOW      |                       |      |            | 4.0  | mA    |

| ЮН    | Output Current, Logic HIGH     |                       |      |            | -2.0 | mA    |

| tcy   | Cycle Time                     | V <sub>DD</sub> = Min |      |            | 50   | ns    |

| tpwL  | Clock Pulse Width, LOW         | V <sub>DD</sub> = Min | 15   |            |      | ns    |

| tPWH  | Clock Pulse Width, HIGH        | V <sub>DD</sub> = Min | 15   |            |      | ns    |

| ts    | Input Setup Time               |                       | 12   |            |      | ns    |

| tH    | Input Hold Time                |                       | 6    |            |      | ns    |

| Тд    | Ambient Temperature, Still Air |                       | 0    |            | 70   | °C    |

6

# DC Characteristics within Specified Operating Conditions<sup>1</sup>

|        |                                             |                                                                                 | Temperat | ure Range |       |

|--------|---------------------------------------------|---------------------------------------------------------------------------------|----------|-----------|-------|

|        |                                             |                                                                                 | Stan     | dard      |       |

| Paramo | eter                                        | Test Conditions                                                                 | Min.     | Max.      | Units |

| IDDQ   | Supply Current, Quiescent                   | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V                                     |          | 5         | mA    |

| IDDU   | Supply Current, Unloaded                    | V <sub>DD</sub> = Max, <del>OEQ</del> = 5V, f = 20MHz                           |          | 150       | mA    |

| IIL    | Input Current, Logic LOW                    | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V                                     |          | -10       | μΑ    |

| IH     | Input Current, Logic HIGH                   | V <sub>DD</sub> = Max, V <sub>IN</sub> = V <sub>DD</sub>                        |          | 10        | μΑ    |

| VoL    | Output Voltage, Logic LOW                   | V <sub>DD</sub> = Min, l <sub>OL</sub> = Max                                    |          | 0.4       | V     |

| Vон    | Output Voltage, Logic HIGH                  | V <sub>DD</sub> = Min, I <sub>OH</sub> = Max                                    | 2.4      |           | V     |

| lozL   | Hi-Z Output Leakage<br>Current, Output LOW  | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V                                     |          | -40       | μА    |

| lozh   | Hi-Z Output Leakage<br>Current, Output HIGH | V <sub>DD</sub> = Max, V <sub>IN</sub> = V <sub>DD</sub>                        |          | 40        | μА    |

| los    | Short-Circuit Output Current                | V <sub>DD</sub> = Max, Output HIGH, one pin to ground, one second duration max. |          | -150      | mA    |

| Cı     | Input Capacitance                           | T <sub>A</sub> = 25°C, f = 1MHz                                                 |          | 10        | pF    |

| Co     | Output Capacitance                          | TA = 25°C, f = 1MHz                                                             |          | 10        | рF    |

#### Note:

# **AC Characteristics within Specified Operating Conditions**

|       |                           |                                                 | Tempe | erature |       |

|-------|---------------------------|-------------------------------------------------|-------|---------|-------|

|       |                           |                                                 | Stan  | dard    |       |

| Param | eter                      | Test Conditions                                 | Min   | Max     | Units |

| tD    | Output Delay <sup>1</sup> | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 25pF |       | 35      | ns    |

| tHO   | Output Hold Time          | V <sub>DD</sub> = Max, C <sub>LOAD</sub> = 25pF | 5     |         | ns    |

#### Note:

<sup>1.</sup> Actual test conditions may vary from those shown, but guarantee operation as specified

<sup>1.</sup> Equivalent to tDIS and tENA of the three-state outputs

# **Notes**

# **Notes**

# **Notes**

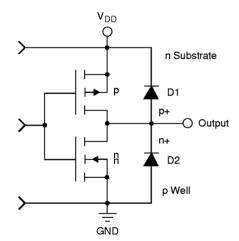

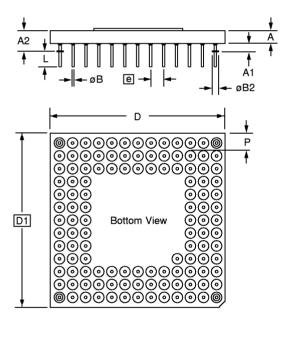

### **Mechanical Dimensions**

### 120-Pin Plastic Pin Grid Array - H5 Package

|        | Inc   | hes   | Millin | neters |       |

|--------|-------|-------|--------|--------|-------|

| Symbol | Min.  | Max.  | Min.   | Max.   | Notes |

| Α      | .080  | .125  | 2.03   | 3.18   |       |

| A1     | .040  | .060  | 1.02   | 1.52   |       |

| A2     | .105  | .180  | 2.67   | 4.57   |       |

| øΒ     | .017  | .020  | 0.43   | 0.51   |       |

| øB2    | .050  | NOM.  | 1.27   | NOM.   |       |

| D      | 1.340 | 1.350 | 34.04  | 35.05  |       |

| D1     | 1.200 | BSC   | 30.48  | BSC    |       |

| е      | .100  | BSC   | 2.54   | BSC    |       |

| L      | .120  | .140  | 3.05   | 3.56   |       |

| М      | 1     | 3     | 1      | 3      | 2     |

| N      | 12    | 21    | 1:     | 3      |       |

| Р      | .003  | _     | .076   | _      |       |

#### Notes:

- 1. Pin #1 identifier shall be within shaded area shown.

- 2. Dimension "M" defines matrix size.

- 3. Dimension "N" defines the maximum possible number of pins.

- 4. Controlling dimension: inch.

11

# **Ordering Information**

| Product<br>Number | Temperature Range    | Screening  | Package                        | Package<br>Marking |

|-------------------|----------------------|------------|--------------------------------|--------------------|

| TMC3211H5C        | STD-TA = 0°C to 70°C | Commercial | 120 Pin Plastic Pin Grid Array | 3211H5C            |

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com