# T8533/T8534 Quad Programmable Codec and Echo Canceller

## Features

- Includes codec, termination impedance, and echo canceller in one device for line card applications

- Programmable µ-law, linear, or A-law PCM input and output (ITU-T G.712 compliant)

- Per-channel programmable gains

- Per-channel programmable internal termination impedance

- Per-channel 64-tap echo canceller (ITU-T G.168 compliant)

- Fully programmable time-slot assignment

- Analog and digital loopback test modes

- Serial microprocessor interface

- Sigma-delta converters with dither to reduce noise

- Five per-channel, bidirectional control pins for SLIC and line card function control (64-pin package)

- Quad design to minimize package count on dense line card applications

- Built-in level correction (transmit equalization) to accommodate current-sensing SLICs

- Single 5 V operation

- Available in 64-pin and 44-pin packages

## **General Description**

The quad programmable codec consists of four independent channels of codec and digital signal processing functions on one chip. In addition to the classic A-to-D and Dto-A conversion, the device includes termination impedance synthesis and a

64-tap echo canceller, functionally, on a per-channel basis. The device is capable of meeting all international standards for terminating impedance and digital encoding format. The processing circuitry for the adjustment of the transmit level (equalization) to accommodate currentsensing SLICs is also included.

The device is controlled by a serial microprocessor interface, and a set of bidirectional I/O pins are provided, on a per-channel basis, so that this control mechanism can be utilized to operate the battery feed device, ringing voltage switches, etc. Common data and clock paths can be shared over any number of devices. All the filter coefficients, signal processing, SLIC, and test features are accessible through this interface. This serial interface can be operated at speeds up to 4.096 Mbits/s.

The PCM bus is also programmable, with any channel capable of being assigned to any time slot. The PCM bus can be operated at speeds up to

16.384 Mbits/s, allowing for a maximum of 256 time slots. Separate transmit and receive interfaces are available for 4-wire bus designs, or they can be strapped together for a 2-wire PCM bus.

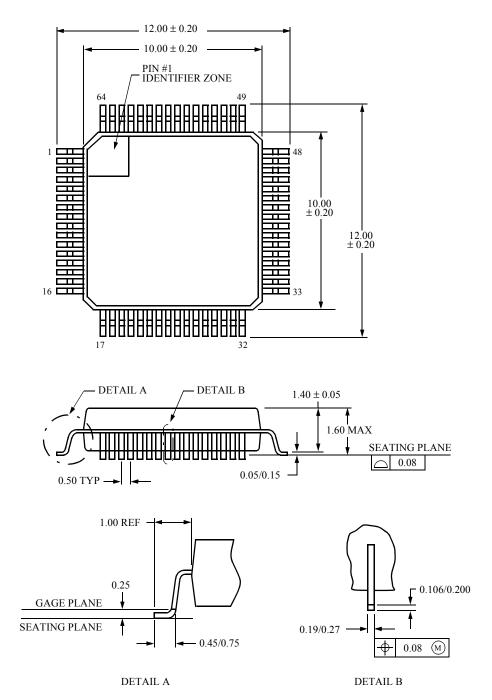

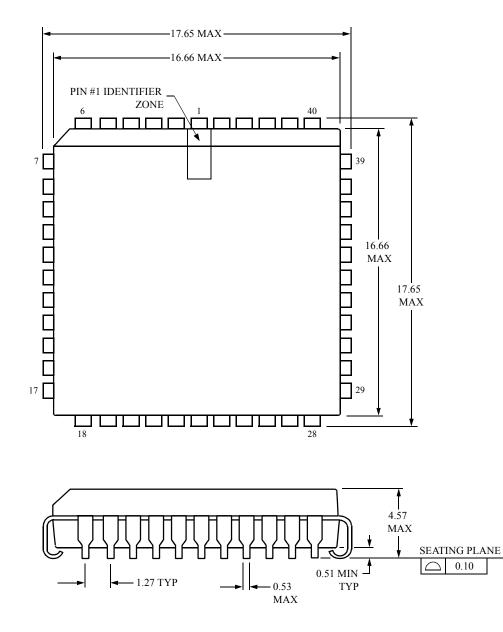

The device is available in 64-pin and 44-pin surfacemount packages for economic use of board space.

| Document ID#          | 081000 | Date:    | Nov 01, 2002 |  |

|-----------------------|--------|----------|--------------|--|

| Rev:                  | Α      | Version: | 1            |  |

| Rev:<br>Distribution: | Public |          |              |  |

Page

## **Table of Contents**

## Section

## Page Figure

| Features                            | 1  |

|-------------------------------------|----|

| General Description                 | 1  |

| Functional Description              | 3  |

| Pin Information                     |    |

| Functional Description              | 9  |

| Clocking Considerations             |    |

| The Control Interface               | 9  |

| Modes                               | 9  |

| Protocol                            | 10 |

| Write Command                       | 12 |

| Read Command                        | 14 |

| Fast Scan Mode                      |    |

| Write All Channels                  | 21 |

| Reset Functionality                 |    |

| Memory Control Mapping              | 22 |

| Standby Mode                        | 22 |

| Test Capabilities                   | 22 |

| Echo Canceller Functionality        |    |

| SLIC Control Capabilities           | 23 |

| Suggested Initialization Procedures |    |

| Signal Processing                   | 24 |

| Absolute Maximum Ratings            | 24 |

| Operating Ranges                    | 25 |

| Handling Precautions                |    |

| Electrical Characteristics          | 25 |

| dc Characteristics                  | 25 |

| Analog Interface                    | 26 |

| Transmission Characteristics        | 27 |

| Noise Characteristics               | 29 |

| Distortion and Group Delay          | 30 |

| Crosstalk                           |    |

| Timing Characteristics              | 32 |

| Bus Timing Diagrams                 |    |

| Normal Mode                         | 34 |

| Byte-by-Byte Mode                   |    |

| PCM Interface                       | 35 |

| Software Interface                  | 36 |

| Applications                        | 42 |

| Outline Diagrams                    |    |

| 64-Pin TQFP                         |    |

| 44-Pin PLCC                         |    |

| Ordering Information                |    |

|                                     |    |

| Functional Block Diagram, Each Section               | 3    |

|------------------------------------------------------|------|

| 44-Pin PLCC Pin Diagram                              | 5    |

| 64-Pin TQFP Pin Diagram                              | 7    |

| Command Frame Format, Master to Slave,               |      |

| Read or Write Commands                               | . 11 |

| Command Frame Format, Slave to Master,               |      |

| Read Commands                                        | . 11 |

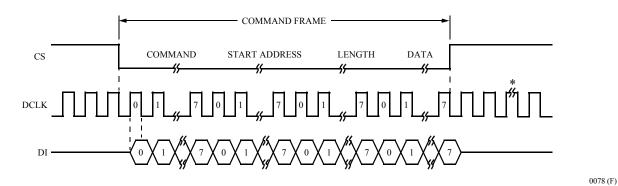

| Write Operation, Normal Mode (Continuous DCLK)       |      |

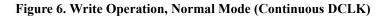

| Write Operation, Normal Mode (Gapped DCLK)           |      |

| Write Operation, Byte-by-Byte Mode                   |      |

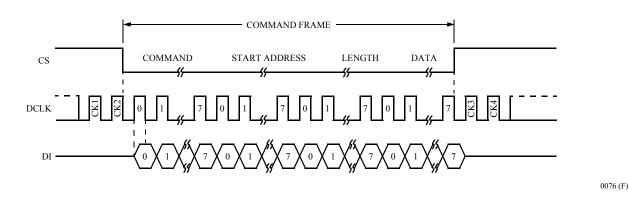

| (Continuous DCLK)                                    | . 13 |

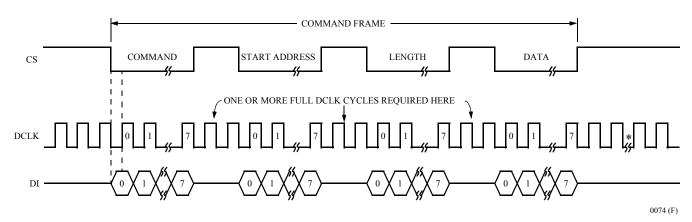

| Write Operation, Byte-by-Byte Mode (Gapped DCLK) .   |      |

| Read Operation, Normal Mode (Continuous DCLK)        |      |

| Read Operation, Normal Mode (Gapped Clock)           |      |

| Read Operation, Byte-by-Byte Mode                    |      |

| (Continuous DCLK)                                    | 16   |

| Read Operation, Byte-by-Byte Mode (Gapped DCLK)      |      |

| Fast Scan, Normal Mode (Continuous DCLK)             |      |

| Fast Scan, Normal Mode (Gapped DCLK)                 |      |

| Fast Scan, Byte-by-Byte Mode (Continuous DCLK)       |      |

| Fast Scan, Byte-by-Byte Mode (Continuous DeDix)      |      |

| Hardware Reset Procedure                             |      |

| Internal Signal Processing                           |      |

| Serial Interface Timing, Normal Mode                 | . 27 |

| (One Byte Transfer Shown)                            | 31   |

| Serial Interface Timing, Byte-by-Byte Mode (One Byte | . 54 |

| Transfer and Gapped DCLK Shown)                      | 3/   |

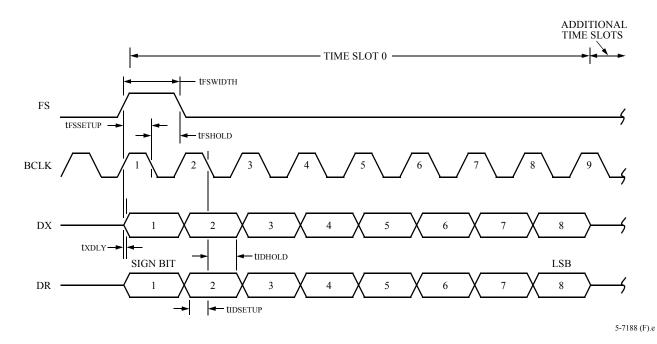

| PCM Bus Timing (Diagram Shown has Bit Offset         | . 54 |

| of Zero and Minimum Width of FS)                     | 25   |

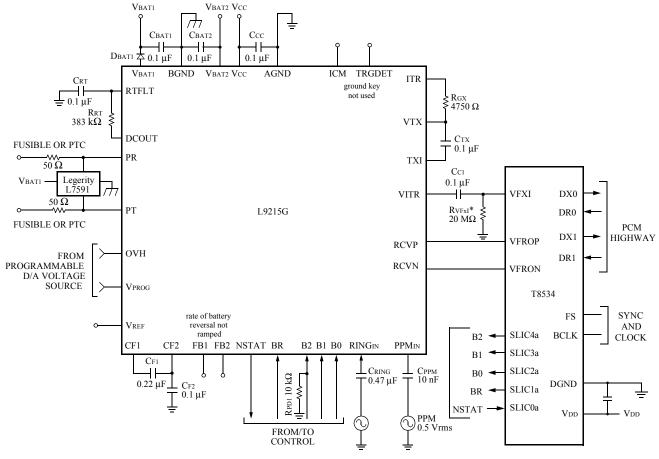

| POTS Interface                                       |      |

|                                                      | . 42 |

| TablePa                                              | aσe  |

|                                                      | U    |

| Pin Assignments, 44-Pin PLCC, Per-Channel Functions  |      |

| Pin Assignments, 44-Pin PLCC, Common Functions       |      |

| Pin Assignments, 64-Pin TQFP, Per-Channel Functions  |      |

| Pin Assignments, 64-Pin TQFP, Common Functions       |      |

| Bit Assignments for Fast Scan Mode                   |      |

| Absolute Maximum Ratings                             |      |

| Operating Ranges                                     |      |

| Handling Precautions                                 |      |

| dc Characteristics                                   |      |

| Analog Interface                                     |      |

| Power Requirements                                   |      |

| Transmission Characteristics                         |      |

| Per-Channel Noise Characteristics                    |      |

| Distortion and Group Delay                           |      |

| Crosstalk                                            |      |

| Timing Characteristics                               |      |

| Echo Canceller Characteristics                       |      |

| Memory Mapping                                       |      |

| Control Bit Definition                               | . 37 |

## **Functional Description**

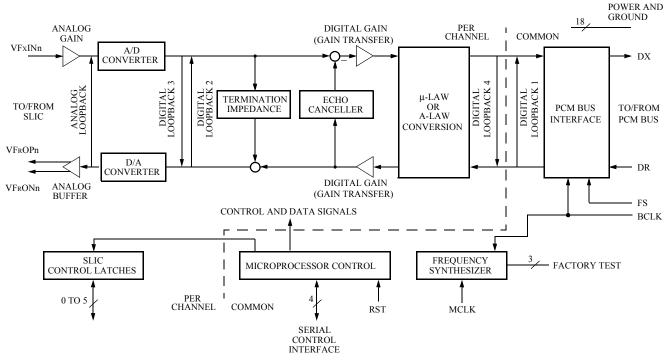

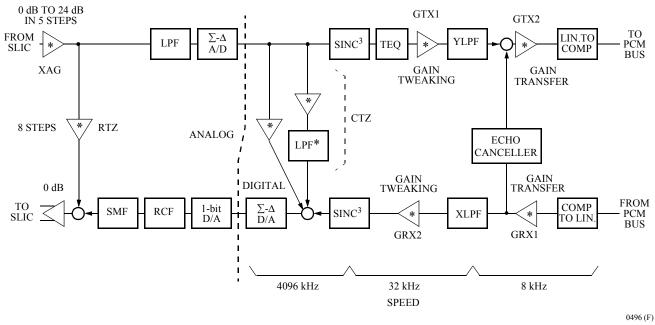

Refer to Figure 1 for the following discussion. (It should be noted that much of the processing is performed in a digital processor; thus, the actual data flow may be different than this functional, analog analogy based diagram shows.)

5-7172 (F).b

Figure 1. Functional Block Diagram, Each Section

This device performs virtually all the signal processing functions associated with a central-office line termination. Functionality includes line termination impedance synthesis, adaptive or fixed hybrid balance (echo canceller), and level conversion both in the analog sense (transmit equalization), to accommodate various subscriber line interface circuits (SLICs), and in the digital sense, for adjustment of the levels on the PCM bus (gain transfer). In general, the termination impedance synthesis generates the equivalent of a circuit with the parallel combination of a capacitor and a resistor in series with a resistor or the parallel combination of a resistor and the series combination of a resistor and capacitor. These general forms of impedance characteristic will satisfy most of the requirements specified throughout the world. Programmable selection of either µ-law or A-law encoding further aids worldwide deployment. In addition to the programmable features for impedance and coding, the device also contains an echo canceller that meets international requirements for network echo cancellers. This includes the ability to automatically disable the adaptation in the presence of 2100 Hz modem tones. All coefficients used in the filtering algorithms can be computed off-line in advance and downloaded to the device at the time of powerup. All signal processing is contained within the device, and there are only three interfaces of consequence to the system designer: the SLIC interface, the PCM interface, and the control interface.

The SLIC interface is designed to be flexible and convenient to use with a variety of SLIC circuits. With an appropriate choice of SLIC, no external components are required in the interface, with the exception of a dc blocking capacitor in the transmit direction. In some cases, dc blocking capacitors in the receive direction may be necessary as well, since the device operates from a single 5 V supply.

The PCM bus interface is flexible in that it allows, independently, the transmit and receive data for any channel to be placed in any time slot. The bus can be operated at a maximum of a 16.384 Mbits/s rate to accommodate a maximum of 256 time slots. Separate pins are provided for each direction of transmission to allow 4-wire bus operation. The frame strobe signal is an 8 kHz signal that defines the beginning of the frame structure. The interface will count 8 bits per time slot and insert or read the data for each channel as programmed. Lower speeds of the PCM bus are allowed. The PCM clock must be synchronous with the master clock for the device (if present) and with the frame strobe signal. The microprocessor control interface is a serial interface that uses the classic chip select type of operation. The interface controls the device by writing or reading various internal addresses. The command set comprises simple read and write operations, with the address determining the effect. All the memory locations, including the per-chip functions, are organized by channel, allowing a straightforward migration path to architectures other than quad.

There are several test modes included to facilitate confirmation of correct operation. In the signal path, both an analog and four digital loopback tests are available; while in the microprocessor interface, there is a write/read test mode that tests the operation of the memory. Use of external test access switches allows a complete test of the signal path through the line card so that correct operation of various operational modes can be verified.

## **Pin Information**

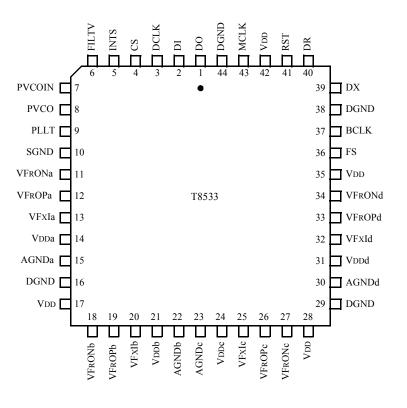

5-8195 (F)

Figure 2. 44-Pin PLCC Pin Diagram

| Ckt     |                                |    | Name | Туре  | Name/Description |                                                                                          |  |  |  |

|---------|--------------------------------|----|------|-------|------------------|------------------------------------------------------------------------------------------|--|--|--|

| a b c d |                                |    |      |       |                  |                                                                                          |  |  |  |

| 15      | 22                             | 23 | 30   | AGND  | GND              | alog Ground. A common AGND, DGND, SGND plane is highly recommended.                      |  |  |  |

| 14      | 21                             | 24 | 31   | Vdd   | PWR              | V Analog Power Supply.                                                                   |  |  |  |

| 13      | 20                             | 25 | 32   | VFxI  | Ι                | cansmit Analog Input. For complex terminations, this node requires a 10 M $\Omega$ or 20 |  |  |  |

|         | M $\Omega$ resistance to AGND. |    |      |       |                  |                                                                                          |  |  |  |

| 12      | 19                             | 26 | 33   | VFROP | 0                | ceive Analog Output, Positive Polarity.                                                  |  |  |  |

| 11      | 18                             | 27 | 34   | VFRON | 0                | Receive Analog Output, Negative Polarity.                                                |  |  |  |

## Pin Information (continued)

## Table 2. Pin Assignments, 44-Pin PLCC, Common Functions

| Pin            | Name   | Туре | Name/Description                                                                                                                                                                                                                       |  |  |  |

|----------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1              | DO     | 0    | Serial Data Output. This is a 3-state output.                                                                                                                                                                                          |  |  |  |

| 2              | DI     | Ι    | Serial Data Input.                                                                                                                                                                                                                     |  |  |  |

| 3              | DCLK   | Ι    | Serial Data Clock Input.                                                                                                                                                                                                               |  |  |  |

| 4              | CS     | Ι    | Chip Select Input. This pin determines the interval that the serial interface is active.                                                                                                                                               |  |  |  |

| 5              | INTS   | Ι    | Serial Interface Select. Leaving this pin open places the serial interface in the normal mode; grounding it places the interface into the byte-by-byte mode. This pin has an internal pull-up.                                         |  |  |  |

| 6              | FILTV  | PWR  | Frequency Synthesizer Power (5 V). This pin must be tied to VDD.                                                                                                                                                                       |  |  |  |

| 7              | PVCOIN |      | nal Test Point. Do not connect to this pin.                                                                                                                                                                                            |  |  |  |

| 8              | PVCO   | —    | Internal Test Point. Do not connect to this pin.                                                                                                                                                                                       |  |  |  |

| 9              | PLLT   |      | Internal Test Point. Do not connect to this pin.                                                                                                                                                                                       |  |  |  |

| 10             | SGND   | GND  | <b>nthesizer Ground.</b> Connect to DGND. A common AGND, DGND, SGND plan highly recommended.                                                                                                                                           |  |  |  |

| 16, 29, 38, 44 | DGND   | GND  | <b>gital Ground.</b> Logic ground and return for logic power supply. A common AGND, GND, SGND plane is highly recommended.                                                                                                             |  |  |  |

| 17, 28, 35, 42 | Vdd    | PWR  | Digital Power Supply (5 V).                                                                                                                                                                                                            |  |  |  |

| 36             | FS     | Ι    | <b>PCM Frame Strobe Input.</b> This 8 kHz clock must be derived from the same source as BCLK. See the Clocking Considerations section.                                                                                                 |  |  |  |

| 37             | BCLK   | Ι    | <b>PCM Clock Input.</b> This pin is used to develop internal clocks for certain clock rates. See the Clocking Considerations section.                                                                                                  |  |  |  |

| 39             | DX     | 0    | PCM Bus Output Pin. This is a 3-state output.                                                                                                                                                                                          |  |  |  |

| 40             | DR     | Ι    | PCM Bus Input Pin.                                                                                                                                                                                                                     |  |  |  |

| 41             | RST    | Ι    | <b>Power-On Reset.</b> A low causes a reset of the entire chip. This pin may be connected to DGND with a 0.1 $\mu$ F capacitor for a power-on reset function, or it may be driven by external logic. This pin has an internal pull-up. |  |  |  |

| 43             | MCLK   | Ι    | <b>1.024 MHz Master Clock Input.</b> Internal timing is derived from this clock input for certain PCM bus rates. See the Clocking Considerations section. When unused, this pin may be left open. This pin has an internal pull-up.    |  |  |  |

## Pin Information (continued)

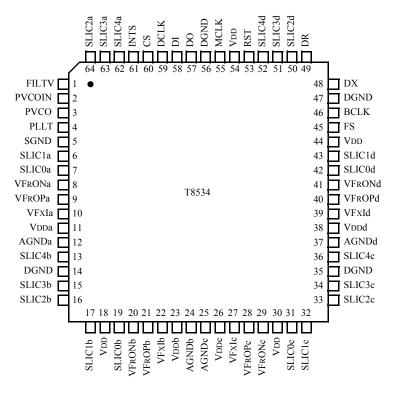

5-8196 (F)

Figure 3. 64-Pin TQFP Pin Diagram

| Table 5. I in Assignments, 04-1 in 1 Q11, 1 ci-Channel I unctions | Table 3. Pin | Assignments, | 64-Pin | TQFP, | <b>Per-Channel Functions</b> |

|-------------------------------------------------------------------|--------------|--------------|--------|-------|------------------------------|

|-------------------------------------------------------------------|--------------|--------------|--------|-------|------------------------------|

|    | С  | kt |    | Name  | Туре | Name/Description                                                                                 |  |  |  |  |

|----|----|----|----|-------|------|--------------------------------------------------------------------------------------------------|--|--|--|--|

| a  | b  | c  | d  |       |      |                                                                                                  |  |  |  |  |

| 12 | 24 | 25 | 37 | AGND  | GND  | log Ground. A common AGND, DGND, SGND plane is highly recommended.                               |  |  |  |  |

| 11 | 23 | 26 | 38 | Vdd   | PWR  | 5 V Analog Power Supply.                                                                         |  |  |  |  |

| 10 | 22 | 27 | 39 | VFxI  | Ι    | <b>Transmit Analog Input.</b> For complex terminations, this node requires a 10 M $\Omega$ or 20 |  |  |  |  |

|    |    |    |    |       |      | Ω resistance to AGND.                                                                            |  |  |  |  |

| 9  | 21 | 28 | 40 | VFROP | 0    | Receive Analog Output, Positive Polarity.                                                        |  |  |  |  |

| 8  | 20 | 29 | 41 | VFRON | 0    | Receive Analog Output, Negative Polarity.                                                        |  |  |  |  |

| 7  | 19 | 31 | 42 | SLIC0 | I/O  | SLIC Control Pin 0.                                                                              |  |  |  |  |

| 6  | 17 | 32 | 43 | SLIC1 | I/O  | SLIC Control Pin 1.                                                                              |  |  |  |  |

| 64 | 16 | 33 | 50 | SLIC2 | I/O  | SLIC Control Pin 2.                                                                              |  |  |  |  |

| 63 | 15 | 34 | 51 | SLIC3 | I/O  | SLIC Control Pin 3.                                                                              |  |  |  |  |

| 62 | 13 | 36 | 52 | SLIC4 | I/O  | SLIC Control Pin 4.                                                                              |  |  |  |  |

## Pin Information (continued)

## Table 4. Pin Assignments, 64-Pin TQFP, Common Functions

| Pin            | Name   | Туре | Name/Description                                                                                                                                                                                                                    |  |  |

|----------------|--------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1              | FILTV  | PWR  | Frequency Synthesizer Power (5 V). This pin must be tied to VDD.                                                                                                                                                                    |  |  |

| 2              | PVCOIN | _    | Internal Test Point. Do not connect to this pin.                                                                                                                                                                                    |  |  |

| 3              | PVCO   |      | Internal Test Point. Do not connect to this pin.                                                                                                                                                                                    |  |  |

| 4              | PLLT   |      | Internal Test Point. Do not connect to this pin.                                                                                                                                                                                    |  |  |

| 5              | SGND   | GND  | <b>Synthesizer Ground.</b> Connect to DGND. A common AGND, DGND, SGND plane is highly recommended.                                                                                                                                  |  |  |

| 14, 35, 47, 56 | DGND   | GND  | <b>Digital Ground.</b> Logic ground and return for logic power supply. A common AGND, DGND, SGND plane is highly recommended.                                                                                                       |  |  |

| 18, 30, 44, 54 | Vdd    | PWR  | al Power Supply (5 V).                                                                                                                                                                                                              |  |  |

| 45             | FS     | Ι    | <b>A Frame Strobe Input.</b> This 8 kHz clock must be derived from the same source CLK. See the Clocking Considerations section.                                                                                                    |  |  |

| 46             | BCLK   | Ι    | <b>M Clock Input.</b> This pin is used to develop internal clocks for certain clock rates the Clocking Considerations section.                                                                                                      |  |  |

| 48             | DX     | 0    | M Bus Output Pin. This is a 3-state output.                                                                                                                                                                                         |  |  |

| 49             | DR     | Ι    | A Bus Input Pin.                                                                                                                                                                                                                    |  |  |

| 53             | RST    | Ι    | <b>Ver-On Reset.</b> A low causes a reset of the entire chip. This pin may be connected GND with a 0.1 $\mu$ F capacitor for a power-on reset function, or it may be driven by rnal logic. This pin has an internal pull-up.        |  |  |

| 55             | MCLK   | Ι    | <b>1.024 MHz Master Clock Input.</b> Internal timing is derived from this clock input for certain PCM bus rates. See the Clocking Considerations section. When unused, this pin may be left open. This pin has an internal pull-up. |  |  |

| 57             | DO     | 0    | Serial Data Output. This is a 3-state output.                                                                                                                                                                                       |  |  |

| 58             | DI     | Ι    | Serial Data Input.                                                                                                                                                                                                                  |  |  |

| 59             | DCLK   | Ι    | Serial Data Clock Input.                                                                                                                                                                                                            |  |  |

| 60             | CS     | Ι    | Chip Select Input. This pin determines the interval that the serial interface is active.                                                                                                                                            |  |  |

| 61             | INTS   | Ι    | Serial Interface Select. Leaving this pin open places the serial interface in the normal mode; grounding it places the interface into the byte-by-byte mode. This pin has an internal pull-up.                                      |  |  |

## **Functional Description**

#### **Clocking Considerations**

This device has several clock inputs for the various interfaces. The PCM bus uses BCLK as the bit clock and the onegoing edge of FS to determine the location of the beginning of a frame. These two clocks must be derived from the same source. Internally, the device develops all the internal clocks with a phase-locked loop that uses BCLK as the timing source when BCLK is 16.384, 8.192, 4.096, 2.048, or 1.024 MHz. In these instances, MCLK is not used and may be left open since any signal driving MCLK is ignored. For BCLK rates of 256 kHz and 512 kHz, MCLK is used as a source for the PLL and must be 1.024 MHz. In this latter case, BCLK, MCLK, and FS must be derived from the same source and the rising edge of BCLK must be within 10 ns of the rising edge of MCLK. BCLK, FS, and MCLK (if required) must be continuously present and without gaps in order for the device to operate correctly. Note that the nominal values in Table 16 are the valid frequencies for BCLK.

DCLK is used to clock the internal serial interface and may be asynchronous to the other clocks. There is no need to derive this clock from the same source as the other clocks. The serial bus may be operated at any speed up to 4.096 Mbits/s. DCLK can be gapped; however, additional clock cycles are required in and around the command frame to process data, and during and after a hardware or a software reset to ensure complete clearing of internal logic. There is no limit on the number of devices on the same serial bus.

### **The Control Interface**

The device is controlled via a series of memory locations accessed by a serial data connection to the external master controller. This interface operates using the chip select lead to enable transmission of information. All chip functions are enabled or disabled by setting or clearing bits in the control memory. Filter coefficients and gain adjustments are also stored in this memory.

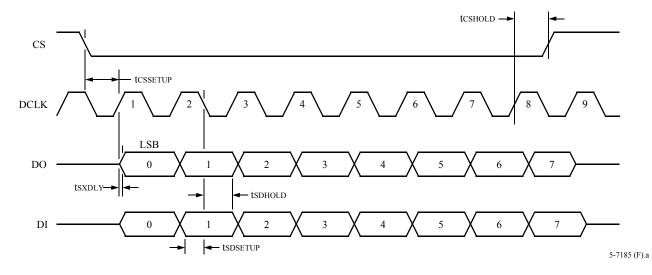

The codec has both a serial input lead and a serial output lead. These may be used individually for a 4-wire serial interface, or tied together for a 2-wire interface. The line driver circuitry is capable of driving relatively high currents so that in the event that the line is long enough to show significant transmission line effects, it can be terminated in the characteristic impedance at each end with resistors to Vcc and ground. All data transfers on the serial bus are byte oriented with the least significant bit (shown in this data sheet as bit 0) transmitted first, followed by the more significant bits. For data fields, the least significant byte of the first data byte is transmitted first, followed by the more significant bytes, each byte transmitted LSB first. This format is compatible with the serial port on most microcontrollers.

#### Modes

There are two different modes of operation for the serial interface, the normal mode and the byte-by-byte mode. These two modes differ in the manner in which CS is used to control the transfer. Note that the CS lead is used to control the transfer of serial data from master controller to slave codec and in the reverse direction.

In normal mode, (INTS pin open) the CS lead must go low for the duration of the transfer. The only error check performed by the codec is to verify that CS is low for an integral number of bytes. Detection of an active (active-low) chip select for other than an integral multiple of 8 bits results in the operation being terminated. The next active excursion of chip select will be interpreted as a new command; hence, the serial I/O interface can always be initialized by asserting CS for a number of clock periods that is not an integral multiple of 8. CS is captured using DCLK, so DCLK must be transitioned to perform this initialization. Undefined command codes are reserved for future use and may cause unwanted operation of the device.

The byte-by-byte mode (INTS pin tied to ground) uses CS to control each byte of the transfer. In this mode, CS goes low for exactly 8 bits at a time, corresponding to a 1-byte transfer either to or from the codec chip. Repeated transitions of CS are used to control subsequent bytes of data to/from the codec. For a write command in this mode, CS must go low for each byte of the transfer until the transfer is complete. For a read command, CS will go low for each of the 3 bytes of the read command transferred to the device, and then low again for each byte to be read. Notice that the total number of bytes transferred (and excursions on CS) is N + 3, where N is the number of bytes to be read in the command. This mode of operation is useful in cases where the master is a microprocessor with a built-in UART that transfers 1 byte at a time. Error detection is limited to detection of an active CS for other than an integral multiple of 8 bits. Recovery is the same as normal mode. Note that the clock phase is shifted in this mode.

Flow control can be accomplished by suspending the transitions on DCLK by holding either state. During the data transfer, CS must remain low while clock transitions are suspended with DCLK in either state.

#### The Control Interface (continued)

#### Protocol

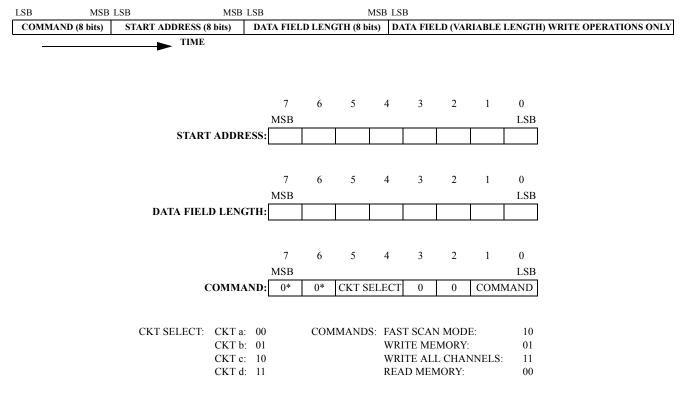

The format of the command protocol is shown in Figures 4 and 5.

The control interface operates with one external master controller and multiple slave codec devices. Each transfer is initiated by the master, and the slave responds for either read operations or the fast scan mode. The slave does not check the bus for activity prior to transmitting; it only checks for an active CS. The master should allow for a wait between the end of a read command until CS becomes active for the read data. The master must refrain from sending additional commands to the slave chip until the response is received. On a 4-wire bus, commands to other devices may be initiated before the response is received, but care in generating the CS function is needed to ensure that the multiple responses do not interfere. It should be noted that multiple memory locations can be accessed in the same command by setting the data field length field to the desired number of bytes to be transferred. If flow control is desired, it must be performed by using separate commands, each transferring smaller blocks of information, or by controlling the serial clock (gapping the serial clock), or with CS in the case of byte-bybyte mode.

There is no response from the slave to the master for a write operation. The response to a read operation simply includes the data to be read in the data field. This data is sent least significant bit first, with the bytes sent in ascending sequence. Commands from the master controller include data for write operations, but not for read operations. Since the coefficients and gains are stored in volatile memory, all the coefficients and gains must be loaded after powerup. There is, however, no need to reload them when switching from active to standby modes, or vice versa. Great care should be exercised in loading memory when the codec channel is not in standby mode. Sudden changes in the termination or balance impedances can result in undesirable system operation.

All data is transmitted in a byte-oriented fashion with the least significant bit of each byte transferred first. Multibyte fields are transferred least significant byte first in both directions. The data field will contain the first addressed data location first, with subsequent data locations transmitted in ascending order.

#### The Control Interface (continued)

**Protocol** (continued)

\* Location of memory bank selection. All user controls are in memory bank 0; other memory banks contain internal state information for the device.

Note: Data field length is in bytes for all operations. All data is transmitted in bytes with the LSB for each byte transmitted first. For 16-bit memory operations, the least significant byte of the first memory location is transmitted first, followed by the most significant byte; each byte is transmitted LSB first. Additional memory locations are loaded in ascending sequence.

#### Figure 4. Command Frame Format, Master to Slave, Read or Write Commands

#### DATA FIELD (VARIABLE LENGTH) READ OPERATIONS ONLY

Note: All data is transmitted in bytes with the LSB for each byte transmitted first. For memory operations, the least significant byte of the first memory location is transmitted first, followed by the most significant byte, each byte transmitted LSB first. Additional memory locations are loaded in ascending sequence.

Figure 5. Command Frame Format, Slave to Master, Read Commands

LSB

### The Control Interface (continued)

#### Write Command

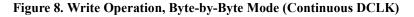

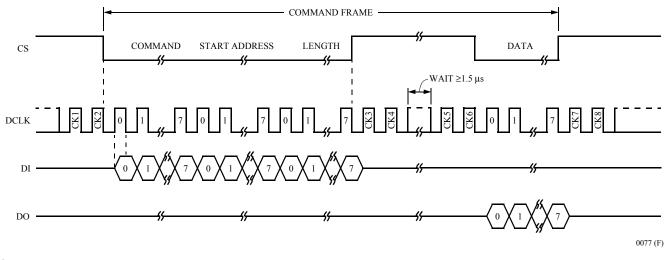

A write command is used to write to the memory addresses. Figures 6—9 illustrate normal or byte-by-byte operation with continuous or gapped DCLKs. For gapped DCLK operation, transitions, not frequency, are critical (as long as transitions occur no faster than 122 ns apart).

\* Two or more full DCLK cycles are required before the start of a new command frame.

Note: Data field length of 1 shown.

Notes:

Data field length of 1 shown.

CK1 through CK4 are additional DCLK pulses required to properly process the data.

CK3 and CK4 are not necessary if another command frame follows this sequence.

#### Figure 7. Write Operation, Normal Mode (Gapped DCLK)

#### The Control Interface (continued)

#### Write Command (continued)

\* Two or more full DCLK cycles are required before the start of a new command frame.

Note: Data field length of 1 shown.

Notes:

Data field length of 1 shown.

CK1 through CK4 are additional DCLK pulses required to properly process the data.

CK3 and CK4 are not necessary if another command frame follows this sequence.

Figure 9. Write Operation, Byte-by-Byte Mode (Gapped DCLK)

#### The Control Interface (continued)

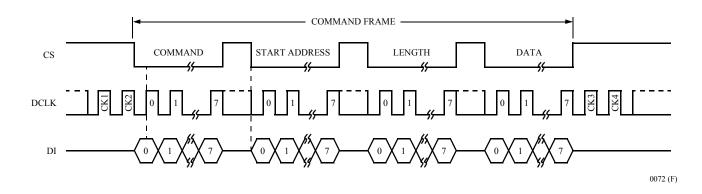

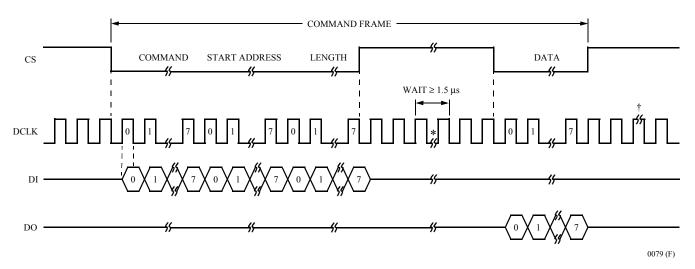

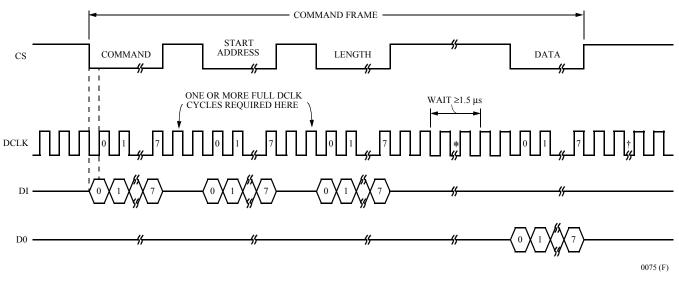

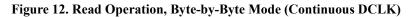

#### **Read Command**

The normal flow of information to the master controller is always in response to a read command. All control memory locations are accessed in 8-bit bytes. All read commands from the master controller require a response from the addressed codec. It is the responsibility of the master controller to ensure that only one device is transmitting on the serial interface line at any one time. The master controller also must ensure that the CS lead goes high after transferring the 3-byte sequence used to initiate the read, and then it goes low again for the response. In this case, it should be noted that the device expects the second time CS goes low that data is to be sent to the master; thus, it does not interpret the DI lead as containing a valid instruction during that CS excursion and a write during this time is not recommended. Note also that the CS lead must allow the number of bytes sent in a read command to be transferred before a subsequent command can be received by the codec. Figures 10—13 illustrate normal or byte-by-byte operation with continuous or gapped DCLKs. Like a write command, transitions, not frequency, are critical with regard to gapped DCLK operation.

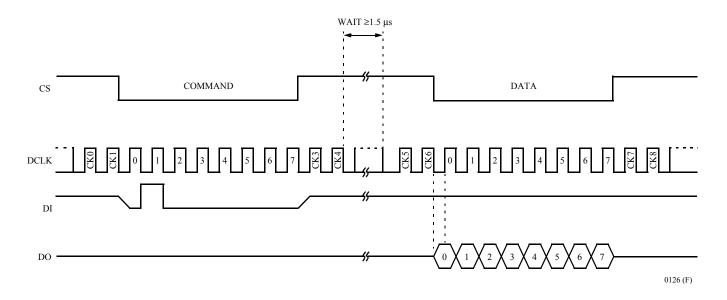

\* Provide sufficient wait time to access read data. Provide sufficient DCLK cycles to effectively wait ≥1.5 µs after the second full DCLK cycle and before the second to last full DCLK cycle. DCLK operation of 4.096 MHz would require 10 cycles of DCLK between LENGTH and DATA. The first two DCLK cycles, when CS goes high, process the command. A wait is then required to access the read data. Two final DCLK cycles are required to process the read data.

† Two or more DCLK cycles are required before the start of a new command frame.

Note: Data field length of 1 shown.

#### Figure 10. Read Operation, Normal Mode (Continuous DCLK)

### The Control Interface (continued)

#### Read Command (continued)

Notes:

Data field length of 1 shown.

CK1 through CK8 are additional DCLK pulses required to properly process the data.

CK7 and CK8 are not necessary if another command frame follows this sequence.

### Figure 11. Read Operation, Normal Mode (Gapped Clock)

#### The Control Interface (continued)

#### Read Command (continued)

\* Provide sufficient wait time to access read data. Provide sufficient DCLK cycles to effectively wait ≥1.5 µs after the second full DCLK cycle and before the second to last full DCLK cycle. DCLK operation of 4.096 MHz would require 10 cycles of DCLK between LENGTH and DATA. The first two DCLK cycles, when CS goes high, process the command. A wait is then required to access the read data. Two final DCLK cycles are required to process the read data.

† Two or more DCLK cycles are required before the start of a new command frame.

Note: Data field length of 1 shown.

### The Control Interface (continued)

Read Command (continued)

Notes:

Data field length of 1 shown.

CK1 through CK8 are additional DCLK pulses required to properly process the data.

CK7 and CK8 are not necessary if another command frame follows this sequence.

#### The Control Interface (continued)

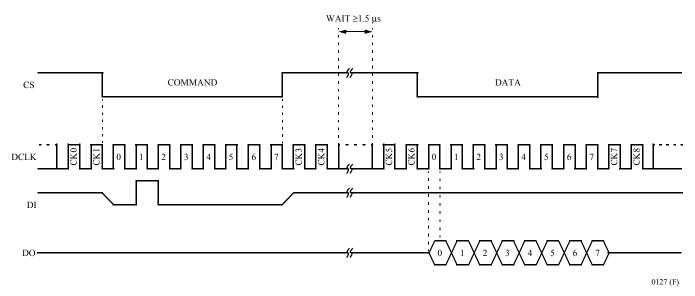

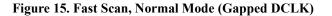

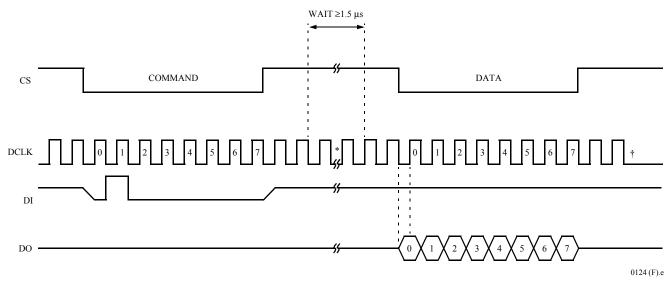

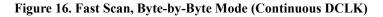

#### Fast Scan Mode

The fast scan mode allows a single byte command to read two SLIC control leads for all four channels with a 1-byte reply. This mode significantly speeds up the normal scanning for off-hook, ring trip, and ring ground detection. This special command sequence allows the controlling microprocessor to fast scan 2 bits in the SLIC control byte of each of the four channels. The command code is (00000010)2; there are no start address or length fields. The command returns only a single byte of data, formatted as shown in Table 5.

| Bit     | Reported Status                              |

|---------|----------------------------------------------|

| 0 (LSB) | Channel 0, bit 0 (ckt a, address 160, bit 0) |

| 1       | Channel 0, bit 1 (ckt a, address 160, bit 1) |

| 2       | Channel 1, bit 0 (ckt b, address 160, bit 0) |

| 3       | Channel 1, bit 1 (ckt b, address 160, bit 1) |

| 4       | Channel 2, bit 0 (ckt c, address 160, bit 0) |

| 5       | Channel 2, bit 1 (ckt c, address 160, bit 1) |

| 6       | Channel 3, bit 0 (ckt d, address 160, bit 0) |

| 7 (MSB) | Channel 3, bit 1 (ckt d, address 160, bit 1) |

The circuit select in the command structure (Figure 4) is not used for this special single-byte command. The rules for toggling chip select apply as for the read command. Figures 14—17 illustrate normal or byte-by-byte operation with continuous or gapped DCLKs.

\* Provide sufficient wait time to access read data. Provide sufficient DCLK cycles to effectively wait ≥ 1.5 µs after the second full DCLK cycle and before the second to last full DCLK cycle. DCLK operation of 4.096 MHz would require 10 cycles of DCLK between COMMAND and DATA. The first two DCLK cycles, when CS goes high, process the command. A wait is then required to access the read data. Two final DCLK cycles are required to process the read data.

† Two or more DCLK cycles are required before the start of a new command frame.

#### Figure 14. Fast Scan, Normal Mode (Continuous DCLK)

## The Control Interface (continued)

Fast Scan Mode (continued)

Note: CK1 through CK8 are additional DCLK pulses required to properly process the data.

### The Control Interface (continued)

#### Fast Scan Mode (continued)

\* Provide sufficient wait time to access read data. Provide sufficient DCLK cycles to effectively wait ≥1.5 µs after the second full DCLK cycle and before the second to last full DCLK cycle. DCLK operation of 4.096 MHz would require 10 cycles of DCLK between COMMAND and DATA. The first two DCLK cycles, when CS goes high, process the command. A wait is then required to access the read data. Two final DCLK cycles are required to process the read data.

† Two or more DCLK cycles are required before the start of a new command frame.

Note: CK1 through CK8 are additional DCLK pulses required to properly process the data.

Figure 17. Fast Scan, Byte-by-Byte Mode (Gapped DCLK)

#### The Control Interface (continued)

#### Write All Channels

The write all channels command causes all four channels to be loaded with the same coefficients with a single data transfer from the master controller. This allows for a faster initialization of the device after a powerup. This command should be used with caution since it affects all four channels. The normal memory write and read commands affect only one channel.

#### **Reset Functionality**

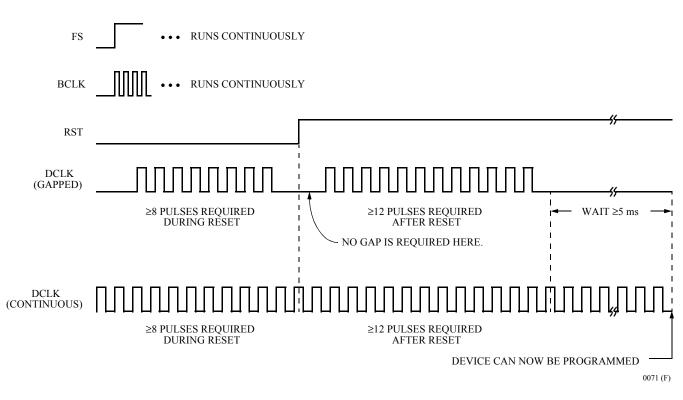

Figure 18. Hardware Reset Procedure

The reset function allows the internal logic of the device to be set to a known initial condition, either externally by activating the reset lead, or on a per-channel basis through the microprocessor interface by setting and then clearing bits, if required, in address RESCTRL (address 128). These two reset functions have different effects, and each of the software reset functions is a subset of the hardware reset functionality. The primary difference is in the treatment of the internal memory. The hardware reset is assumed to be a result of a catastrophic hardware event, such as a loss of power or an initial powerup. Accordingly, the assumption is made that the internal memory does not contain valid data, and default values for all memory locations are loaded. A software reset, however, can only be initiated if the device is operational (at least the microprocessor interface), so the contents of the memory may indeed be valid; thus, the resets may be more specific. Additionally, software resets only affect the selected channel.

#### Reset Functionality (continued)

A 0.1  $\mu$ F capacitor between the RST lead and ground will effectively hold the lead low long enough to reset the device on powerup, allowing for a cost-effective power-on reset function. Notice that the memory must be reloaded through the serial interface after a hardware reset function. For proper operation, it is necessary for FS and BCLK to be present and stable during a reset. DCLK transitions (frequency is not critical as long as the maximum rate is not exceeded) are also required in order for all internal logic to be properly cleared as is a wait period for the internal PLL to stabilize. See the timing diagram shown in Figure 18 for the proper hardware or power-on reset procedure.

For a software reset, the control memory should not be accessed for a minimum of 256 µs following the reset.

#### **Memory Control Mapping**

Several memory locations are used to control the device. The software interface tables (Table 18 and Table 19) show the memory assignments that are useful in call processing and system testing. It should be noted that other memory locations are used by the device to hold intermediate results and other device state information. Writing to these other locations can cause serious disruptions in the operation of the device and should be avoided.

### **Standby Mode**

The device enters a low-power standby mode with powerup or software reset, or by programming the CHACTIVE register 129, bit 0. In standby mode, the control interface is active, capable of writing or reading registers. SLIC read and write data latches are also active. Analog signals at VFxI and PCM signals at DR are ignored in this mode. BCLK must be present for proper standby mode operation.

### **Test Capabilities**

The device has several built-in test capabilities that can be used to verify correct operation of the signal processing of the line card. These test functions are accessed in several different control addresses. Five loopback modes are employed (the first four in the list below are digital loopbacks):

- Digital 1. Allows the digital signal from the PCM bus to be looped back to the PCM bus. This loopback facility can be used to verify correct operation of the PCM bus interface logic, as well as operation of the PCM bus.

- Digital 2. Allows complete testing of the digital processing capability of the codec by looping the data back at the analog/digital conversion interface.

- Digital 3. This loopback function is at the digital side of the sigma-delta mode converters and loops analog transmit data back to the analog receive path.

- Digital 4. This loopback is at the PCM bus interface and loops the transmit data from the line back to the receive path.

- Analog 5. The analog loopback facility can be used to check the operation of all the signal processing performed in the device, including the conversions to/from analog.

Three of these loopback functions (digital 1 and 2, and the analog loopback) can be used with tone generation and reception via the PCM bus.

By assigning the transmit and receive time slots identically, a loopback arrangement at the PCM bus can be effectively programmed for signals generated on the line side of the codec. This mode is useful for testing from the line side through the entire device.

An optional 16-bit encoding mode is included on a perchannel basis for use in various test scenarios, or for use by an external digital signal processor. This mode of operation differs from the companded modes in both the bit order and the use of multiple time slots on the PCM bus.

#### **Echo Canceller Functionality**

The echo canceller has three sets of coefficient memory storage locations. One, called HPRE, contains the default balance coefficients and can be accessed as memory addresses 0—127. This serves as the coefficients for a fixed balance network (adaptation disabled), or as a starting point for echo cancellation. The contents of these memory locations do not change with adaptation. The adaptation coefficients, which are added to the corresponding coefficients in HPRE, are stored in the HHAT area. Normally, the user has no need to access these coefficients; thus, these addresses are not described in this data sheet. The HHAT coefficients cover either the first 8, 16, 32, or the entire 64-tap length of the balance filter, depending on the settings in the LMSGAIN address. Note that all echo canceller length options in this control location may not be implemented, but are reserved for future use.

A third set of coefficients is contained in HDTA, which is used for special data call functions.

#### **SLIC Control Capabilities**

Memory locations 158, 159, and 160 are used to control five bidirectional latches that are intended to allow the serial interface to control other line card devices, such as ringing/ test switches, telecom electromechanical relays, and SLIC devices. When the TTL latches are configured as outputs, external devices should be set up to sink current from the latch. Location 158 sets the operational mode of these latches as either inputs or outputs. Location 159 specifies what is to be written on the latch leads driven by the device. Location 160 reports the actual state of these leads. It should be noted that a channel control reset forces all of these external leads, except those corresponding to bits 2 and 3, to the high-impedance state, so any inputs connected to bits 0, 1, 4, and 5 should have appropriate pull-up or pull-down resistors (off-chip, if required) to force the external device into a known state at power-up or in the event of a reset. Bits 2 and 3 will reset to outputs with a value of zero.

The fast scan mode allows for a minimal data transfer on the serial bus to monitor bits 0 and 1 of the SLIC data memory location (159). If these 2 bits are wired as inputs to the off-hook and/or ring ground detection circuits, a convenient method of rapidly scanning for these two functions is obtained. Bits 2 and 3 default to outputs; thus, they are convenient to provide control of the SLIC state. In any event, all six leads are programmable for maximum flexibility.

#### **Suggested Initialization Procedures**

It is suggested that upon powerup, a hardware reset be used to set the device into a known state. The serial interface should then be used to load the memory addresses that differ from the default values (the write all channels command is convenient for this function). If other devices are controlled by the SLIC data memory location, then it also should be loaded with a known configuration. After the completion of this sequence, the device is ready to be activated. Depending on the application, the next step may either be normal operation or a set of test sequences. After the initialization of the memory, the device and associated line card devices can be controlled by using memory locations 130, 131, 145, 155, 156, 157, 158, 159, and 129; that is, by supplying the PCM bus time-slot addresses, switching the SLIC into the proper mode, and activating the codec. Within memory location 129, the codec would normally be placed into active mode, with both directions of the PCM bus enabled at the start of a call. At the completion of a call, the codec should be placed into standby mode and the PCM bus disabled. Great caution should be used when changing the memory while the codec is in active mode, since termination impedances, balance impedances, and gains may change. These changes are likely to yield undesirable system effects. It is safe to refresh coefficients that are known to be unchanging in the application. It is always possible to read the memory to verify its contents without deleterious effects on codec operation. Normal operation would load the memory and perform all gain adjustments while the codec is in standby mode. Under no circumstances should memory above address 162 be written, since this section of memory is used for state data and intermediate results. Also, all reserved addresses should not be written. Changing this information may have deleterious effects on system operation.

### **Signal Processing**

Figure 19 details the signal processing functional blocks of one channel of the codec.

\* Programmable blocks.

## **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational section of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

#### **Table 6. Absolute Maximum Ratings**

| Parameter                                          | Symbol | Min   | Max  | Unit |

|----------------------------------------------------|--------|-------|------|------|

| Storage Temperature Range                          | Tstg   | -55   | 150  | °C   |

| Power Supply Voltage (all pins designated power)   | VDDX   | _     | 7    | V    |

| Negative Voltage on Any Pin with Respect to Ground | Vss    | -0.25 |      | V    |

| Thermal Resistance, Junction to Case (64-pin MQFP) | Røjc   |       | 35   | °C/W |

| Package Power Dissipation (64-pin MQFP)            | Pd     |       | 1.14 | W    |

| Thermal Resistance, Junction to Case (44-pin PLCC) | Røjc   |       | 49   | °C/W |

| Package Power Dissipation (44-pin PLCC)            | Pd     | _     | 815  | mW   |

## **Operating Ranges**

#### Table 7. Operating Ranges

| Parameter                      | Symbol | Min | Max | Unit |

|--------------------------------|--------|-----|-----|------|

| Ambient Operating Temperature  | TA     | -40 | 85  | °C   |

| Operating Junction Temperature | τJ     | -40 | 125 | °C   |

## **Handling Precautions**

Although electrostatic discharge (ESD) protection circuitry has been designed into this device, proper precautions must be taken to avoid exposure to ESD and electrical overstress (EOS) during all handling, assembly, and test operations. Legerity employs both a human-body model (HBM) and a charged-device model (CDM) qualification requirement in order to determine ESD-susceptibility limits and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used in each of the models, as defined by JEDEC's JESD22-A114 (HBM) and JESD22-C101 (CDM) standards.

#### **Table 8. Handling Precautions**

| HBM ESD Threshold Voltage |         |  |  |  |  |

|---------------------------|---------|--|--|--|--|

| Device                    | Voltage |  |  |  |  |

| T8533/T8534               | >2000   |  |  |  |  |

## **Electrical Characteristics**

For all specifications:  $T_A = -40$  °C to +85 °C,  $V_{DD} = 5 V \pm 5\%$ , unless otherwise noted. Typical values are for  $T_A = 25$  °C and  $V_{DD} = 5 V$ . Input signal frequency is 1004 Hz, unless otherwise noted.

#### dc Characteristics

#### Table 9. dc Characteristics

| Parameter                                             | Symbol | Test Conditions                                                             | Min       | Тур | Max | Unit |

|-------------------------------------------------------|--------|-----------------------------------------------------------------------------|-----------|-----|-----|------|

| Input Voltage Low                                     | VIL    | All inputs                                                                  | —         |     | 0.8 | V    |

| Input Voltage High                                    | VIH    | All inputs                                                                  | 2.0       | —   | —   | V    |

| Input Current                                         | IIL    | Digital, without pull-up, inputs,<br>GND < V <sub>IN</sub> < V <sub>D</sub> | -10       |     | 10  | μA   |

|                                                       |        | With internal pull-up, VIN = GND<br>(INTS, MCLK, and RST pins)              | -240      | —   | 10  | μA   |

|                                                       |        | With internal pull-up, VIN = VDD<br>(INTS, MCLK, and RST pins)              | -10       |     | 10  | μA   |

| Output Voltage Low                                    | Vol    | IL = 3.2  mA                                                                | _         | _   | 0.4 | V    |

| Output Voltage High                                   | Voh    | $I_L = -320 \ \mu A$                                                        | 3.5       |     |     | V    |

| Output Current in High-impedance State                | Ioz    | GND < V <sub>OUT</sub> < V <sub>DD</sub>                                    | -30       |     | 30  | μA   |

| Line Driver (DX and DO pins) Output Volt-<br>age High | Vон    | $I_L = -10 \text{ mA}$                                                      | Vdd - 0.5 |     |     | V    |

| Line Driver (DX and DO pins) Output Voltage Low       | Vol    | $I_L = 10 \text{ mA}$                                                       |           |     | 0.5 | V    |

## **Analog Interface**

The following specifications pertain to the analog SLIC interface for each channel.

#### Table 10. Analog Interface

| Parameter                                                      | Symbol | Test Conditions                                                                     | Min  | Тур | Max | Unit |

|----------------------------------------------------------------|--------|-------------------------------------------------------------------------------------|------|-----|-----|------|

| Input Resistance                                               | Rvfxi  | $0.25 < V_{IN} < (V_{DDX} - 0.25) V$                                                | 100  | —   | 300 | kΩ   |

| Input Voltage                                                  | Vix    | Relative to ground<br>Signal should be capacitively<br>coupled to VFxI              |      | 2.0 | 2.2 | V    |

| Load Resistance at VFrOP and VFrON (differential)              | RL     | RL<br>RL<br>RL<br>RL<br>S-8881F                                                     | 7.5  |     |     | kΩ   |

| Output Resistance                                              | Ro     | Digital input code corresponding to idle<br>PCM code (µ-law)                        | —    | 2   | 10  | Ω    |

| Output Offset Voltage Between VFrOP<br>and VFrON               | Vos    | Digital input code corresponding to idle<br>PCM code (µ-law)                        | -100 | 0   | 100 | mV   |

| Output Offset Voltage Between<br>VFROP and VFRON, Standby Mode | Voss   | $R_L = 100 \text{ k}\Omega$                                                         | -20  | 0   | 20  | mV   |

| Common-mode Output Voltage,<br>Active Mode                     | Vocm   | Digital input code corresponding to alter-<br>nating $\pm$ zero $\mu$ -law PCM code |      | 2.0 | —   | V    |

| Common-mode Output Voltage,<br>Standby Mode                    | Vocms  |                                                                                     | 1.7  | 2.0 | 2.3 | V    |

## Analog Interface (continued)

#### Table 11. Power Requirements

| Parameter                         | Min  | Тур | Max  | Unit |

|-----------------------------------|------|-----|------|------|

| Operating Voltage:                |      |     |      |      |

| VDD                               | 4.75 | —   | 5.25 | V    |

| Vddx                              | 4.75 | —   | 5.25 | V    |

| Power Supply Current, VDD + VDDX: |      |     |      |      |

| All Channels in Standby Mode      | —    | —   | 35   | mA   |

| All Channels Active               | _    |     | 110  | mA   |

### **Transmission Characteristics**

#### **Table 12. Transmission Characteristics**

| Parameter                                       | Symbol | Test Conditions                                                                                                                                                                       | Min            | Тур   | Max          | Unit     |

|-------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|--------------|----------|

| Absolute Levels                                 | GAL    | Maximum 0 dBm0 levels (1004 Hz):<br>VFxI (encoder milliwatt), all programma-<br>ble transmit gains set to 0 dB                                                                        | _              | 2.80  |              | Vp-p     |

|                                                 |        | RCV (decoder milliwatt), termination<br>impedance off, all programmable receive<br>gains set to 0 dB                                                                                  | _              | 5.29  |              | Vp-p     |

|                                                 |        | Minimum 0 dBm0 levels (1004 Hz)<br>VFxI (encoder milliwatt)<br>XAG = 24 dB<br>GTX1 = 6 dB<br>GTX2 = 0 dB                                                                              | _              | 87.5  |              | mVp-p    |

|                                                 |        | RCV (decoder milliwatt), termination<br>impedance off<br>GRX1 = 0  dB<br>GRX2 = -6  dB                                                                                                |                | 2.63  |              | Vp-p     |

| Absolute Maximum Volt-                          | GAL    | VFxI                                                                                                                                                                                  |                | _     | 3.2          | Vp-p     |

| age Swings                                      |        | VFrOP to VFrON (differential)                                                                                                                                                         |                | —     | 5.28         | Vp-p     |

| Transmit Gain Absolute<br>Accuracy              | GXA    | Transmit gain programmed for maximum<br>0 dBm0 test level, measured deviation of<br>digital code from ideal<br>0 dBm0 level at DX digital outputs, with<br>transmit gain set to 0 dB: |                |       |              |          |

|                                                 |        | 20 °C to 70 °C                                                                                                                                                                        |                | ±0.15 |              | dB       |

|                                                 |        | 0 °C to 85 °C<br>-40 °C to +85 °C                                                                                                                                                     | -0.25<br>-0.35 |       | 0.25<br>0.35 | dB<br>dB |

| Transmit Gain Variation<br>with Programmed Gain | GXAG   | Measured transmit gain over the range<br>from maximum to minimum, calculated<br>deviation from the programmed gain rela-<br>tive to GXA at                                            |                |       |              |          |

|                                                 |        | $0 \text{ dB}, \text{V}_{\text{DD}} = 5 \text{ V}$                                                                                                                                    | -0.1           | —     | 0.1          | dB       |

## Transmission Characteristics (continued)

### Table 12. Transmission Characteristics (continued)

| Parameter                             | Symbol | Test Conditions                                                                       | Min             | Тур           | Max            | Unit     |

|---------------------------------------|--------|---------------------------------------------------------------------------------------|-----------------|---------------|----------------|----------|

| Transmit Gain Varia-                  | GXAF   | Relative to 1004 Hz, minimum                                                          |                 |               |                |          |

| tion with Frequency,                  |        | gain < GX < maximum gain, VFxI = 0 dBm0                                               |                 |               |                |          |

| $600 \Omega$ Resistive                |        | signal, path gain set to 0 dB:                                                        |                 |               |                |          |

| Source Impedance                      |        | f = 16.67 Hz                                                                          |                 | -50           | -30            | dB       |

| and Synthesized Ter-                  |        | f = 40 Hz                                                                             | —               | -40           | -26            | dB       |

| mination Impedance                    |        | f = 50 Hz                                                                             |                 | -40           | -30            | dB       |

|                                       |        | f = 60  Hz                                                                            | —               | -55           | -30            | dB       |

|                                       |        | f = 200 Hz                                                                            |                 | -3.5          | 0              | dB       |

|                                       |        | f = 300  Hz to  3000  Hz                                                              | -0.125<br>-0.57 | ±0.04<br>0.01 | 0.135          | dB<br>dD |

|                                       |        | f = 3140  Hz<br>f = 3380  Hz                                                          | -0.37<br>-0.735 | -0.01         | 0.125<br>0.015 | dB<br>dB |

|                                       |        | f = 3860  Hz<br>f = 3860 Hz                                                           | -0.733          | -0.03<br>-9.0 | -8.98          | dB<br>dB |

|                                       |        | f = 4600  Hz and above                                                                |                 | -9.0          | -32            | dB       |

| Transmit Gain Varia-                  | GXAL   | Sinusoidal test method*,                                                              |                 |               | 52             | uВ       |

| tion with Signal                      | UAAL   | reference level = $0 \text{ dBm0}$ :                                                  |                 |               |                |          |

| Level                                 |        | VFxI = -40  dBm0 to  +3  dBm0                                                         | -0.25           |               | 0.25           | dB       |

| Level                                 |        | VFxI = -50  dBm0 to  -40  dBm0                                                        | -0.50           |               | 0.50           | dB       |

|                                       |        | VFxI = -55  dBm0 to  -50  dBm0                                                        | -1.40           |               | 1.40           | dB       |

| Receive Gain Abso-                    | GRA    | Receive gain programmed to –6 dB, apply                                               |                 |               |                |          |

| lute Accuracy                         | ••••   | 0 dBm0 signal to DR, measure V <sub>RCV</sub> ,                                       |                 |               |                |          |

| , , , , , , , , , , , , , , , , , , , |        | $R_L = 100 \text{ k}\Omega$ differential:                                             |                 |               |                |          |

|                                       |        | 20 °C to 70 °C                                                                        | —               | ±0.15         | _              | dB       |

|                                       |        | 0 °C to 85 °C                                                                         | -0.25           | —             | 0.25           | dB       |

|                                       |        | <b>−40</b> °C to +85 °C                                                               | -0.30           | —             | 0.30           | dB       |

| Relative Gain,                        |        | Digital input 0 dBm0 signal,                                                          | -0.01           |               | 0.01           | dB       |

| VFrOP to VFrON                        |        | f = 300 Hz to 3400 Hz                                                                 |                 |               |                |          |

| Relative Phase,                       | _      | Digital input 0 dBm0 signal,                                                          | -0.25           | _             | 0.25           | Degrees  |

| VFrOP to VFrON                        |        | f = 300 Hz to 3400 Hz                                                                 |                 |               |                |          |

| Receive Gain Varia-                   | GRAG   | Measure receive gain over the range from                                              | -0.1            | _             | 0.1            | dB       |

| tion with Pro-                        |        | maximum to minimum setting, calculated                                                |                 |               |                |          |

| grammed Gain                          |        | deviation from the programmed gain relative                                           |                 |               |                |          |

|                                       |        | to GRA at 0 dB, $V_{DD}$ = 5 V                                                        |                 |               |                |          |

| Receive Gain Varia-                   | GRAF   | Relative to 1004 Hz, digital input =                                                  |                 |               |                |          |

| tion with Fre-                        |        | 0 dBm0 code, minimum gain < GR < maxi-                                                |                 |               |                |          |

| quency, $600 \ \Omega$                |        | mum gain, 0 dB path gain:                                                             |                 |               |                |          |

| Resistive Termination                 |        | f = below 3000 Hz                                                                     | -0.125          | ±0.04         | 0.125          | dB       |

|                                       |        | f = 3140 Hz                                                                           | -0.57           | ±0.04         | 0.125          | dB       |

|                                       |        | f = 3380 Hz                                                                           | -0.735          | -0.550        | 0.015          | dB       |

|                                       |        | f = 3860 Hz                                                                           |                 | -10.7         | -8.98          | dB       |

|                                       |        | f = 4600 Hz and above                                                                 |                 |               | -28            | dB       |

| Receive Gain Varia-                   | GRAL   | Sinusoidal test method*,                                                              |                 |               |                |          |

| tion with Signal                      |        | reference level = $0 \text{ dBm0}$ :                                                  | 0.25            |               | 0.25           | ЧD       |

| Level                                 |        | IPCM digital level = -40 dBm0 to +3 dBm0<br>IPCM digital level = -50 dBm0 to -40 dBm0 | -0.25<br>-0.50  | _             | 0.25<br>0.50   | dB<br>dB |

|                                       |        | IPCM digital level = $-50 \text{ dBm0 to } -40 \text{ dBm0}$                          | -0.50<br>-1.40  |               | 0.50<br>1.40   | dВ       |

|                                       |        |                                                                                       | -1.40           |               | 1.40           | uD       |

\* Applied to all four channels.

## **Noise Characteristics**

#### Table 13. Per-Channel Noise Characteristics

| Parameter                                                     | Symbol | Test Conditions                                                                                                                                                                                                                                     | Min      | Тур | Max               | Unit              |

|---------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-------------------|-------------------|

| Transmit Noise,<br>C-Message Weighted                         | Nxc    | 0 dB transmit gain*                                                                                                                                                                                                                                 | _        |     | 18                | dBrnC0            |

| Transmit Noise,<br>P-Message Weighted                         | Nxp    | 0 dB transmit gain*                                                                                                                                                                                                                                 | _        |     | -68               | dBm0p             |

| Receive Noise,<br>C-Message Weighted                          | Nrc    | 0 dB receive gain, digital pattern<br>corresponding to idle PCM code, μ-law                                                                                                                                                                         |          |     | 13                | dBrnC0            |

| Receive Noise,<br>P-Message Weighted                          | Nrp    | 0 dB receive gain, digital pattern<br>corresponding to idle PCM code, A-law                                                                                                                                                                         |          |     | -75               | dBm0p             |

| Noise, Single Frequency                                       | Nrs    | f = 0  kHz to  100  kHz, loop around<br>measurement, VVFxI = 0 Vrms                                                                                                                                                                                 | _        | _   | -53               | dBm0              |

| Power Supply Rejection,<br>Transmit                           | PSRx   | $V_{DD} = 5.0 V_{DC} + 100 \text{ mVrms}$<br>f = 0  kHz to  4  kHz<br>f = 4  kHz to  50  kHz<br>C-message weighted                                                                                                                                  | 36<br>30 |     |                   | dBC<br>dBC        |