#### 4-CH OVER-VOLTAGE PROTECTION FOR CC/DIFF PINS ON USB TYPE-C

#### **Description**

The DPO2039DABQ-13 provides 4 channels of over-voltage protection over the CC1/2 & DIFF1/2 pins which are connected to the USB Type-C connector. The 4 channels are divided into two pairs, one pair of channels protect the CC1 and CC2 pins from being shorted to the V<sub>BUS</sub>, one pair of channels protect the DIFF1 and DIFF2 pins from being shorted to the V<sub>BUS</sub>. Whenever the voltage threshold set for any of the two pairs of channels is reached, the exception condition becomes valid and the low-active flag FAULTB is subsequently asserted.

This device is designed to draw its operating voltage primarily from the system power, Vsys, which is either the always-ON 3.3/5V existed within the system or the 1-cell battery inside the mobile system. Under the circumstance when the battery inside a mobile system is fully depleted, DPO2039DABQ-13 can obtain power from the external peripheral system connected to the USB Type-C connector. The DPO2039DABQ-13 is housed in the low-profile and space-saving U-QFN3030-16 (Type B) package which is manufactured with environmental-friendly material.

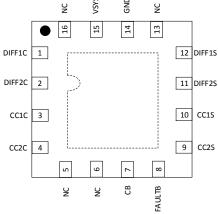

#### **Pin Assignments**

# (Top View)

U-QFN3030-16 (Type B)

#### **Features**

- Operating Voltage Range: 2.7V to 5.5V

- 4-Channel Over-Voltage Protection with Auto-Recovery

- IEC 61000-4-2 ESD Protection over CCxC and DIFFxC Pins

Process of OVE MOSEET for CC Rip Protection: 300mQ Typics

- RDS(ON) of OVP MOSFET for CC-Pin Protection:  $300m\Omega$  Typical

- R<sub>DS(ON)</sub> of OVP MOSFET for DIFF-Pin Protection: 5Ω Typical

- C<sub>IN</sub> of OVP MOSFET for CC-Pin Protection: 50pF

- C<sub>IN</sub> of OVP MOSFET for DIFF-Pin Protection: 5pF

- Built-In Over-Temperature Protection

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

- The DPO2039DABQ-13 is suitable for automotive applications requiring specific change control; this part is AEC-Q100 qualified, PPAP capable, and manufactured in IATF 16949 certified facilities.

https://www.diodes.com/quality/product-definitions/

#### **Applications**

- Notebook/Desktop/AIO PCs, Tablets, Mobile Phones

- VR/AR Headsets

- Docking Stations, Universal & Multimedia Hubs

- FPTVs, PC Monitors

- Set-Top-Boxes, Residential Gateways, Storage Devices

- Universal AC/DC Chargers/Adapters

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

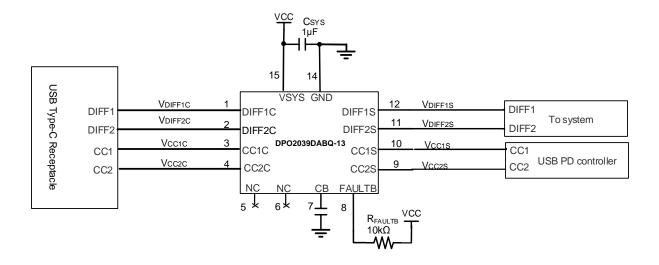

# **Typical Application Circuit**

**Figure 1. Typical Application Circuit**

# **Pin Descriptions**

| Pin Number   | Pin Name | Function                                                                                      |

|--------------|----------|-----------------------------------------------------------------------------------------------|

| 1            | DIFF1C   | DIFF1 connector side. This shall be connected to the DIFF1 pin of the USB Type-C connector.   |

| 2            | DIFF2C   | DIFF2 connector side. This shall be connected to the DIFF2 pin of the USB Type-C connector.   |

| 3            | CC1C     | CC1 connector side. This shall be connected to the CC1 pin of the USB Type-C connector.       |

| 4            | CC2C     | CC2 connector side. This shall be connected to the CC2 pin of the USB Type-C connector.       |

| 7            | СВ       | Pin for ESD support capacitor. Place a 0.1µF capacitor on this pin to ground.                 |

| 8            | FAULTB   | Fault status. This is an active-low open-drain output.                                        |

| 9            | CC2S     | CC2 system side. This shall be connected to the CC2 pin of the component to be protected.     |

| 10           | CC1S     | CC1 system side. This shall be connected to the CC1 pin of the component to be protected.     |

| 11           | DIFF2S   | DIFF2 system side. This shall be connected to the DIFF2 pin of the component to be protected. |

| 12           | DIFF1S   | DIFF1 system side. This shall be connected to the DIFF1 pin of the component to be protected. |

| 5, 6, 13, 16 | NC       | No connection.                                                                                |

| 14           | GND      | Ground.                                                                                       |

| 15           | VSYS     | Power Input. This shall be connected to the 2.7 to 5.5V power source inside the system.       |

| _            | EP       | Exposed pad. This shall be connected to ground.                                               |

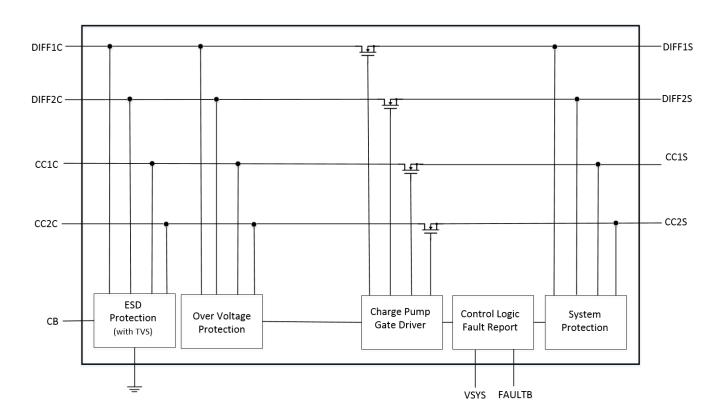

# **Functional Block Diagram**

Figure 2. Internal Functional Blocks

#### Absolute Maximum Ratings(@ T<sub>A</sub> = +25°C, unless otherwise specified) (Note 4)

| Symbol            | Parameter                                        | Rating       | Unit |

|-------------------|--------------------------------------------------|--------------|------|

| V <sub>VSYS</sub> | Voltage Range of VSYS Pin                        | -0.3 to 6.0  | V    |

| VFAULTB           | Voltage Range of FAULTB Pin                      | -0.3 to 6.0  | V    |

| VcB               | Voltage Range of CB Pin                          | -0.3 to 24   | V    |

| VDIFFXS, VCCXS    | Voltage Range of DIFF1S, DIFF2S, CC1S, CC2S Pins | -0.3 to 6.0  | V    |

| VDIFFXC, VCCXC    | Voltage Range of DIFF1C, DIFF2C, CC1C, CC2C Pins | -0.3 to 24.0 | V    |

| TJ                | Operating Junction Temperature                   | -40 to +150  | °C   |

| TL                | Lead Temperature                                 | +260         | °C   |

| T <sub>STG</sub>  | Storage Temperature                              | -65 to +150  | °C   |

| ESD               | Human Body Model (HBM), JESD22-A114              | ±2.0         | kV   |

|                   | Charge Device Model (CDM), JESD22-C101           | ±0.5         | K V  |

Note:

These are stress ratings only. Operation outside the absolute maximum ratings can cause device failure.

Operation at the absolute maximum rating for extended periods can reduce device reliability.

#### Package Thermal Data (@ T<sub>A</sub> = +25°C, unless otherwise specified) (Note 5)

| Symbol           | Parameter                               | Rating | Unit |

|------------------|-----------------------------------------|--------|------|

| PD               | Power Dissipation                       | 1.75   | W    |

| Reja             | Thermal Resistance, Junction-to-Ambient | 73     | °C/W |

| R <sub>θJC</sub> | Thermal Resistance, Junction-to-Case    | 12.7   | °C/W |

Note: 5. Device mounted on FR-4 substrate PC board, 2oz copper, with 1"  $\times$  1" copper pad layout.

# Recommended Operating Conditions (@ T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol           | Parameter                                                                    | Min | Max | Unit |

|------------------|------------------------------------------------------------------------------|-----|-----|------|

| Vvsys            | Input Supply Voltage at VSYS Pin                                             | 2.7 | 5.5 | V    |

| VFAULTB          | Power Rail for Pull-Up on FAULTB Pin                                         | 2.7 | 5.5 | V    |

| Vcв              | Voltage across CB Pin                                                        | 0   | 5.5 | V    |

| Vccxc, Vccxs     | I/O Voltage at CC1C, CC2C, CC1S, CC2S Pins                                   | 0   | 5.5 | V    |

| VDIFFXC, VDIFFXS | I/O Voltage at DIFF1C, DIFF2C, DIFF1S, DIFF2S Pins                           | 0   | 4.2 | V    |

| Ivccx            | Output Current Flowing into CCxS and out of CCxC, with Vccxs − Vccxc ≤ 250mV | _   | 600 | mA   |

#### Electrical Characteristics (@ TA = +25°C, Vvsys = 4.2V, unless otherwise specified.)

| Symbol                         | Parameter                                         | Test Conditions                                                                                                                                                              | Min  | Тур      | Max  | Unit |

|--------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------|------|

| CC OVP Switches                | •                                                 | •                                                                                                                                                                            |      |          |      |      |

|                                | On Designation of OO OVD FFT.                     | Vccxc = 5.5V, T <sub>A</sub> ≤ +85°C                                                                                                                                         | _    | 300      | 450  | mΩ   |

| R <sub>DS(ON)_</sub> cc        | On Resistance of CC OVP FETs                      | Vccxc = 5.5V, T <sub>A</sub> ≤ +105°C                                                                                                                                        | _    | 300      | 480  | mΩ   |

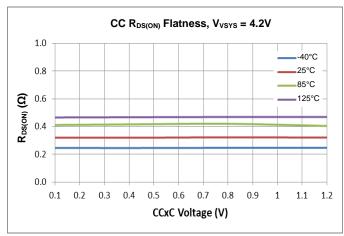

| Rds(onflat)_cc                 | On Resistance Flatness of CC OVP FETs             | Vccxc = 0.1 to 1.2V                                                                                                                                                          | _    | _        | 5    | mΩ   |

| Con_cc                         | Equivalent ON Capacitance                         | Capacitance from CCxC or CCxS to GND when device is powered, (Vccxc / Vccxs) = 0V to 1.2V                                                                                    | _    | 50       | _    | pF   |

| VTH_OVP_CCxC                   | OVP Threshold on CCxC Signal                      | _                                                                                                                                                                            | 5.6  | 6        | 6.25 | V    |

| VTH OVP HYS CCxC               | OVP Hysteresis on CCxC Signal                     | _                                                                                                                                                                            | _    | 140      | _    | mV   |

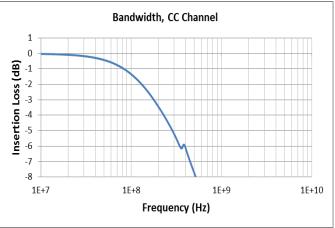

| BWon_cc<br>(Note 6)            | CC Line ON Bandwidth Single Ended (-3dB)          | Measured from CCxC to CCxS, $50\Omega$ system, $V_{CM} = 0.1V$ to $1.2V$                                                                                                     | _    | 200      | _    | MHz  |

| Vsht_ccxc_max<br>(Note 6)      | Short-to-VBUS Tolerance on the CCxC Pins          | Hot-plug CCxC with a 1 meter USB Type-C cable, place a 30Ω load on CCxS                                                                                                      | _    | _        | 24   | ٧    |

| VsHT_CCxs_CL<br>(Note 6)       | Short-to-VBUS Clamping Voltage on the CCxS Pins   | Hot-plug CCxC with a 1 meter USB Type-C cable, place a 30Ω load on CCxS. Hot plug voltage Vccxc = 24V                                                                        | _    | 7        | _    | V    |

| DIFF OVP Switches              |                                                   |                                                                                                                                                                              |      |          |      |      |

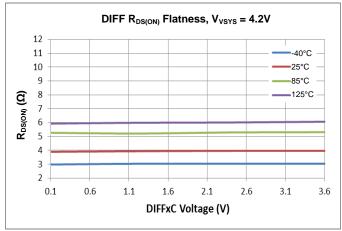

| D                              | On Resistance of DIFF OVP FETs                    | VDIFFxC = 3.6V, TA = +85°C                                                                                                                                                   | _    | 5        | _    | Ω    |

| R <sub>DS(ON)_DIFF</sub>       |                                                   | VDIFFxC = 3.6V, TA = +105°C                                                                                                                                                  | _    | 5        | _    | Ω    |

| RDS(ONFLAT)_DIFF               | On Resistance Flatness of DIFF OVP FETs           | $V_{DIFFxC} = 0.1 \text{ to } 3.6V$                                                                                                                                          | _    | _        | 1    | Ω    |

| C <sub>ON_DIFF</sub>           | Equivalent ON Capacitance                         | Capacitance from DIFFxC or<br>DIFFxS to GND when device is<br>powered. VDIFFxC / VDIFFxS = 0V to                                                                             | _    | 5        | _    | pF   |

|                                |                                                   | 3.6V                                                                                                                                                                         |      |          |      |      |

| VTH_OVP_DIFFxC                 | OVP Threshold on DIFFxC Signals                   | _                                                                                                                                                                            | 4.15 | 4.5      | 4.75 | V    |

| VTH_OVP_HYS_DIFFxC             | OVP Hysteresis on DIFFxC Signals                  | _                                                                                                                                                                            | _    | 110      | _    | mV   |

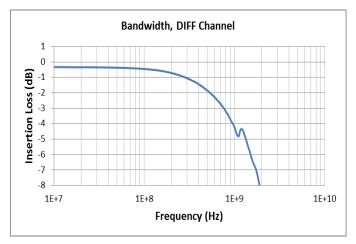

| BWon_diff<br>(Note 6)          | DIFF line ON Bandwidth Single Ended (-3dB)        | Measured from DIFFxC to DIFFxS, 50Ω system, V <sub>CM</sub> = 0.1V to 3.6V                                                                                                   | _    | 100<br>0 | _    | MHz  |

| Vshtbus_diffxc_max<br>(Note 6) | Short-to-VBUS Tolerance on the DIFFxC Pins        | Hot-plug DIFFxC with a 1 meter USB Type-C cable, place a 40Ω in series with 150nF to GND on DIFFxS pin                                                                       | _    | _        | 24   | V    |

| VshtBus_DIFFxs_cL<br>(Note 6)  | Short-to-VBUS Clamping Voltage on the DIFFxS Pins | Hot-plug DIFFxC with a 1 meter USB Type-C cable, place a 40Ω in series with 100nF to GND on DIFFxS pin. Hot plug voltage V <sub>DIFFxC</sub> = 24V, V <sub>VSYS</sub> = 3.3V | _    | 7        | _    | V    |

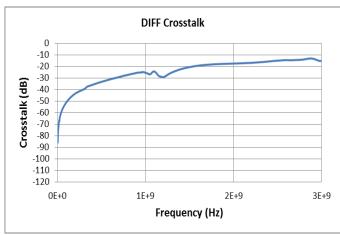

| XTALK_DIFFX<br>(Note 6)        | Crosstalk between DIFFx Lines                     | Measure crosstalk at f = 1MHz, from DIFF1S to DIFF2C or DIFF2 to DIFF1C. $V_{CM1} = 3.6V$ , $V_{CM2} = 0.3V$ , terminate open sides to $50\Omega$                            | _    | -80      | _    | dB   |

# Electrical Characteristics (@ T<sub>A</sub> = +25°C, V<sub>VSYS</sub> = 4.2V, unless otherwise specified) (continued)

| Symbol               | Parameter                                                                                                                                       | Test Conditions                                                                                                            | Min  | Тур  | Max  | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Power Supply and Lea | akage Current                                                                                                                                   |                                                                                                                            |      |      |      |      |

| Vuvlo                | Vvsys under Voltage Lockout                                                                                                                     | Vvsys steps up from 2V until CC or DIFF FETs turn ON                                                                       | 2.15 | 2.4  | 2.55 | V    |

| Vuvlo_Hsys           | Vvsys UVLO Hysteresis                                                                                                                           | Vvsys steps down from 2.5V until CC or DIFF FETs turn off. Measure difference between rising and falling UVLO to calculate | _    | 200  | _    | mV   |

| lvsys_on             | Vvsys Supply Current                                                                                                                            | _                                                                                                                          | _    | 190  | _    | μΑ   |

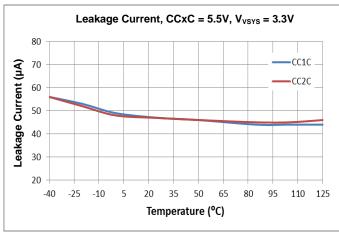

| ILEAK_CCxC           | Leakage current for CCxC when device is powered                                                                                                 | $V_{CCxC} = 3.6V$                                                                                                          | _    | _    | 30   | μΑ   |

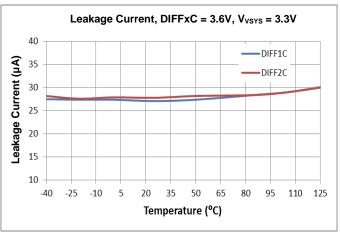

| ILEAK_DIFFxC         | Leakage current for DIFFxC when device is powered                                                                                               | VDIFFXC = 3.6V                                                                                                             | _    |      | 35   | μΑ   |

| ILEAK_CCxS           | Leakage current for CCxS when device is powered                                                                                                 | V <sub>CCx</sub> = 3.6V                                                                                                    | _    | _    | 30   | μΑ   |

| ILEAK_DIFFxS         | Leakage current for DIFFxS when device is powered                                                                                               | V <sub>DIFFx</sub> = 3.6V                                                                                                  | _    | _    | 35   | μΑ   |

| have over an a       | Leakage current into CCxC pins when                                                                                                             | Vvsys = 0V, Vccxc = 22V, Vccxs = 0V                                                                                        | _    |      | 150  | μΑ   |

| ILEAK_OVP_CCxC       | device is in OVP                                                                                                                                | Vvsys = 4.2V, Vccxc = 22V, Vccxs = 0V                                                                                      | _    | -    | 150  | μΑ   |

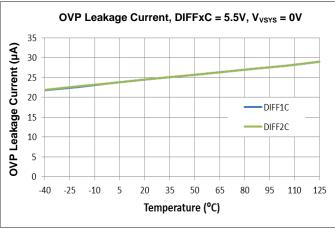

| L                    | Leakage current into DIFFxC pins when                                                                                                           | Vvsys = 0V, V <sub>DIFFxC</sub> = 22V, V <sub>DIFFxS</sub> = 0V                                                            | _    |      | 200  | μΑ   |

| ILEAK_OVP_DIFFxC     | device is in OVP                                                                                                                                | Vvsys = 4.2V, Vdiffxc = 22V, Vdiffxs = 0V                                                                                  | _    | _    | 200  | μΑ   |

| hear ove on o        | Leakage current out of CCxS pins when device is in OVP                                                                                          | Vvsys = 0V, Vccxc = 22V, Vccxs = 0V                                                                                        | _    | 1    | 1    | μΑ   |

| ILEAK_OVP_CCxS       |                                                                                                                                                 | Vvsys = 4.2V, Vccxc = 22V, Vccxs = 0V                                                                                      | _    | _    | 1    | μA   |

|                      | Leakage current out of DIFFxS pins when device is in OVP                                                                                        | VVSYS = 0V, VDIFFXC = 22V, VDIFFXS = 0V                                                                                    | _    | _    | 1    | μA   |

| ILEAK_OVP_DIFFxS     |                                                                                                                                                 | $V_{VSYS} = 4.2V$ , $V_{DIFFxC} = 22V$ , $V_{DIFFxS} = 0V$                                                                 | _    |      | 1    | μΑ   |

| FAULTB Pin           |                                                                                                                                                 |                                                                                                                            | •    |      |      | •    |

| VFAULTB              | Active-Low Output Voltage of FAULTB Pin                                                                                                         | I <sub>OL</sub> = 8mA                                                                                                      | _    | _    | 0.4  | V    |

| ILEAK_FAULB          | FAULTB Leakage Current                                                                                                                          | VFAULTB = 4.2V                                                                                                             | _    | _    | 1    | μΑ   |

| tfaultb_assertion    | FAULTB Assertion Time                                                                                                                           | _                                                                                                                          | _    | -    | 300  | μs   |

| tFAULTB_DEASSERTION  | FAULTB Deassertion Time                                                                                                                         | _                                                                                                                          | _    | 4    | _    | ms   |

| Timing Requirements  |                                                                                                                                                 |                                                                                                                            | •    |      | •    | •    |

| ton                  | Time from Crossing Rising Vvsys UVLO until CC/DIFF OVP FETs are on                                                                              | _                                                                                                                          | _    | _    | 2.5  | ms   |

| tovp_response_cc     | OVP Response Time on the CC Pins, Time from OVP Asserted until OVP FETs Turnoff                                                                 | _                                                                                                                          | _    | 100  | _    | ns   |

| tovp_response_diff   | OVP Response Time on the DIFF Pins,<br>Time from OVP Asserted until OVP FETs<br>Turnoff                                                         | _                                                                                                                          | _    | 100  | _    | ns   |

| tovp_response_cc_1   | OVP Recovery Time on the CC Pins. Once an OVP has occurred, the minimum duration until CC FETs turn back on if OVP has been removed already     | _                                                                                                                          | 26   | 32   | 38   | ms   |

| tovp_response_diff_1 | OVP Recovery Time on the DIFF Pins. Once an OVP has occurred, the minimum duration until DIFF FETs turn back on if OVP has been removed already | _                                                                                                                          | 26   | 32   | 38   | ms   |

| tovp_response_cc_2   | OVP Recovery Time on the CC Pins. Time from OVP removal until CC FETs turn back on, if device has been in OVP > 40ms                            | _                                                                                                                          | _    | 1    | _    | ms   |

| tovp_response_diff_2 | OVP Recovery Time on the DIFF Pins. Time from OVP removal until DIFF FETs turn back on, if device has been in OVP > 40ms                        | _                                                                                                                          | _    | 1    | _    | ms   |

| Thermal Shutdown an  |                                                                                                                                                 |                                                                                                                            | •    |      | •    | •    |

| T <sub>SHDN</sub>    | Thermal Shut Down Threshold                                                                                                                     | _                                                                                                                          | _    | +150 | _    | °C   |

|                      |                                                                                                                                                 |                                                                                                                            |      |      |      |      |

Note: 6. Guaranteed by bench characterization

#### Performance Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.)

Figure 3. DIFF RDS(ON) Flatness

Figure 4. CC RDS(ON) Flatness

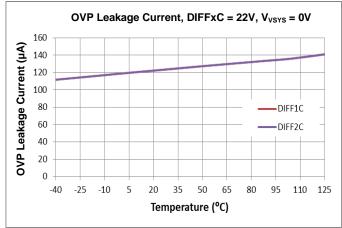

Figure 5. DIFFxC Leakage Current vs. Temperature

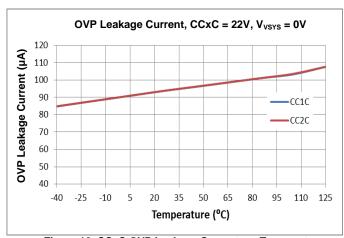

Figure 6. CCxC Leakage Current vs. Temperature

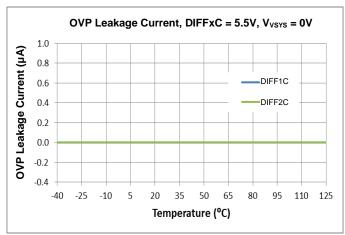

Figure 7. DIFFxC 5.5V OVP Leakage Current vs. Temperature

Figure 8. DIFFxC 22V OVP Leakage Current vs. Temperature

#### Performance Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.) (continued)

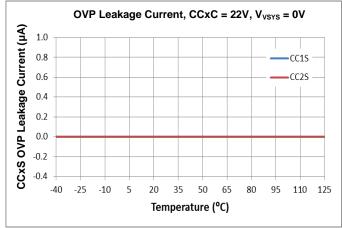

Figure 9. DIFFxC OVP Leakage Current vs. Temperature

Figure 10. CCxC OVP Leakage Current vs. Temperature

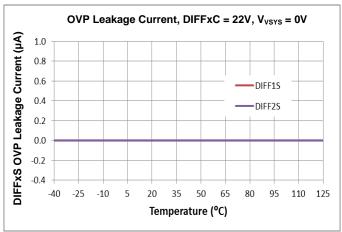

Figure 11. DIFFxS OVP Leakage Current vs Temperature

Figure 12. CCxS OVP Leakage Current vs Temperature

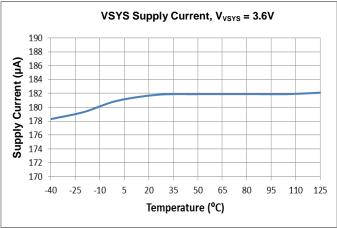

Figure 13. VSYS Supply Current vs Temperature

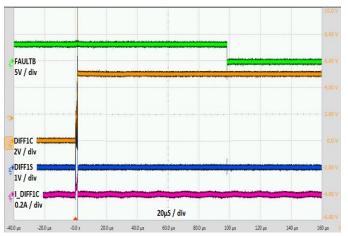

Figure 14. DIFF1C Short to 5V VBUS

#### Performance Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.) (continued)

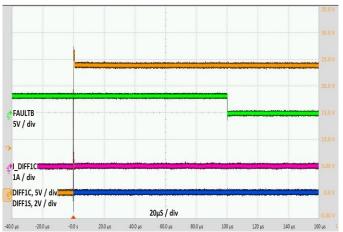

Figure 15. DIFF1C Short to 24V V<sub>BUS</sub>

Figure 16. CC1C Short to 24V VBUS

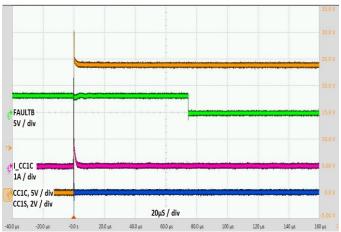

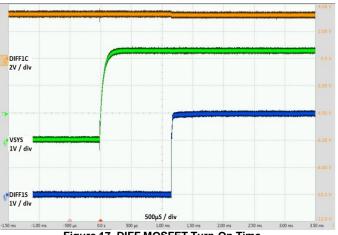

Figure 17. DIFF MOSFET Turn-On Time

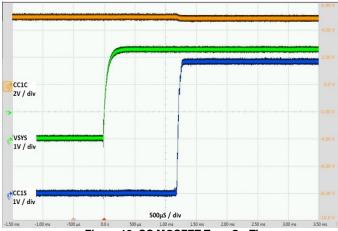

Figure 18. CC MOSFET Turn-On Time

Figure 19. DIFF Channel Bandwidth

Figure 20. CC Channel Bandwidth

#### Performance Characteristics (@ T<sub>A</sub> = +25°C, unless otherwise specified.) (continued)

Figure 21. DIFF Crosstalk

#### **Application Information**

#### **General Description**

The DPO2039DABQ-13 is a USB port protection device designed to work with USB Type-C connector, cable and USB PD to form a system that enables signal management and power delivery in a compact package. It provides short to VBUS protection for the CC and DIFF pins over the USB Type-C connector.

#### **Short to VBUS Protection**

The DPO2039DABQ-13 is a 4-channel uni-directional power switch with over-voltage protection. This is used to prevent the components inside a system which adopts the USB Type-C connector from being damaged by unexpected hazard. On the USB Type-C connector, the CC and DIFF pins are located in the close proximity of the VBUS pin. If ever the CC and/or the DIFF lines are short to the VBUS line either at the USB-C connector or at the cable end, the components (mostly ICs manufactured on the various sub-micron process nodes) behind the USB Type-C connector can easily be damaged by the resulting EOS. The damage, if occurred, is likely non-recoverable especially given that the voltage level on the VBUS line can go up to 20V or slightly higher. The DPO2039DABQ-13 integrates four series over-voltage FETs to protect the system side CC and DIFF lines. When either line on the Type-C connector side CC1C, CC2C, DIFF1C or DIFF2C is shorted to VBUS line, the DPO2039DABQ-13 will turn off the over-voltage FETs in less than 100ns window to isolate the system side CC and DIFF lines from the over-voltage connector side. When shorted to VBUS line is detected, the open-drain FAULTB will output low to indicate a fault condition.

#### **Signal Operation Range**

Table 1 and Table 2 show the signal operation range and output status:

| 0) / ( = 1   ) / ( 0 / ( = =       ) ) | 0V to 5.85V  | OFF                                 |

|----------------------------------------|--------------|-------------------------------------|

| 0V to UVLO (Invalid)                   | 5.85V to 20V | OFF                                 |

|                                        | 0V to 5.85V  | ON                                  |

| 2.7V to 5.5V (Valid)                   | 5.85V to 20V | OFF: FAULTB Asserted (OVP detected) |

Table 1. Signal Operation Range for CCx

| 0)/ to 11)/1 0 (loverlie) | 0V to 4.35V  | OFF                                 |

|---------------------------|--------------|-------------------------------------|

| 0V to UVLO (Invalid)      | 4.35V to 20V | OFF                                 |

| 0.71/1- 5.51/0/-1/-1      | 0V to 4.35V  | ON                                  |

| 2.7V to 5.5V (Valid)      | 4.35V to 20V | OFF: FAULTB Asserted (OVP detected) |

Table 2. Signal Operation Range for DIFFx

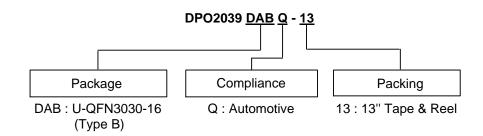

#### Ordering Information (Note 7)

| Part Number    | Marking ID | Reel Size (inches) | Tape Width (mm)    | 13" Tape and Reel |                    |  |

|----------------|------------|--------------------|--------------------|-------------------|--------------------|--|

| Fait Number    | Marking ID |                    | rape widin (iliin) | Quantity          | Part Number Suffix |  |

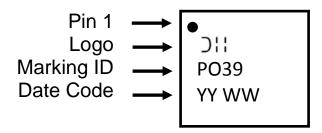

| DPO2039DABQ-13 | PO39       | 13                 | 8                  | 3,000/Tape & Reel | -13                |  |

Note: 7. For packaging details, go to our website at https://www.diodes.com/design/support/packaging/diodes-packaging/.

# **Marking Information**

YY: Year

WW: Week 01 to 53

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

# Side View D (Pin #1 ID) E (Pin #1 ID) L (16x) Z (8x)

**Bottom View**

#### U-QFN3030-16 (Type B)

| U-QFN3030-16         |      |      |       |  |  |

|----------------------|------|------|-------|--|--|

| Type B               |      |      |       |  |  |

| Dim                  | Min  | Max  | Тур   |  |  |

| Α                    | 0.55 | 0.65 | 0.60  |  |  |

| A1                   | 0    | 0.05 | 0.02  |  |  |

| A3                   | -    | -    | 0.15  |  |  |

| b                    | 0.18 | 0.28 | 0.23  |  |  |

| D                    | 2.95 | 3.05 | 3.00  |  |  |

| D2                   | 1.40 | 1.60 | 1.50  |  |  |

| Е                    | 2.95 | 3.05 | 3.00  |  |  |

| E2                   | 1.40 | 1.60 | 1.50  |  |  |

| е                    | -    | -    | 0.50  |  |  |

| L                    | 0.35 | 0.45 | 0.40  |  |  |

| Z                    | -    | -    | 0.625 |  |  |

| All Dimensions in mm |      |      |       |  |  |

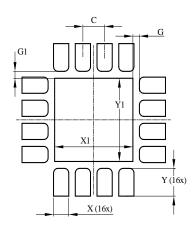

### **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

#### U-QFN3030-16 (Type B)

| Dimensions    | Value   |

|---------------|---------|

| Dillielisions | (in mm) |

| С             | 0.500   |

| G             | 0.150   |

| G1            | 0.150   |

| Х             | 0.350   |

| X1            | 1.800   |

| Y             | 0.600   |

| Y1            | 1.800   |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2019, Diodes Incorporated

www.diodes.com