## 74F525 Programmable Counter

## **General Description**

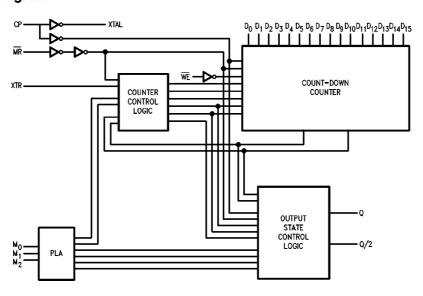

The 'F525 is a multi-function 28-pin device. It consists of a 16-bit count-down counter, logic to control the counter, logic to control the state of the outputs and a PLA to decode the particular function selected by the user. The list of high-speed timing applications include:

## **Features**

- Baud rate generator

- Digitally programmed monostable

- Variable system frequency generator

- Digital filter variable sampling rate

- 16-bit data path

- External trigger

- Extremely accurate one shot w/pulse widths from 50 ns to 3.27 ms @CP = 40 MHz

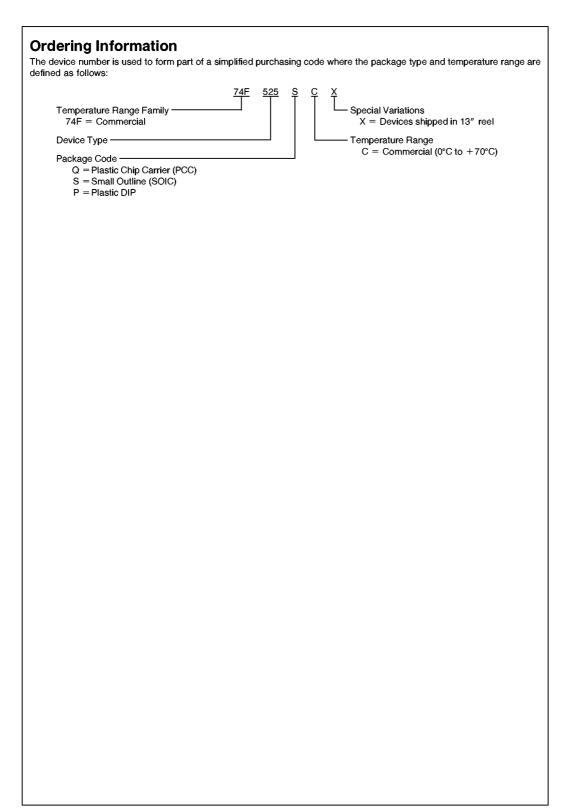

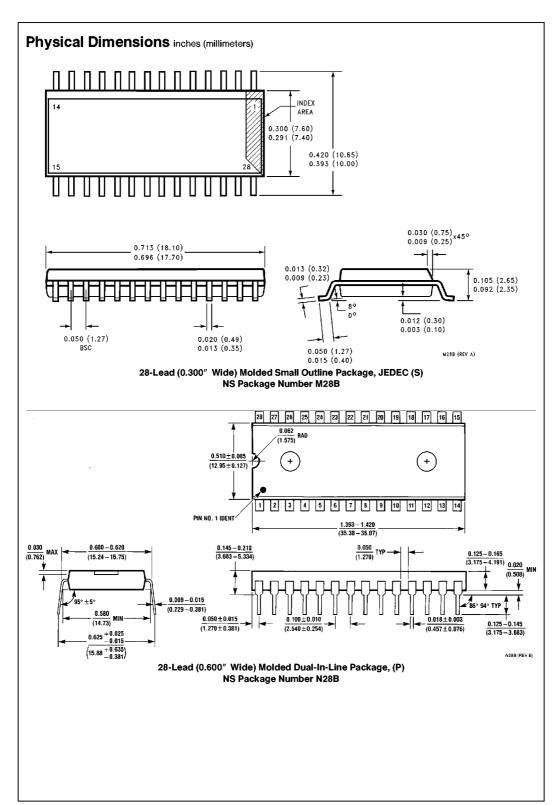

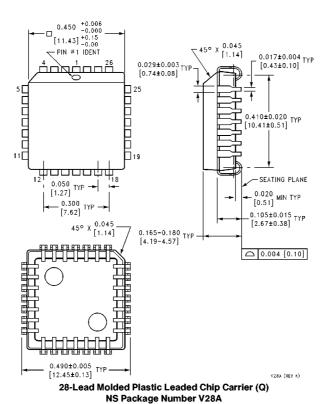

| Commercial        | Package<br>Number | Package Description                               |

|-------------------|-------------------|---------------------------------------------------|

| 74F525QC (Note 1) | V28A              | 28-Lead Molded Plastic Leaded Chip Carrier        |

| 74F525SC (Note 1) | M28B              | 28-Lead (0.300" Wide) Molded Small Outline, JEDEC |

| 74F525PC          | N28B              | 28-Lead (0.600" Wide) Molded Dual-In-Line Package |

Note 1: Devices also available in 13" reel. Use suffix = SCX and QCX.

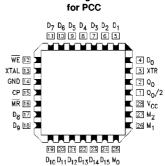

## **Connection Diagrams**

Pin Assignment

TL/F/9547-3

TRI-STATE® is a registered trademark of National Semiconductor Corporation

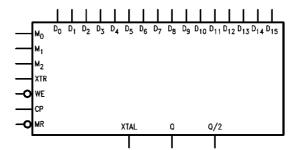

## **Logic Symbol**

TL/F/9547-1

## **Unit Loading/Fan Out**

|                                 |                                 | 74F              |                                                                                   |  |  |

|---------------------------------|---------------------------------|------------------|-----------------------------------------------------------------------------------|--|--|

| Pin Names                       | Description                     | U.L.<br>HIGH/LOW | Input I <sub>IH</sub> /I <sub>IL</sub><br>Output I <sub>OH</sub> /I <sub>OL</sub> |  |  |

| Q                               | Ouput (Primarily indicates when | 50/33.3          | -1 mA/20 mA                                                                       |  |  |

|                                 | the counter has reached zero)   |                  |                                                                                   |  |  |

| Q/2                             | Output (Divides Q by 2)         | 50/33.3          | -1 mA/20 mA                                                                       |  |  |

| M <sub>0</sub> -M <sub>2</sub>  | Status Inputs                   | 1.0/1.0          | 20 μA/ - 0.6 mA                                                                   |  |  |

| MR                              | Master Reset                    | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |  |  |

| CP                              | Clock Pulse                     | 1.0/2.0          | 20 μA/ – 1.2 mA                                                                   |  |  |

| D <sub>0</sub> -D <sub>15</sub> | Data Inputs                     | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |  |  |

| WE                              | Write Enable Input              | 1.0/1.0          | 20 μA/ - 0.6 mA                                                                   |  |  |

| XTR                             | External Trigger Input          | 1.0/2.0          | 20 μA/ – 1.2 mA                                                                   |  |  |

| XTAL                            | Crystal Output                  | 1.0/1.0          | 20 μA/ – 0.6 mA                                                                   |  |  |

## **Functional Description**

The multi-function aspect of the device consists of eight different modes of operation. An explanation of the operation of the device in each of the modes follows. However, there is one operation that is independent of the selected mode: the loading of data. Data is latched into a set of data latches when  $\overline{WE}$  is brought from a LOW to a HIGH state. The latches are transparent when  $\overline{WE}$  is held LOW.

### **Operation Notes:**

- 1. Device should be reset before operation.

- 2. The XTR input acts as a select line for the clock.

- 3. With XTR low, the clock goes into the counter.

- 4. With XTR high, the clock loads the counter.

- 5. In mode 4 and 5, during counting, the counter cannot be reloaded. XTR high freezes the count.

- 6. Mode 7 is the only auto-reload mode, all other modes require and XTR pulse to begin.

- 7. Loading 0 into the latches idles the device.

### MODE 0: Interval Timer with Level Output

While XTR is HIGH, the data in the data latches is loaded into the counter upon the next positive edge of CP. The negative edge of XTR enables the count-down to begin with the next positive edge of CP. When the count reaches zero,

Q, normally LOW, is brought HIGH and Q/2 toggles state. Taking XTR HIGH at any time enables the data in the data latches to be loaded into the counter on the rising edge of CP and clears Q. See  $\it Figure~1$ .

### **MODE 1: Interval Timer with Inverted Level Output**

The operation is exactly the same as in Mode 0 except that Q is normally HIGH and goes LOW when the count reaches zero. Q/2 toggles on the negative-edge of Q. See Figure 1.

### **MODE 2: Interval Timer with Pulse Output**

While XTR is HIGH, the data in the data latches is loaded into the counter upon the next positive edge of CP. The negative edge of XTR enables the count-down to begin with the next positive edge of CP. When the count reaches zero, Q, normally LOW, is brought HIGH for a single period of CP. Q/2 toggles state on the positive edge of Q. Taking XTR HIGH at any time causes the data in the data latches to be loaded into the counter on the rising edge of CP and clears Q. See Figure 2.

### **MODE 3: Interval Timer with Inverted Pulse Output**

The operation is exactly the same as in Mode 2 except that Q is normally HIGH and goes LOW for a single period of CP. Q/2 toggles on the negative edge of Q. See *Figure 2*.

## Functional Description (Continued)

**Function Table**

| M <sub>2</sub> | M <sub>1</sub> | M <sub>O</sub> | Function |

|----------------|----------------|----------------|----------|

| 0              | 0              | 0              | Mode 0   |

| 0              | 0              | 1              | Mode 1   |

| 0              | 1              | 0              | Mode 2   |

| 0              | 1              | 1              | Mode 3   |

| 1              | 0              | 0              | Mode 4   |

| 1              | 0              | 1              | Mode 5   |

| 1              | 1              | 0              | Mode 6   |

| 1              | 1              | 1              | Mode 7   |

### MODE 4: Interval Timer, Pulse Output with Count Hold

While XTR is HIGH, the data in the data latches is loaded into the counter upon the next positive edge of CP. The negative edge of XTR enables the count-down to begin with the next positive edge of CP. When the count reaches zero, Q, normally low, is brought HIGH for a single period of CP. Q/2 toggles state on the positive edge of Q. Taking XTR HIGH before the counters reach zero, stops the count-down from the point where it was held. Data cannot be reloaded into the counter until a count of zero is reached. See *Figure* 3

## MODE 5: Interval Timer, Inverted Pulse Output with Count Hold

The operation is exactly the same as Mode 4 except that Q is normally HIGH and goes LOW for a single period of CP. Q/2 toggles on the negative-edge of Q. See Figure 3.

### MODE 6: Retriggerable Synchronous One-Shot

When XTR is HIGH, the data in the data latches is loaded into the counter upon the positive edge of CP. The negative edge of XTR enables the count-down to begin with the next positive edge of CP, wehre Q, normally LOW, is then brought HIGH and the counter is decremented when the count reaches zero, Q is brought LOW, and Q/2 is toggled. Bringing XTR HIGH during the count-down will allow the data in the data latches to be loaded into the counter with the next positive edge of CP, but will not affect Q. See Figure 4. NOTE that the pulse width of Q will be N-1 clock cycles, where N is the number loaded into the counter. N=1 should not be used as this may cause unpredictable results.

### **MODE 7: Frequency Generator**

When XTR is HIGH, the data in the data latches is loaded into the counter upon the positive edge of CP. The negative edge of XTR enables the count-down to begin with the next positive edge of CP. When the count reaches zero, Q, normally LOW, is brought HIGH for a single period of CP and Q/2 is toggled. The same clock edge that brings Q HIGH, also loads the data in the data latches into the counter. The counter will start to count on the next positive edge of CP. This mode will run continuously after an initial XTR until stopped by MR. Taking XTR HIGH at any time causes the data in the data latches to be loaded into the counter and Q output to be cleared with the next positive edge of CP. See Figure 5.

### **Block Diagram**

TL/F/9547-4

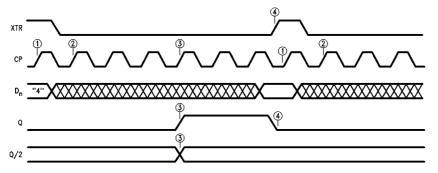

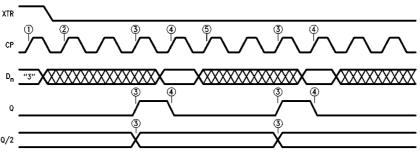

## **Timing Diagrams**

TL/F/9547-5

$\Phi\mbox{With XTR HIGH, the rising edge of CP loads data from the latches to the counter.}$

- With XTR LOW, the rising edge of CP begins count-down cycle.

- When the count reaches zero, Q goes HIGH, and Q/2 toggles state.

- ⊕ The next occurrence of XTR clears Q.

FIGURE 1. MODE 0 and MODE 1 (Inverse Output of Mode 0)  $\overline{M}_{n} = 000,001$

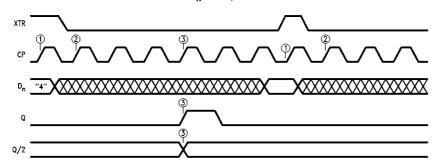

TL/F/9547-6

$\Phi\mbox{With XTR HIGH, the rising edge of CP loads data from the latches to the counter.}$

®With XTR LOW, the rising edge of CP begins the count-down cycle.

When the count reaches zero, Q goes HIGH for one period of CP, and Q/2 toggles state.

### FIGURE 2. MODE 2 and MODE 3 (Inverse Output of Mode 2) $\overline{M}_n = 010,011$

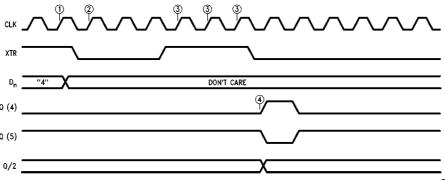

TL/F/9547-7

FIGURE 3. MODE 4 and MODE 5

$\overline{M}_n = 100, 101$

①With XTR HIGH, the rising edge of CP loads data from the latches into the counter.

②With XTR LOW, the rising edge of CP begins the count-down.

With XTR HIGH, during count-down, the rising edge of CP does nothing.

•When the count reaches zero, Q goes HIGH for one clock cycle and Q/2 toggles state.

Note: Once the count reaches zero, the counter can be reloaded with XTR HIGH.

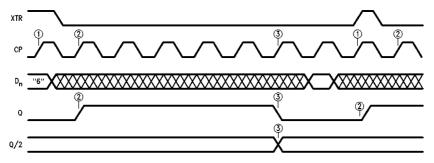

## Timing Diagrams (Continued)

FIGURE 4. MODE 6

$\overline{M}_n = 110$

①With XTR HIGH, the rising edge of CP loads data from the latches to the counter.

®With XTR LOW, the rising edge of CP begins the count, and Q goes HIGH.

When the count reaches zero, Q goes LOW, and Q/2 toggles state. Bringing XTR HIGH before count reaches zero will reload the counter, but not affect Q.

Loading N=0 halts counter; loading N=1 will result in undefined operation.

Pulse width = (2/CP) \* (N-1)

TL/F/9547-9

TL/F/9547-8

FIGURE 5. MODE 7  $\overline{M}_n = 111$

⊕With XTR HIGH, the rising edge of CP, loads data from the latches to the counter.

②On the falling edge of XTR, the rising edge of CP begins count-down.

When count reaches zero, Q goes HIGH for one period of CP, and Q/2 toggles on the Q rising edge.

①On the rising edge of CP on which Q goes LOW, the counters are reloaded.

©Count-down begins again.

## **Absolute Maximum Ratings** (Note 1)

Storage Temperature  $-65^{\circ}\text{C}$  to  $+150^{\circ}\text{C}$ -55°C to +125°C Ambient Temperature under Bias -55°C to +175°C Junction Temperature under Bias Plastic -55°C to +150°C

$V_{\mbox{\footnotesize CC}}$  Pin Potential to

Ground Pin

-0.5V to +7.0VInput Voltage (Note 2) -0.5V to +7.0VInput Current (Note 2)  $-30\,\mathrm{mA}$  to  $+5.0\,\mathrm{mA}$

Voltage Applied to Output

in HIGH State (with  $V_{CC} = 0V$ )

$\begin{array}{c} -0.5 \text{V to V}_{CC} \\ -0.5 \text{V to } +5.5 \text{V} \end{array}$ Standard Output TRI-STATE® Output

Current Applied to Output

in LOW State (Max) twice the rated IOL (mA)

Note 1: Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

## **Recommended Operating Conditions**

Free Air Ambient Temperature

0°C to +70°C Commercial

Supply Voltage Commercial

+4.5V to +5.5V

### **DC Electrical Characteristics**

| Symbol           | Parameter                            |                                                   | 74F        |     |              | Units | v <sub>cc</sub> | Conditions                                                |  |

|------------------|--------------------------------------|---------------------------------------------------|------------|-----|--------------|-------|-----------------|-----------------------------------------------------------|--|

| Symbol           |                                      |                                                   | Min        | Тур | Max          | Units | ▼CC             | Conditions                                                |  |

| V <sub>IH</sub>  | Input HIGH Voltage                   |                                                   | 2.0        |     |              | V     |                 | Recognized as a HIGH Signal                               |  |

| $V_{IL}$         | Input LOW Voltage                    |                                                   |            |     | 0.8          | V     |                 | Recognized as a LOW Signal                                |  |

| $V_{CD}$         | Input Clamp Diode Vo                 | oltage                                            |            |     | -1.2         | V     | Min             | $I_{IN} = -18 \text{ mA}$                                 |  |

| V <sub>OH</sub>  | Output HIGH<br>Voltage               | 74F 10% V <sub>CC</sub><br>74F 5% V <sub>CC</sub> | 2.5<br>2.7 |     |              | V     | Min             | $I_{OH} = -1 \text{ mA}$<br>$I_{OH} = -1 \text{ mA}$      |  |

| V <sub>OL</sub>  | Output LOW<br>Voltage                | 74F 10% V <sub>CC</sub>                           |            |     | 0.5          | ٧     | Min             | I <sub>OL</sub> = 20 mA                                   |  |

| l <sub>IH</sub>  | Input HIGH<br>Current                | 74F                                               |            |     | 5.0          | μΑ    | Max             | $V_{IN} = 2.7V$                                           |  |

| I <sub>BVI</sub> | Input HIGH Current<br>Breakdown Test | 74F                                               |            |     | 7.0          | μΑ    | Max             | V <sub>IN</sub> = 7.0V                                    |  |

| I <sub>CEX</sub> | Output HIGH<br>Leakage Current       | 74F                                               |            |     | 50           | μΑ    | Max             | V <sub>OUT</sub> = V <sub>CC</sub>                        |  |

| V <sub>ID</sub>  | Input Leakage<br>Test                | 74F                                               | 4.75       |     |              | ٧     | 0.0             | $I_{\text{ID}} = 1.9 \mu\text{A}$ All Other Pins Grounded |  |

| lop              | Output Leakage<br>Circuit Current    | 74F                                               |            |     | 3.75         | μΑ    | 0.0             | V <sub>IOD</sub> = 150 mV<br>All Other Pins Grounded      |  |

| l <sub>IL</sub>  | Input LOW Current                    |                                                   |            |     | -0.6<br>-1.2 | mA    | Max             | $V_{IN} = 0.5V (D0-D15)$<br>$V_{IN} = 0.5V (CP, XTR)$     |  |

| los              | Output Short-Circuit (               | Current                                           | -60        |     | <b>- 150</b> | mA    | Max             | V <sub>OUT</sub> = 0V                                     |  |

| Іссн             | Power Supply Curren                  | t                                                 |            | 106 | 160          | mA    | Max             | V <sub>O</sub> = HIGH                                     |  |

| ICCL             | Power Supply Curren                  | t                                                 |            | 106 | 160          | mA    | Max             | $V_O = LOW$                                               |  |

| AC Elec                              | ctrical Characteristic                   | s            |                                                            |              |                                                                    |              |       |

|--------------------------------------|------------------------------------------|--------------|------------------------------------------------------------|--------------|--------------------------------------------------------------------|--------------|-------|

|                                      |                                          |              | 74F                                                        |              | 74F  T <sub>A</sub> , V <sub>CC</sub> = Com C <sub>L</sub> = 50 pF |              | Units |

| Symbol                               | Parameter                                |              | $T_A = +25^{\circ}C$ $V_{CC} = +5.0$ $C_L = 50 \text{ pF}$ |              |                                                                    |              |       |

|                                      |                                          | Min          | Тур                                                        | Max          | Min                                                                | Max          |       |

| f <sub>max</sub>                     | Maximum Clock Frequency                  | 50           | 60                                                         |              | 40                                                                 |              | MHz   |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>CP to Q             | 9.0<br>8.0   | 16.0<br>12.0                                               | 20.5<br>15.5 | 8.0<br>7.0                                                         | 22.5<br>17.5 | ns    |

| t <sub>PLH</sub>                     | Propagation Delay<br>CP to Q/2           | 9.0<br>10.0  | 15.5<br>15.5                                               | 20.0<br>20.0 | 8.0<br>9.0                                                         | 22.0<br>22.0 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>XTR to Q            | 8.5<br>6.0   | 12.0<br>10.5                                               | 15.5<br>13.5 | 7.5<br>5.0                                                         | 17.5<br>15.0 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay MR to Q                | 11.5<br>9.0  | 16.5<br>12.5                                               | 21.0<br>16.0 | 10.5<br>8.0                                                        | 23.0<br>18.0 | ns    |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay MRto Q/2               | 8.0<br>7.0   | 14.0<br>10.5                                               | 17.5<br>13.5 | 7.0<br>6.0                                                         | 19.5<br>15.0 | ns    |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>M <sub>n</sub> to Q | 10.0<br>10.5 | 15.0<br>17.0                                               | 19.0<br>21.5 | 9.0<br>9.5                                                         | 21.0<br>23.5 | ns    |

# **AC Operating Requirements**

|                                          |                                                 | 74           | 4F               | 74                                     | Units |    |

|------------------------------------------|-------------------------------------------------|--------------|------------------|----------------------------------------|-------|----|

| Symbol                                   | Parameter                                       |              | + 25°C<br>+ 5.0V | T <sub>A</sub> , V <sub>CC</sub> = Com |       |    |

|                                          |                                                 | Min          | Max              | Min                                    | Max   | ]  |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup Time, HIGH or LOW<br>D <sub>n</sub> to WE | 2.0<br>4.0   |                  | 2.5<br>4.5                             |       | ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>D <sub>n</sub> to WE  | 0<br>2.0     |                  | 0<br>2.5                               |       | ns |

| t <sub>s</sub> (H)<br>t <sub>s</sub> (L) | Setup Time, HIGH or LOW<br>D <sub>n</sub> to CP | 9.0<br>10.5  |                  | 10.0<br>12.0                           |       | ns |

| t <sub>h</sub> (H)<br>t <sub>h</sub> (L) | Hold Time, HIGH or LOW<br>D <sub>n</sub> to CP  | 0            |                  | 0<br>0                                 |       | ns |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup Time, HIGH or LOW<br>XTR to CP            | 7.0<br>8.0   |                  | 8.0<br>9.0                             |       | ns |

| t <sub>h</sub> (H)                       | Hold Time, HIGH or LOW<br>XTR to CP             | 0            |                  | 0                                      |       | ns |

| t <sub>S</sub> (H)<br>t <sub>S</sub> (L) | Setup Time, HIGH or LOW<br>Mode to CP           | 33.5<br>33.5 |                  | 35.5<br>35.5                           |       | ns |

| t <sub>w</sub> (H)                       | XTR Pulse Width, HIGH                           | 11.5         |                  | 13.0                                   |       | ns |

| t <sub>w</sub> (L)                       | MR Pulse Width, LOW                             | 7.0          |                  | 8.0                                    |       | ns |

| t <sub>w</sub> (L)                       | WE Pulse Width, LOW                             | 4.5          |                  | 5.0                                    |       | ns |

| t <sub>w</sub> (H)<br>t <sub>w</sub> (L) | CP Pulse Width<br>HIGH or LOW                   | 3.5<br>9.5   |                  | 4.0<br>10.5                            |       | ns |

| t <sub>rec</sub>                         | Recovery Time<br>MR to CP                       | 5.0          |                  | 6.0                                    |       | ns |

| t <sub>rec</sub>                         | Recovery Time<br>Mode to CP                     | 30.0         |                  | 32.0                                   |       | ns |

## Physical Dimensions inches (millimeters) (Continued)

LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

National Semiconductor

Fax: (+49) 0-180-530 85 86 Email: cniyage etevm2.nsc.com Deutsch Tel: (+49) 0-180-539 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 35 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408